初步的 信息

mt8910-1

9-11

这 重置 状态 组成 的 二 substates, 这

receive 重置 状态 和 全部 重置 状态. 这 全部 重置

状态 是 entered 下列的 一个 电源-向上 或者 之后 这

expiry 的 这 receive 重置计时器 (40 ms). 这

receive 重置 状态 是 一个 瞬时 状态 这个 是

entered once 这 dslic 有 发现 一个 丧失 的

received 信号 当 这 transceiver 是 不

transmitting. 在 这个 状态, 这 transceiver 将 不

initiate 这 开始-向上 sequence 但是 是 有能力 的

responding 至 这 适合的 触发 声调. 当

这 计时器 在 这 receive 重置 状态 有 安排时间 输出 (40

ms), 这 transceiver enters 这 全部 重置 状态.

所有 计时器 surrounding 这 重置 states 是 包含

在 这 dslic 和 有 被 设置 作 每 这 ansi-

t1.601-1988:

• 失败 至 完全 一个 开始-向上 sequence

计时器 是 设置 在 15 秒.

• 丧失 的 received 信号 计时器 是 设置 在

480 ms 作 是 这 丧失 的

同步.

• 这 receive 重置 状态 计时器 是 设置 至

40 ms.

• 一个 fourth 计时器 (不 指定 在 ansi

t1.601-1988) 有 被 包含 这个

将 restrict 这 时间 至 520 ms 为 一个

deactivation sequence.

这 dslic 将 enter 一个 deactivated 状态 在 这

assertion 的 一个 deactivation 要求 (设置 这 开始/

停止 位 至 0 在 控制 寄存器 1, 和 这

subsequent 丧失 的 这 received 信号). once 这

deactivation 处理 有 被 完成, 这

要求 为 触发 能 follow 一个 warm 开始

处理 作 定义 在 ansi t1.601-1988.

循环 效能

这 mt8910-1 运作 在 一个 数字的 subscriber 线条

(dsl) 这个 是 一个 二 线 twisted 一双 metallic

中等 典型地 使用 为 传递 在 这

central 办公室 (lt) 和 这 客户 premise

设备 (更多 commonly 涉及 至 作 "基本

进入 接口 在 这 网络 一侧 的 这 nt").

这 mt8910-1 是 生产 测试 为 错误 自由

效能 为 2.5 秒 (20,000 st-总线) frames

在 一个 4.6km (15 kft) 26 awg simulated 循环

(相等的 至 40db attenuation @ 40 khz).

st-总线 接口

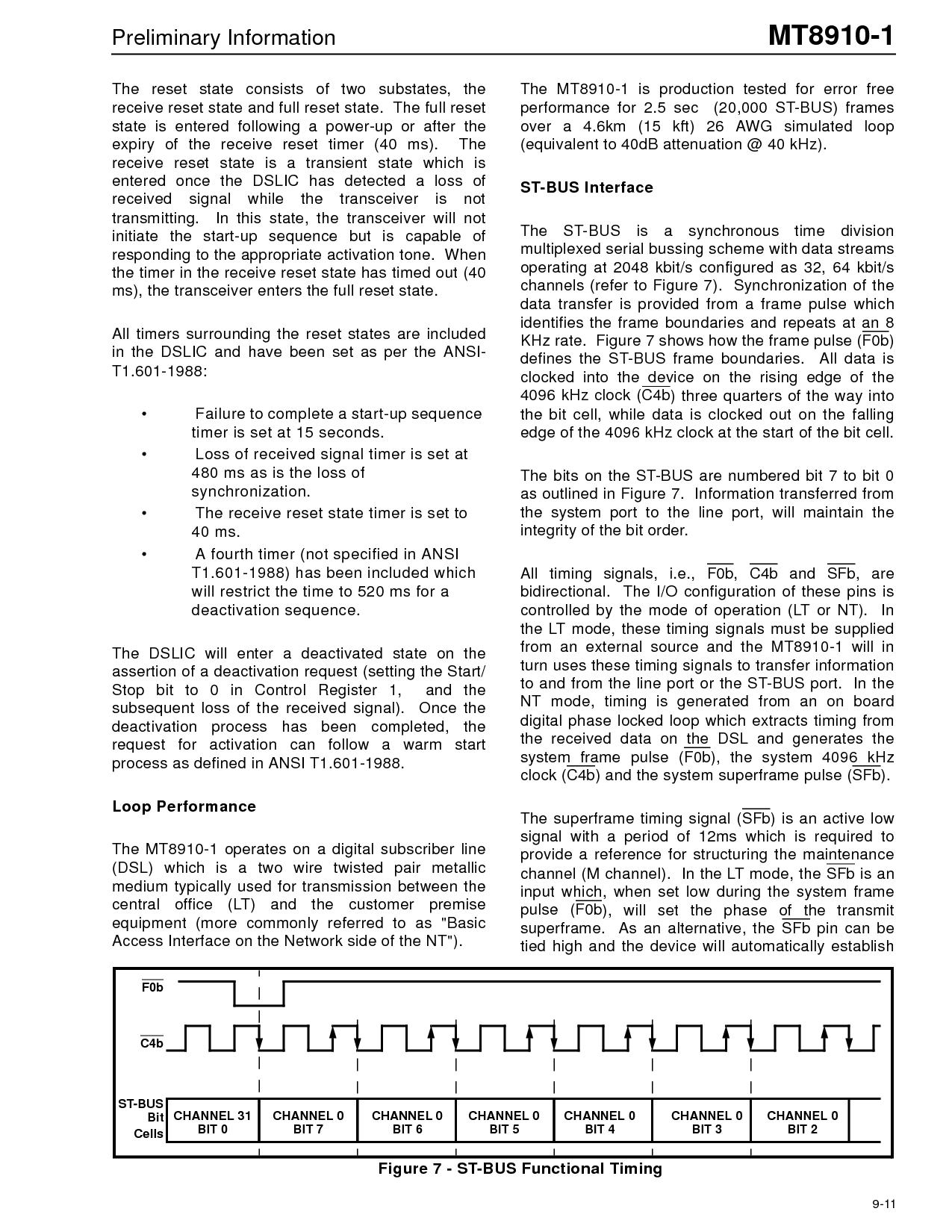

这 st-总线 是 一个 同步的 时间 分隔

多路复用 串行 bussing scheme 和 数据 streams

运行 在 2048 kbit/s 配置 作 32, 64 kbit/s

途径 (谈及 至 图示 7). 同步 的 这

数据 转移 是 提供 从 一个 框架 脉冲波 这个

identifies 这 框架 boundaries 和 repeats 在 一个 8

khz 比率. 图示 7 显示 如何 这 框架 脉冲波 (f0b

)

定义 这 st-总线 框架 boundaries. 所有 数据 是

clocked 在 这 设备 在 这 rising 边缘 的 这

4096 khz 时钟 (c4b

) 三 quarters 的 这 方法 在

这 位 cell, 当 数据 是 clocked 输出 在 这 下落

边缘 的 这 4096 khz 时钟 在 这 开始 的 这 位 cell.

这 位 在 这 st-总线 是 numbered 位 7 至 位 0

作 概述 在 图示 7. 信息 transferred 从

这 系统 端口 至 这 线条 端口, 将 维持 这

integrity 的 这 位 顺序.

所有 定时 信号, i.e., f0b

, c4b和 sfb, 是

双向的. 这 i/o 配置 的 这些 管脚 是

控制 用 这 模式 的 运作 (lt 或者 nt). 在

这 lt 模式, 这些 定时 信号 必须 是 有提供的

从 一个 外部 源 和 这 mt8910-1 将 在

转变 使用 这些 定时 信号 至 转移 信息

至 和 从 这 线条 端口 或者 这 st-总线 端口. 在 这

nt 模式, 定时 是 发生 从 一个 在 板

数字的 阶段 锁 循环 这个 extracts 定时 从

这 received 数据 在 这 dsl 和 发生 这

系统 框架 脉冲波 (f0b), 这 系统 4096 khz

时钟 (c4b

) 和 这 系统 superframe 脉冲波 (sfb).

这 superframe 定时 信号 (sfb

) 是 一个 起作用的 低

信号 和 一个 时期 的 12ms 这个 是 必需的 至

提供 一个 涉及 为 structuring 这 maintenance

频道 (m 频道). 在 这 lt 模式, 这 sfb

是 一个

输入 这个, 当 设置 低 在 这 系统 框架

脉冲波 (f0b

), 将 设置 这 阶段 的 这 transmit

superframe. 作 一个 alternative, 这 sfb

管脚 能 是

系 高 和 这 设备 将 automatically establish

图示 7 - st-总线 函数的 定时

F0b

C4b

st-总线

位

Cells

频道 31

位 0

频道 0

位 7

频道 0

位 6

频道 0

位 5

频道 0

位 4

频道 0

位 3

频道 0

位 2