4 altera 公司

串行 配置 设备 (epcs1 &放大; epcs4) 数据 薄板

管脚 描述

作 显示 在图示 1, 这 串行 配置 设备 是 一个 8-管脚 设备.

这 控制 管脚 在 这 串行 配置 设备 是: 串行 数据 输出

(

数据

), 起作用的 串行 数据 输入 (

ASDI

), 串行 时钟 (

DCLK

), 和 碎片 选择

(

nCS

).表格 3显示 这 串行 配置 设备的 管脚 描述.

程序编制

&放大; 配置

文件 支持

这 quartus ii 设计 软件 提供 程序编制 支持 为 串行

配置 设备. 之后 selecting 这 串行 配置 设备, 这

quartus ii 软件 automatically 发生 这 programmer 物体 文件

(

.pof

) 至 程序 这 设备. 这 软件 准许 用户 至 选择 这

适合的 串行 配置 设备 密度 那 大多数 efficiently stores

这 配置 数据 为 一个 选择 cyclone fpga.

串行 配置 设备 是 编写程序 使用 这 apu 和 这

适合的 程序编制 adapter (plmsepc-8) 通过 这 quartus ii

软件 或者 这 byteblaster ii 下载 缆索 通过 这 quartus ii 软件.

在 增加, 许多 第三-群 programmers, 此类 作 bp microsystems

和 系统 一般, 提供 程序编制 硬件 那 支持 串行

配置 设备.

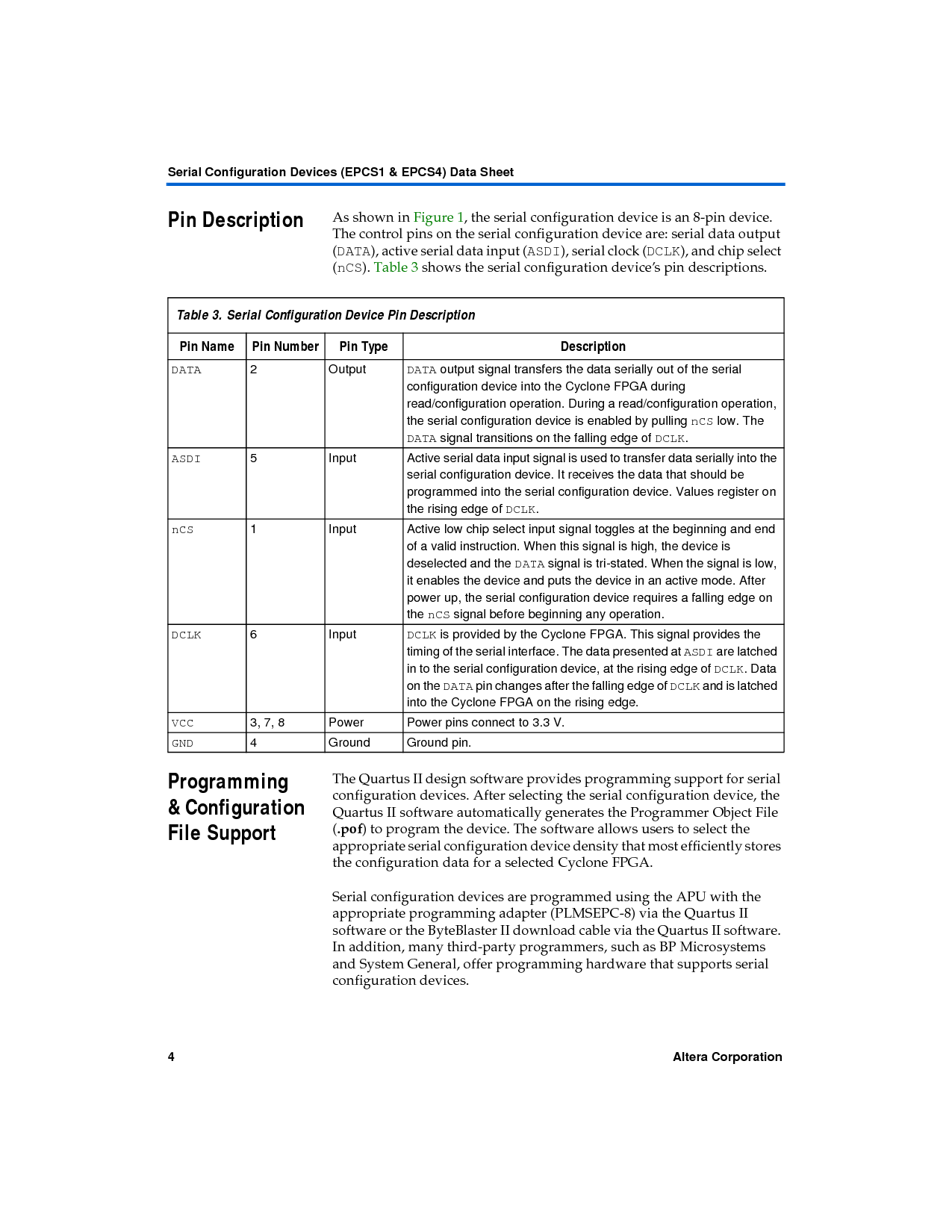

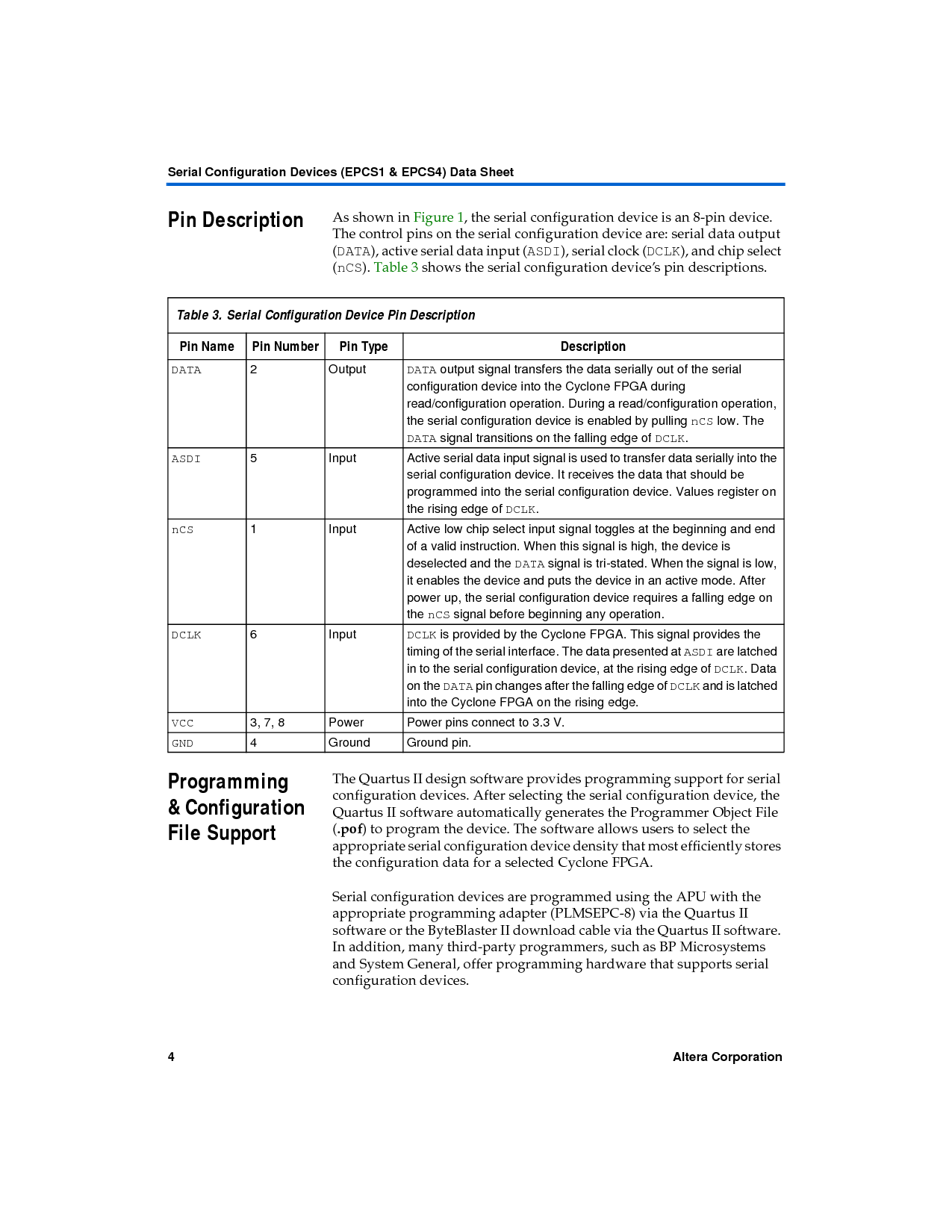

表格 3. 串行 配置 设备 管脚 描述

管脚 名字 管脚 号码 管脚 类型 描述

数据

2 输出

数据

输出 信号 transfers 这 数据 serially 输出 的 这 串行

配置 设备 在 这 cyclone fpga 在

读/配置 运作. 在 一个 读/配置 运作,

这 串行 配置 设备 是 使能 用 拉

nCS

低. 这

数据

信号 transitions 在 这 下落 边缘 的

DCLK

.

ASDI

5 输入 起作用的 串行 数据 输入 信号 是 使用 至 转移 数据 serially 在 这

串行 配置 设备. 它 receives 这 数据 那 应当 是

编写程序 在 这 串行 配置 设备. 值 寄存器 在

这 rising 边缘 的

DCLK

.

nCS

1 输入 起作用的 低 碎片 选择 输入 信号 toggles 在 这 beginning 和 终止

的 一个 有效的 操作指南. 当 这个 信号 是 高, 这 设备 是

deselected 和 这

数据

信号 是 触发-陈述. 当 这 信号 是 低,

它 使能 这 设备 和 puts 这 设备 在 一个 起作用的 模式. 之后

电源 向上, 这 串行 配置 设备 需要 一个 下落 边缘 在

这

nCS

信号 在之前 beginning 任何 运作.

DCLK

6 输入

DCLK

是 提供 用 这 cyclone fpga. 这个 信号 提供 这

定时 的 这 串行 接口. 这 数据 提交 在

ASDI

是 latched

在 至 这 串行 配置 设备, 在 这 rising 边缘 的

DCLK

. 数据

在 这

数据

管脚 改变 之后 这 下落 边缘 的

DCLK

和 是 latched

在 这 cyclone fpga 在 这 rising 边缘.

VCC

3, 7, 8 电源 电源 管脚 连接 至 3.3 v.

地

4 地面 地面 管脚.