rev. b

–8–

AD768

数字的 输入 代号 – k

8

–8

06510 20 30 40

4

–2

–4

–6

6

0

2

dnl 错误 – lsb

50 6051525354555

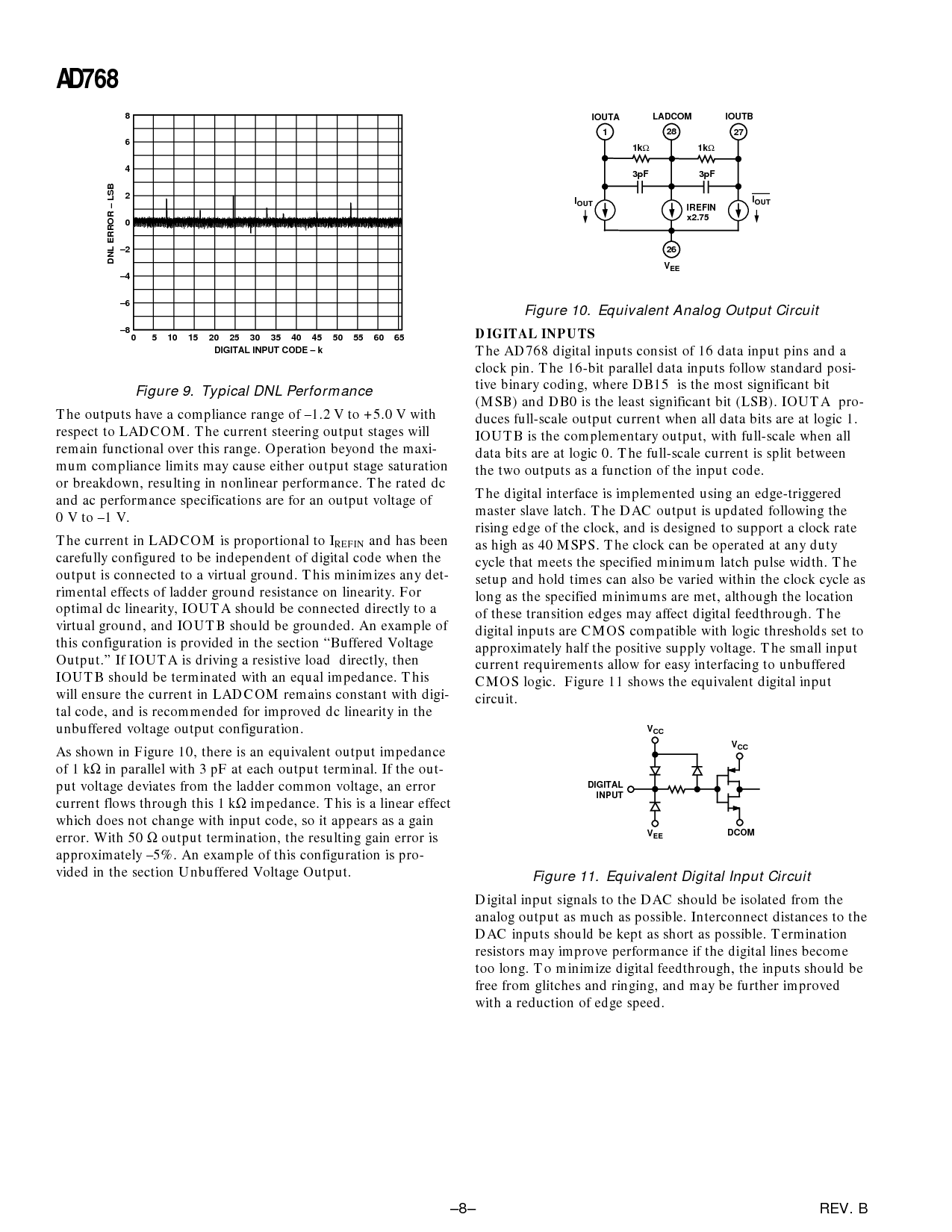

图示 9. 典型 dnl 效能

这 输出 有 一个 遵从 范围 的 –1.2 v 至 +5.0 v 和

遵守 至 ladcom. 这 电流 steering 输出 stages 将

仍然是 函数的 在 这个 范围. 运作 在之外 这 maxi-

mum 遵从 限制 将 导致 也 输出 平台 饱和

或者 损坏, 结果 在 非线性的 效能. 这 评估 直流

和 交流 效能 规格 是 为 一个 输出 电压 的

0 v 至 –1 v.

这 电流 在 ladcom 是 均衡的 至 i

REFIN

和 有 被

carefully 配置 至 是 独立 的 数字的 代号 当 这

输出 是 连接 至 一个 模拟的 地面. 这个 降低 任何 det-

rimental 影响 的 ladder 地面 阻抗 在 线性. 为

最优的 直流 线性, iouta 应当 是 连接 直接地 至 一个

模拟的 地面, 和 ioutb 应当 是 grounded. 一个 例子 的

这个 配置 是 提供 在 这 部分 “buffered 电压

输出.” 如果 iouta 是 驱动 一个 resistive 加载 直接地, 然后

ioutb 应当 是 terminated 和 一个 equal 阻抗. 这个

将 确保 这 电流 在 ladcom 仍然是 常量 和 digi-

tal 代号, 和 是 推荐 为 改进 直流 线性 在 这

unbuffered 电压 输出 配置.

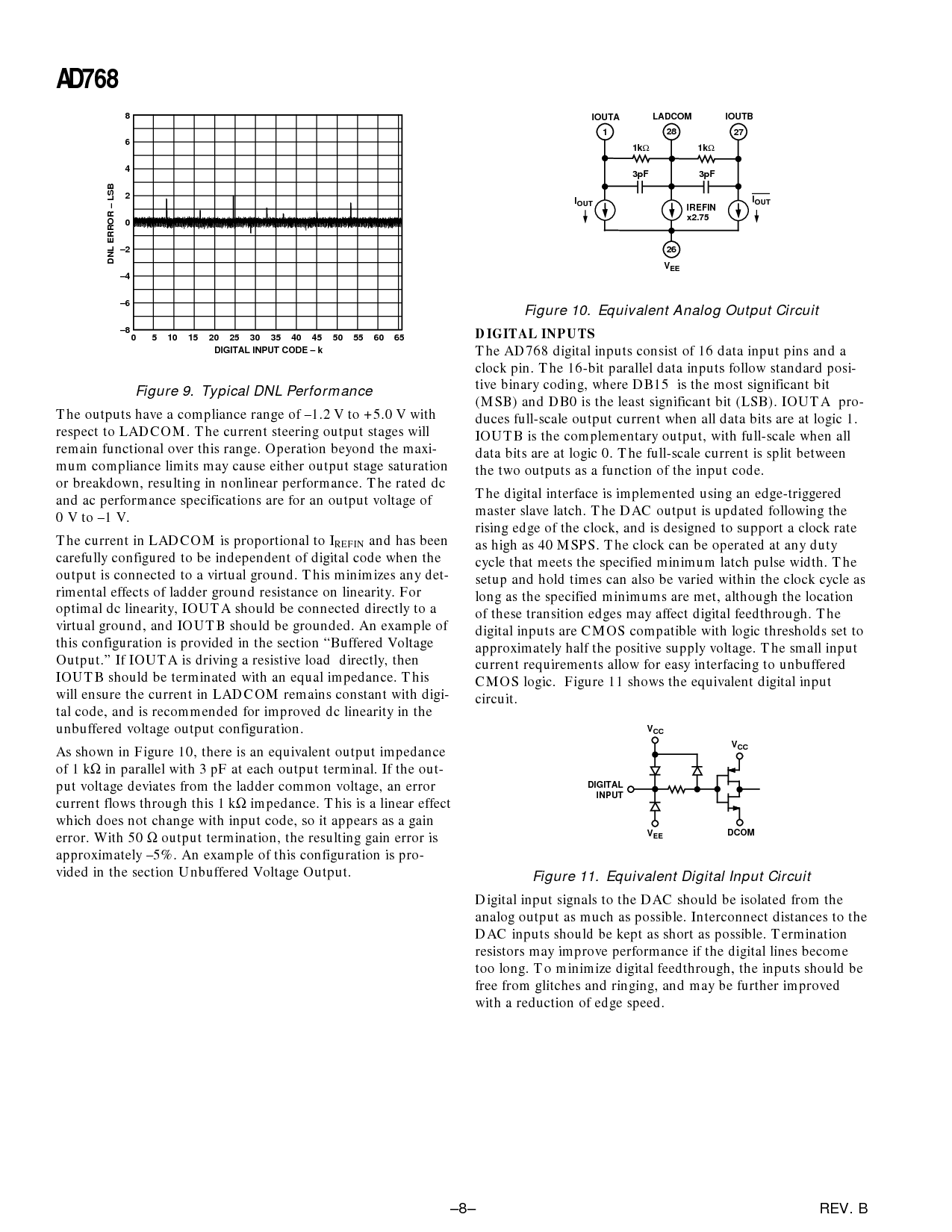

作 显示 在 图示 10, 那里 是 一个 相等的 输出 阻抗

的 1 k

Ω

在 并行的 和 3 pf 在 各自 输出 终端. 如果 这 输出-

放 电压 deviates 从 这 ladder 一般 电压, 一个 错误

电流 flows 通过 这个 1 k

Ω

阻抗. 这个 是 一个 直线的 效应

这个 做 不 改变 和 输入 代号, 所以 它 呈现 作 一个 增益

错误. 和 50

Ω

输出 末端, 这 结果 增益 错误 是

大概 –5%. 一个 例子 的 这个 配置 是 pro-

vided 在 这 部分 unbuffered 电压 输出.

1

26

27

28

1k

Ω

1k

Ω

3pF 3pF

I

输出

I

输出

IREFIN

x2.75

V

EE

LADCOM IOUTB

IOUTA

图示 10. 相等的 相似物 输出 电路

数字的 输入

这 ad768 数字的 输入 组成 的 16 数据 输入 管脚 和 一个

时钟 管脚. 这 16-位 并行的 数据 输入 follow 标准 posi-

tive 二进制的 编码, 在哪里 db15 是 这 大多数 重大的 位

(msb) 和 db0 是 这 least 重大的 位 (lsb). iouta pro-

duces 全部-规模 输出 电流 当 所有 数据 位 是 在 逻辑 1.

ioutb 是 这 complementary 输出, 和 全部-规模 当 所有

数据 位 是 在 逻辑 0. 这 全部-规模 电流 是 分割 在

这 二 输出 作 一个 函数 的 这 输入 代号.

这 数字的 接口 是 执行 使用 一个 边缘-triggered

主控 从动装置 获得. 这 dac 输出 是 updated 下列的 这

rising 边缘 的 这 时钟, 和 是 设计 至 支持 一个 时钟 比率

作 高 作 40 msps. 这 时钟 能 是 运作 在 任何 职责

循环 那 满足 这 指定 最小 获得 脉冲波 宽度. 这

建制 和 支撑 时间 能 也 是 varied 在里面 这 时钟 循环 作

长 作 这 指定 minimums 是 符合, 虽然 这 location

的 这些 转变 edges 将 影响 数字的 feedthrough. 这

数字的 输入 是 cmos 兼容 和 逻辑 门槛 设置 至

大概 half 这 积极的 供应 电压. 这 小 输入

电流 (所需的)东西 准许 为 容易 接合 至 unbuffered

cmos 逻辑. 图示 11 显示 这 相等的 数字的 输入

电路.

V

CC

V

EE

数字的

输入

V

CC

DCOM

图示 11. 相等的 数字的 输入 电路

数字的 输入 信号 至 这 dac 应当 是 分开的 从 这

相似物 输出 作 更 作 可能. interconnect 距离 至 这

dac 输入 应当 是 保持 作 短的 作 可能. 末端

电阻器 将 改进 效能 如果 这 数字的 线条 变为

too 长. 至 降低 数字的 feedthrough, 这 输入 应当 是

自由 从 glitches 和 ringing, 和 将 是 更远 改进

和 一个 减少 的 边缘 速.