®

9

ADS7841

转换器

+IN

–在

CH0

CH1

CH2

CH3

COM

a2-a0

(显示 001

B

)

sgl/dif

(显示 高)

theory 的 运作

这 ads7841 是 一个 classic successive approximation 寄存器

(sar) 相似物-至-数字的 (一个/d) 转换器. 这 architecture 是

为基础 在 电容的 redistribution 这个 本质上 包含

一个 样本/支撑 函数. 这 转换器 是 fabricated 在 一个

0.6

µ

s cmos 处理.

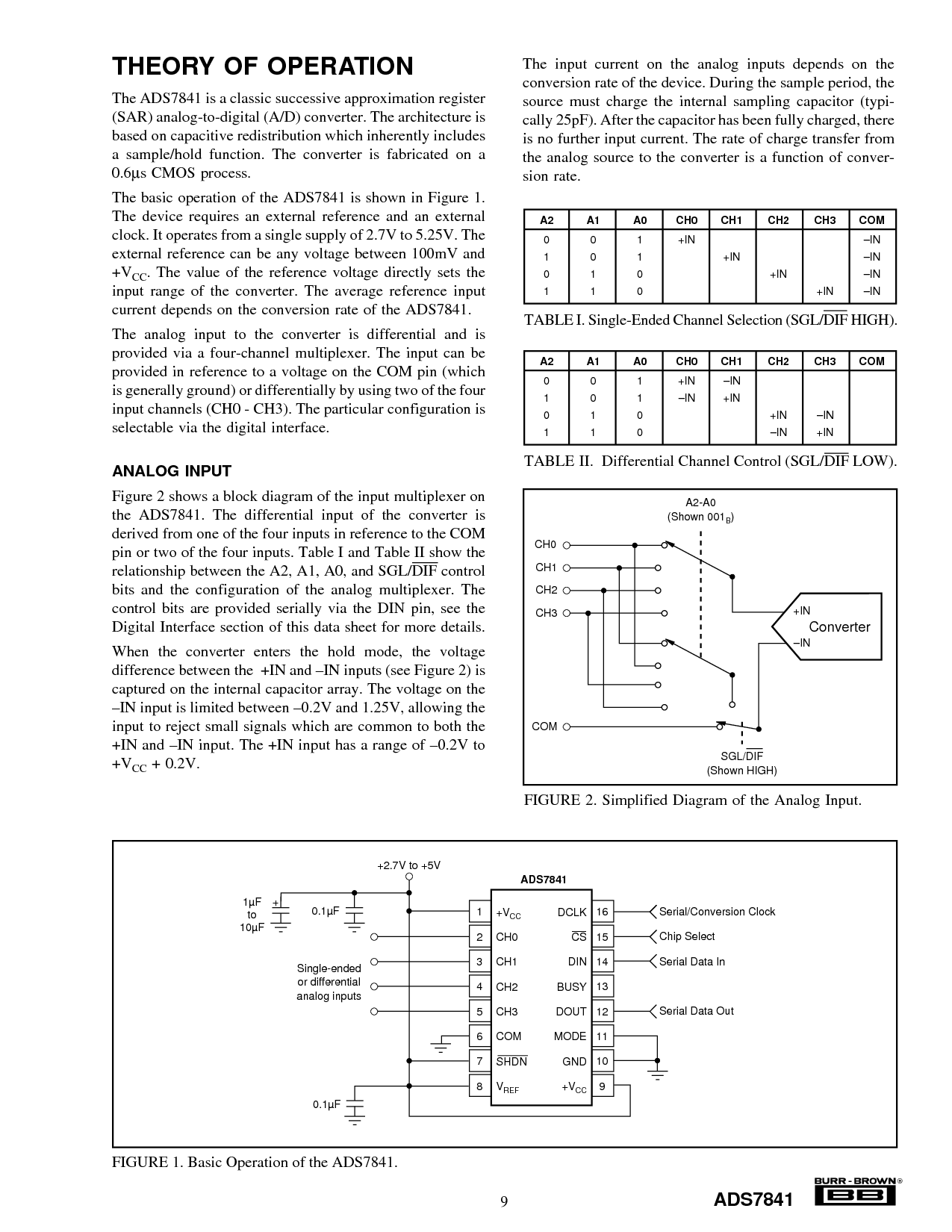

这 基本 运作 的 这 ads7841 是 显示 在 图示 1.

这 设备 需要 一个 外部 涉及 和 一个 外部

时钟. 它 运作 从 一个 单独的 供应 的 2.7v 至 5.25v. 这

外部 涉及 能 是 任何 电压 在 100mv 和

+V

CC

. 这 值 的 这 涉及 电压 直接地 sets 这

输入 范围 的 这 转换器. 这 平均 涉及 输入

电流 取决于 在 这 转换 比率 的 这 ads7841.

这 相似物 输入 至 这 转换器 是 差别的 和 是

提供 通过 一个 四-频道 多路调制器. 这 输入 能 是

提供 在 涉及 至 一个 电压 在 这 com 管脚 (这个

是 一般地 地面) 或者 differentially 用 使用 二 的 这 四

输入 途径 (ch0 - ch3). 这 particular 配置 是

可选择的 通过 这 数字的 接口.

相似物 输入

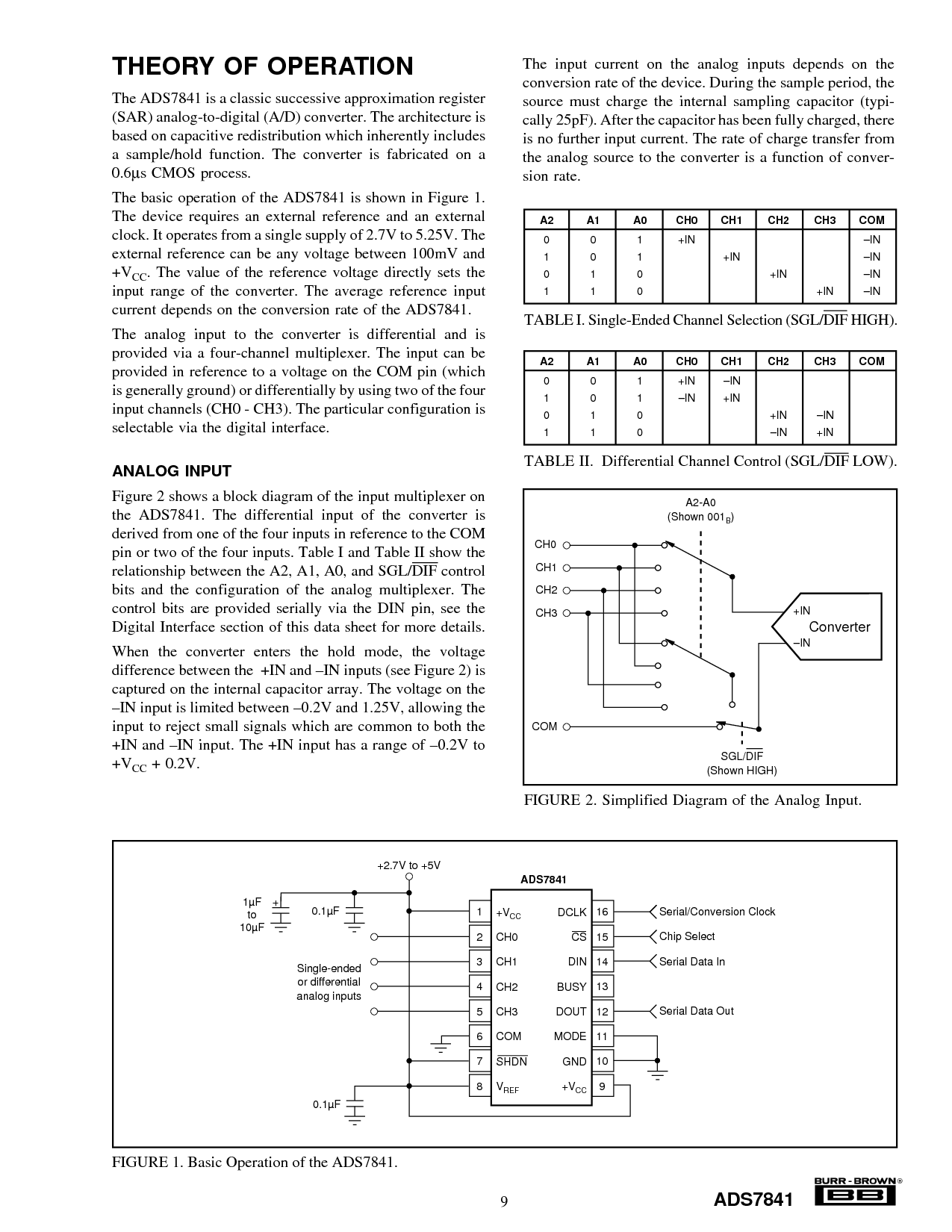

图示 2 显示 一个 块 图解 的 这 输入 多路调制器 在

这 ads7841. 这 差别的 输入 的 这 转换器 是

获得 从 一个 的 这 四 输入 在 涉及 至 这 com

管脚 或者 二 的 这 四 输入. 表格 i 和 表格 ii 显示 这

relationship 在 这 a2, a1, a0, 和 sgl/dif 控制

位 和 这 配置 的 这 相似物 多路调制器. 这

控制 位 是 提供 serially 通过 这 din 管脚, 看 这

数字的 接口 部分 的 这个 数据 薄板 为 更多 详细信息.

当 这 转换器 enters 这 支撑 模式, 这 电压

区别 在 这 +in 和 –in 输入 (看 图示 2) 是

captured 在 这 内部的 电容 排列. 这 电压 在 这

–in 输入 是 限制 在 –0.2v 和 1.25v, 准许 这

输入 至 reject 小 信号 这个 是 一般 至 两个都 这

+in 和 –in 输入. 这 +in 输入 有 一个 范围 的 –0.2v 至

+V

CC

+ 0.2v.

图示 2. simplified 图解 的 这 相似物 输入.

A2 A1 A0 CH0 CH1 CH2 CH3 COM

0 0 1 +IN –IN

1 0 1 –IN +IN

0 1 0 +IN –IN

1 1 0 –IN +IN

表格ii. 差别的 频道 控制 (sgl/dif 低).

A2 A1 A0 CH0 CH1 CH2 CH3 COM

0 0 1 +IN –IN

1 0 1 +IN –IN

0 1 0 +IN –IN

1 1 0 +IN –IN

表格 i. 单独的-结束 频道 选择 (sgl/dif 高).

这 输入 电流 在 这 相似物 输入 取决于 在 这

转换 比率 的 这 设备. 在 这 样本 时期, 这

源 必须 承担 这 内部的 抽样 电容 (typi-

cally 25pf). 之后 这 电容 有 被 全部地 charged, 那里

是 非 更远 输入 电流. 这 比率 的 承担 转移 从

这 相似物 源 至 这 转换器 是 一个 函数 的 变换器-

sion 比率.

图示 1. 基本 运作 的 这 ads7841.

+V

CC

CH0

CH1

CH2

CH3

COM

SHDN

V

REF

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

DCLK

CS

DIN

BUSY

DOUT

模式

地

+V

CC

串行/转换 时钟

碎片 选择

串行 数据 在

串行 数据 输出

0.1µf

0.1µf

+2.7v 至 +5v

ADS7841

单独的-结束

或者 差别的

相似物 输入

+

1µF

至

10µF