二月 27, 1997 3

galvantech, 公司 reserves 这 正确的 至 改变 产品 或者 规格 没有 注意.

rev. 2/97

GVT71128E36

128k x 36 同步的 burst sram

GALVANTECH

, 公司

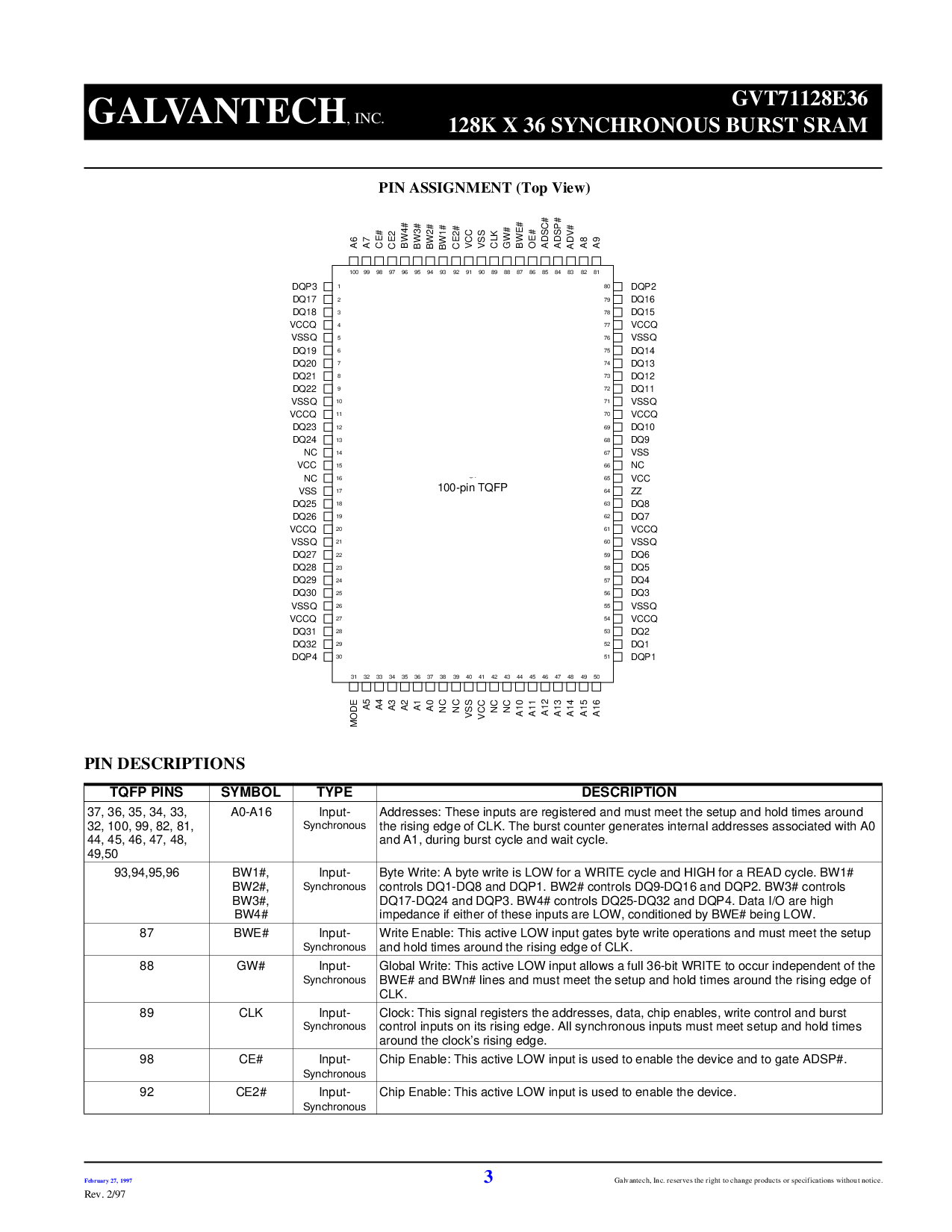

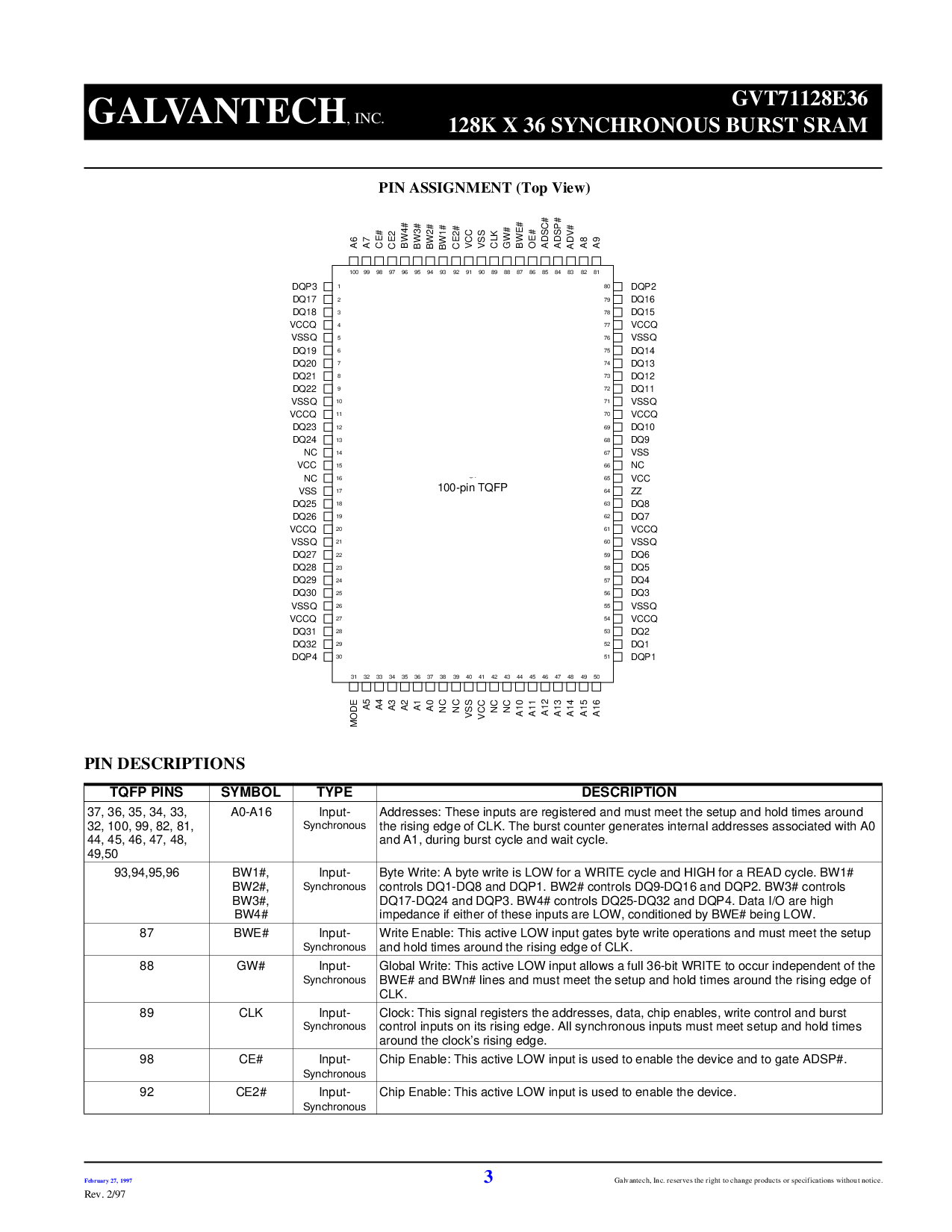

管脚 分派 (顶 视图)

管脚 描述S

tqfp 管脚S SYMBOL 典型值E DESCRIPTION

37, 36, 35, 34, 33,

32, 100, 99, 82, 81,

44, 45, 46, 47, 48,

49,50

a0-a16 输入-

Synchronous

地址: 这些 输入 是 注册 和 必须 满足 这 建制 和 支撑 时间 周围

这 rising 边缘 的 clk. 这 burst 计数器 发生 内部的 地址 有关联的 和 a0

和 a1, 在 burst 循环 和 wait 循环.

93,94,95,96 bw1#,

bw2#,

bw3#,

BW4#

输入-

Synchronous

字节 写: 一个 字节 写 是 低 为 一个 写 循环 和 高 为 一个 读 循环. bw1#

控制 dq1-dq8 和 dqp1. bw2# 控制 dq9-dq16 和 dqp2. bw3# 控制

dq17-dq24 和 dqp3. bw4# 控制 dq25-dq32 和 dqp4. 数据 i/o 是 高

阻抗 如果 也 的 这些 输入 是 低, conditioned 用 bwe# 正在 低.

87 BWE# 输入-

Synchronous

写 使能: 这个 起作用的 低 输入 门 字节 写 行动 和 必须 满足 这 建制

和 支撑 时间 周围 这 rising 边缘 的 clk.

88 GW# 输入-

Synchronous

global 写: 这个 起作用的 低 输入 准许 一个 全部 36-位 写 至 出现 独立 的 这

bwe# 和 bwn# 线条 和 必须 满足 这 建制 和 支撑 时间 周围 这 rising 边缘 的

CLK.

89 CLK 输入-

Synchronous

时钟: 这个 信号 寄存器 这 地址, 数据, 碎片 使能, 写 控制 和 burst

控制 输入 在 它的 rising 边缘. 所有 同步的 输入 必须 满足 建制 和 支撑 时间

周围 这 时钟’s rising 边缘.

98 CE# 输入-

Synchronous

碎片 使能: 这个 起作用的 低 输入 是 使用 至 使能 这 设备 和 至 门 adsp#.

92 CE2# 输入-

Synchronous

碎片 使能: 这个 起作用的 低 输入 是 使用 至 使能 这 设备.

100-管脚 pqfp

或者

100-管脚 tqfp

100 99 98 97 96 95 94 93 92 91 90 89 88

1

2

3

4

5

6

7

8

9

10

31 32 33 34 35 36 37 38 39 40 41 42 43

87 86 85 84 83 82 81

80

79

78

77

76

75

74

73

72

71

70

69

68

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

44 45 46 47 48 49 50

A6

A7

CE#

ADSC#

ADSP#

ADV#

CLK

OE#

A8

A9

VCC

VSS

GW#

BWE#

CE2#

DQP2

DQ16

DQ15

VSSQ

VCCQ

DQ10

DQ9

DQ8

DQ7

VCCQ

VSSQ

DQ6

DQ5

VSS

NC

VCC

ZZ

A5

A4

A3

A2

A1

A0

VSS

VCC

A10

A14

A13

A12

A11

模式

NC

NC

NC

NC

A15

A16

CE2

BW4#

BW3#

BW2#

BW1#

VCCQ

VSSQ

DQ14

DQ13

DQ12

DQ11

DQ4

DQ3

DQ2

DQ1

DQP1

VSSQ

VCCQ

DQP3

DQ17

DQ18

VSSQ

VCCQ

DQ23

DQ24

DQ25

DQ26

VCCQ

VSSQ

DQ27

DQ28

VSS

NC

VCC

NC

VCCQ

VSSQ

DQ19

DQ20

DQ21

DQ22

DQ29

DQ30

DQ31

DQ32

DQP4

VSSQ

VCCQ