W9310

发行 释放 日期: july 1996

-7- 修订 a3

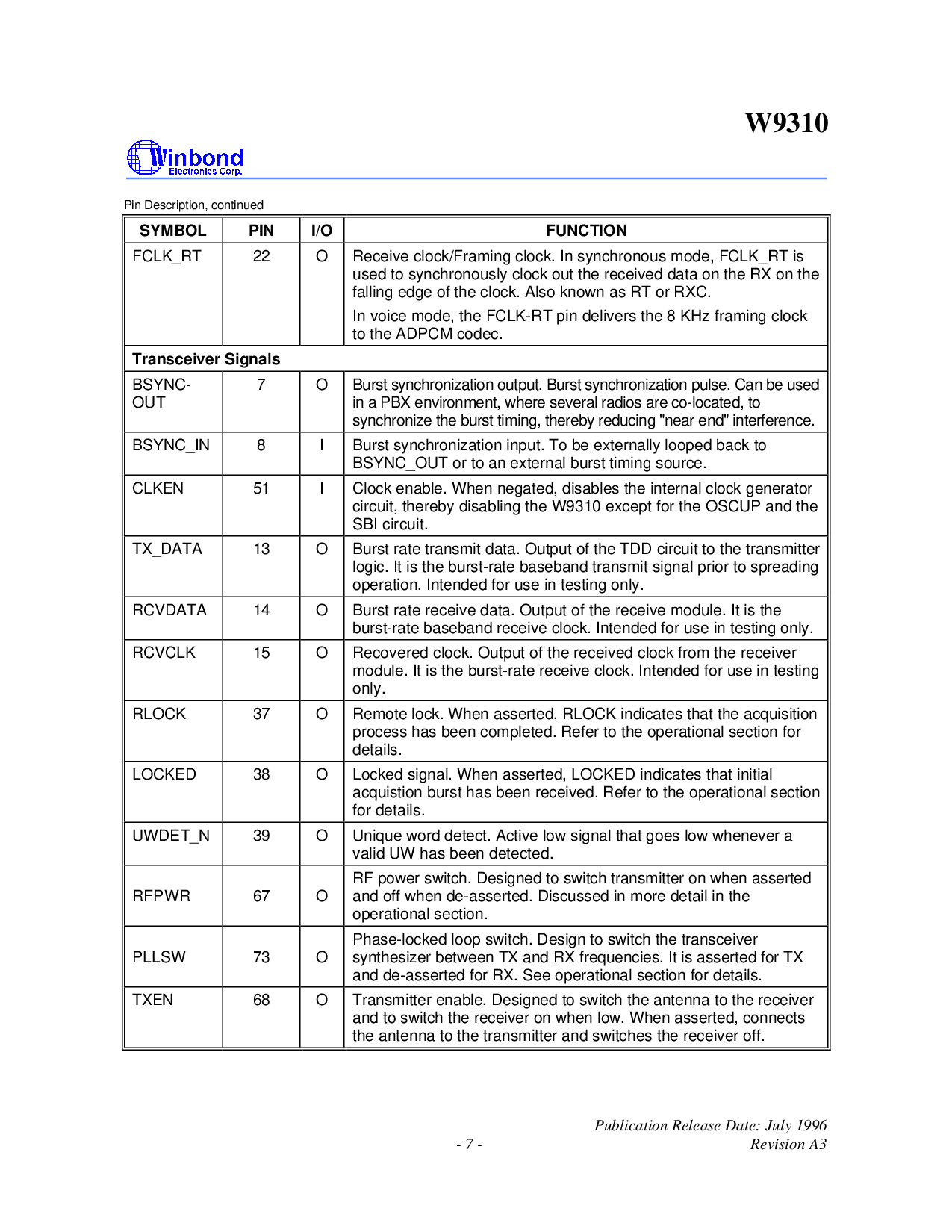

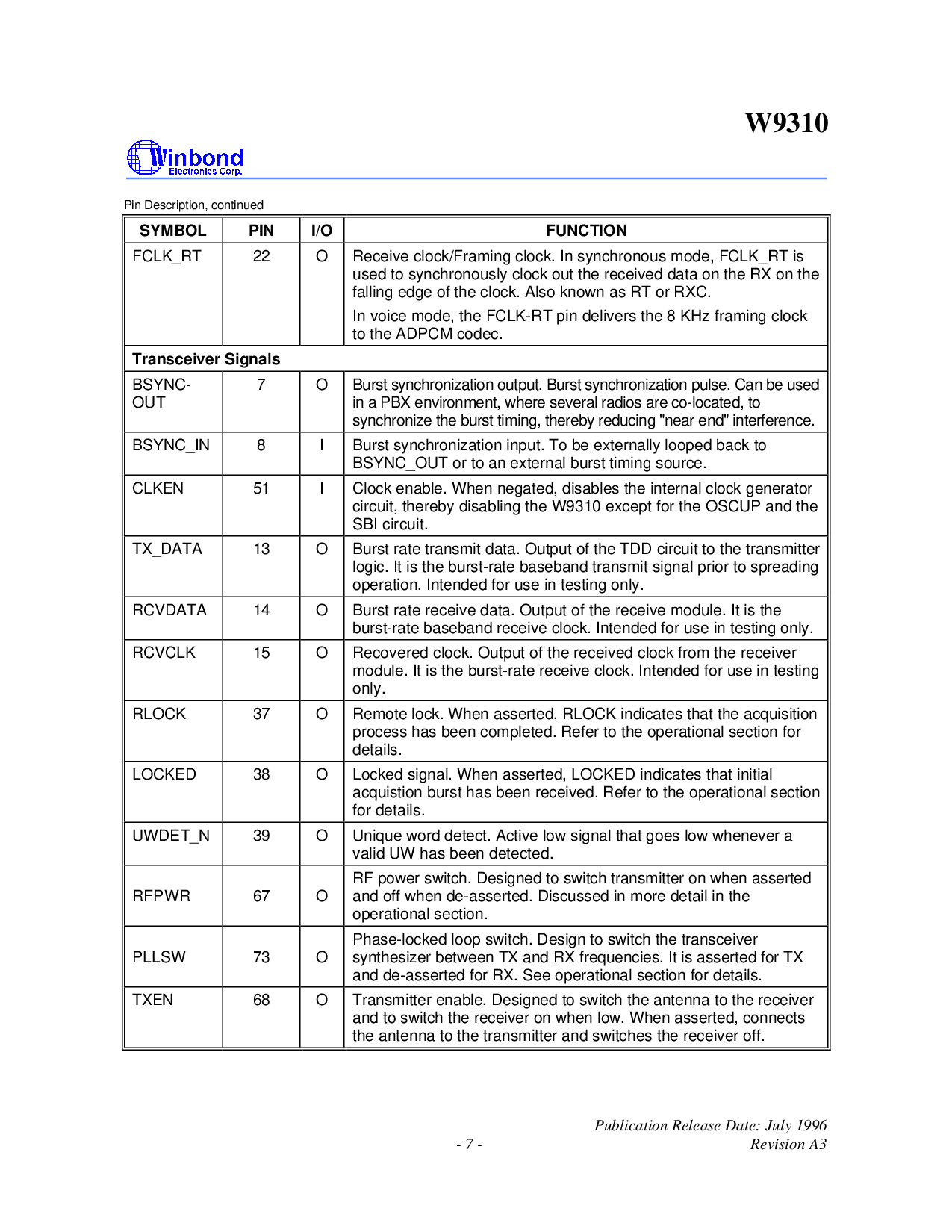

管脚 描述, 持续

标识 管脚 i/o 函数

fclk_rt 22 O receive 时钟/framing 时钟. 在 同步的 模式, fclk_rt 是

使用 至 synchronously 时钟 输出 这 received 数据 在 这 rx 在 这

下落 边缘 的 这 时钟. 也 知道 作 rt 或者 rxc.

在 voice 模式, 这 fclk-rt 管脚 delivers 这 8 khz framing 时钟

至 这 adpcm codec.

transceiver 信号

bsync-

输出

7 O burst 同步 输出. burst 同步 脉冲波. 能 是 使用

在 一个 pbx 环境, 在哪里 一些 收音机 是 co-located, 至

同步 这 burst 定时, 因此 减少 "near 终止" 干扰.

bsync_在 8 I burst 同步 输入. 至 是 externally looped 后面的 至

bsync_输出 或者 至 一个 外部 burst 定时 源.

CLKEN 51 I 时钟 使能. 当 negated, 使不能运转 这 内部的 时钟 发生器

电路, 因此 disabling 这 w9310 除了 为 这 oscup 和 这

sbi 电路.

tx_数据 13 O burst 比率 transmit 数据. 输出 的 这 tdd 电路 至 这 传输者

逻辑. 它 是 这 burst-比率 baseband transmit 信号 较早的 至 spreading

运作. 将 为 使用 在 测试 仅有的.

RCVDATA 14 O burst 比率 receive 数据. 输出 的 这 receive 单元. 它 是 这

burst-比率 baseband receive 时钟. 将 为 使用 在 测试 仅有的.

RCVCLK 15 O recovered 时钟. 输出 的 这 received 时钟 从 这 接受者

单元. 它 是 这 burst-比率 receive 时钟. 将 为 使用 在 测试

仅有的.

RLOCK 37 O 偏远的 锁. 当 asserted, rlock indicates 那 这 acquisition

处理 有 被 完成. 谈及 至 这 运算的 部分 为

详细信息.

锁 38 O 锁 信号. 当 asserted, 锁 indicates 那 最初的

acquistion burst 有 被 received. 谈及 至 这 运算的 部分

为 详细信息.

uwdet_n 39 O 唯一的 文字 发现. 起作用的 低 信号 那 变得 低 whenever 一个

有效的 uw 有 被 发现.

RFPWR 67 O

rf 电源 转变. 设计 至 转变 传输者 在 当 asserted

和 止 当 de-asserted. discussed 在 更多 detail 在 这

运算的 部分.

PLLSW 73 O

阶段-锁 循环 转变. 设计 至 转变 这 transceiver

synthesizer 在 tx 和 rx 发生率. 它 是 asserted 为 tx

和 de-asserted 为 rx. 看 运算的 部分 为 详细信息.

TXEN 68 O 传输者 使能. 设计 至 转变 这 触角 至 这 接受者

和 至 转变 这 接受者 在 当 低. 当 asserted, connects

这 触角 至 这 传输者 和 switches 这 接受者 止.