2000 二月 29 5

飞利浦 半导体 初步的 规格

ic card 接口 TDA8004AT

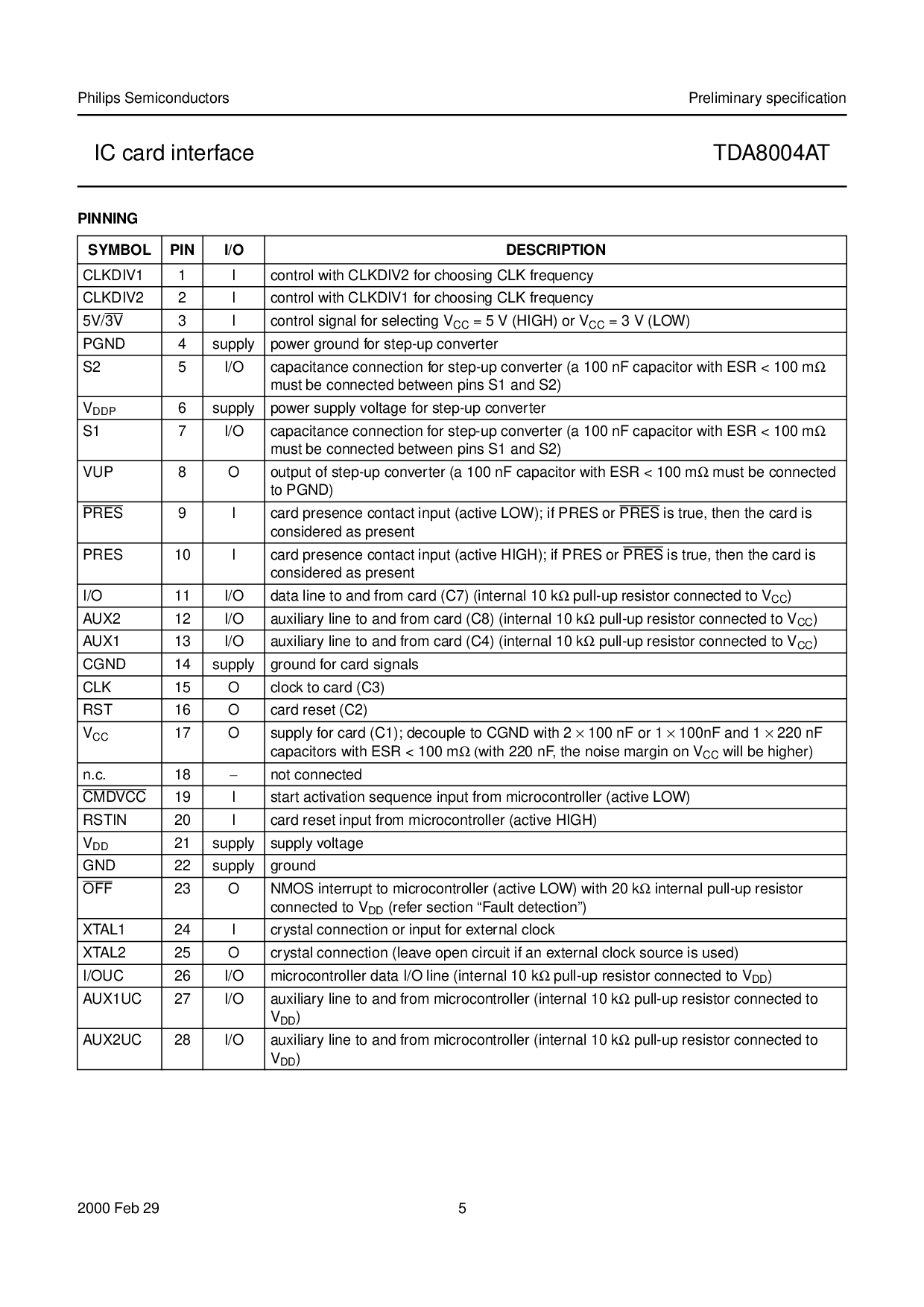

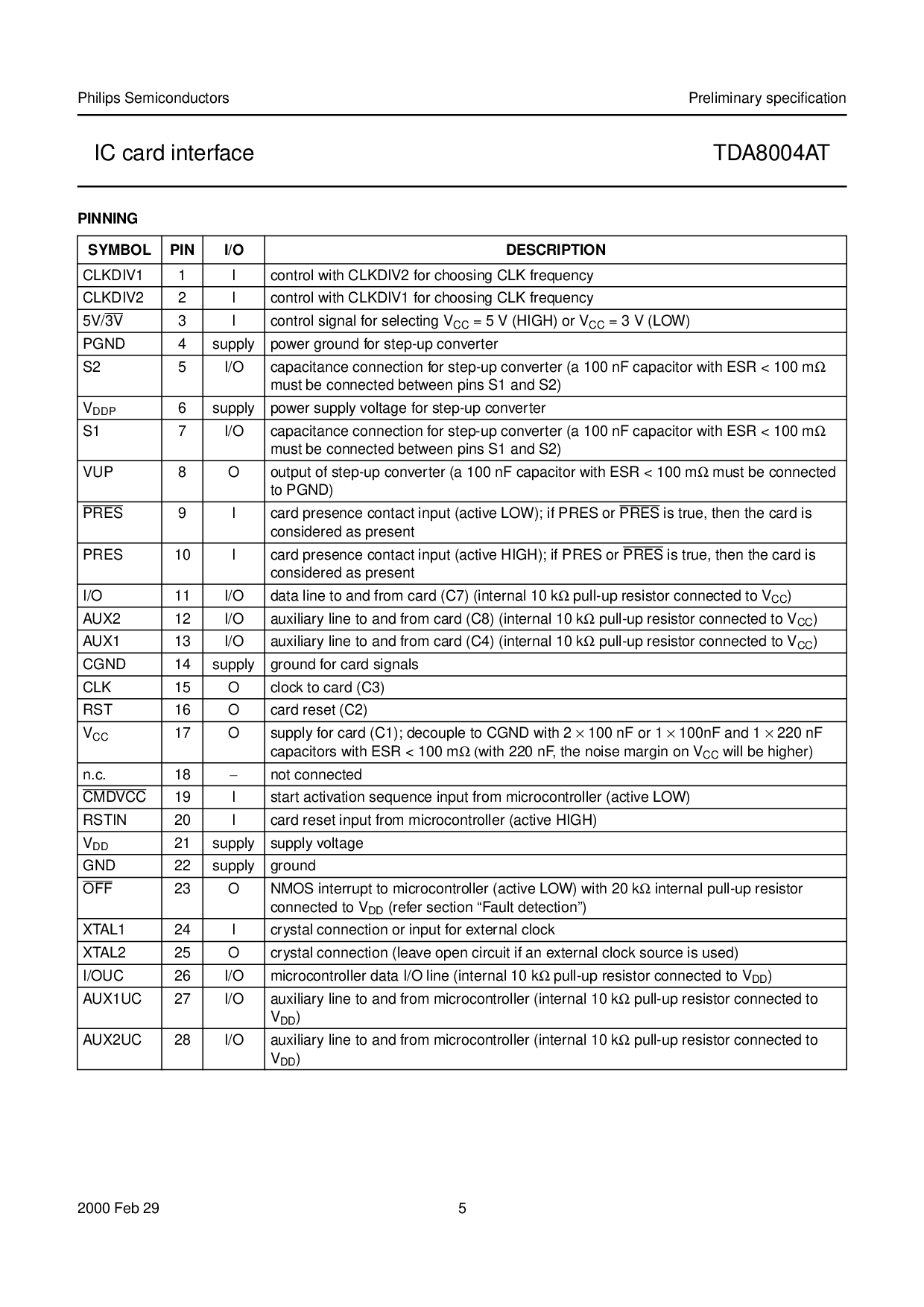

固定

标识 管脚 i/o 描述

CLKDIV1 1 I 控制 和 clkdiv2 为 choosing clk 频率

CLKDIV2 2 I 控制 和 clkdiv1 为 choosing clk 频率

5v/

3V 3 I 控制 信号 为 selecting v

CC

= 5 v (高) 或者 v

CC

= 3 v (低)

PGND 4 供应 电源 地面 为 步伐-向上 转换器

S2 5 i/o 电容 连接 为 步伐-向上 转换器 (一个 100 nf 电容 和 等效串联电阻 < 100 m

Ω

必须 是 连接 在 管脚 s1 和 s2)

V

DDP

6 供应 电源 供应 电压 为 步伐-向上 转换器

S1 7 i/o 电容 连接 为 步伐-向上 转换器 (一个 100 nf 电容 和 等效串联电阻 < 100 m

Ω

必须 是 连接 在 管脚 s1 和 s2)

VUP 8 O 输出 的 步伐-向上 转换器 (一个 100 nf 电容 和 等效串联电阻 < 100 m

Ω

必须 是 连接

至 pgnd)

PRES 9 I card 存在 联系 输入 (起作用的 低); 如果 pres 或者 pres 是 真实, 然后 这 card 是

考虑 作 呈现

PRES 10 I card 存在 联系 输入 (起作用的 高); 如果 pres 或者

pres 是 真实, 然后 这 card 是

考虑 作 呈现

i/o 11 i/o 数据 线条 至 和 从 card (c7) (内部的 10 k

Ω

拉-向上 电阻 连接 至 v

CC

)

AUX2 12 i/o auxiliary 线条 至 和 从 card (c8) (内部的 10 k

Ω

拉-向上 电阻 连接 至 v

CC

)

AUX1 13 i/o auxiliary 线条 至 和 从 card (c4) (内部的 10 k

Ω

拉-向上 电阻 连接 至 v

CC

)

CGND 14 供应 地面 为 card 信号

CLK 15 O 时钟 至 card (c3)

RST 16 O card 重置 (c2)

V

CC

17 O 供应 为 card (c1); 分离 至 cgnd 和 2

×

100 nf 或者 1

×

100nf 和 1

×

220 nF

电容 和 等效串联电阻 < 100 m

Ω (

和 220 nf, 这 噪音 余裕 在 v

CC

将 是 高等级的)

n.c. 18

−

不 连接

CMDVCC 19 I 开始 触发 sequence 输入 从 微控制器 (起作用的 低)

RSTIN 20 I card 重置 输入 从 微控制器 (起作用的 高)

V

DD

21 供应 供应 电压

地 22 供应 地面

止 23 O nmos 中断 至 微控制器 (起作用的 低) 和 20 k

Ω

内部的 拉-向上 电阻

连接 至 v

DD

(谈及 部分 “fault detection”)

XTAL1 24 I 结晶 连接 或者 输入 为 外部 时钟

XTAL2 25 O 结晶 连接 (leave 打开 电路 如果 一个 外部 时钟 源 是 使用)

i/ouc 26 i/o 微控制器 数据 i/o 线条 (内部的 10 k

Ω

拉-向上 电阻 连接 至 v

DD

)

AUX1UC 27 i/o auxiliary 线条 至 和 从 微控制器 (内部的 10 k

Ω

拉-向上 电阻 连接 至

V

DD

)

AUX2UC 28 i/o auxiliary 线条 至 和 从 微控制器 (内部的 10 k

Ω

拉-向上 电阻 连接 至

V

DD

)