5

ltc1421/ltc1421-2.5

典型 perforM一个Nce 特性

U

W

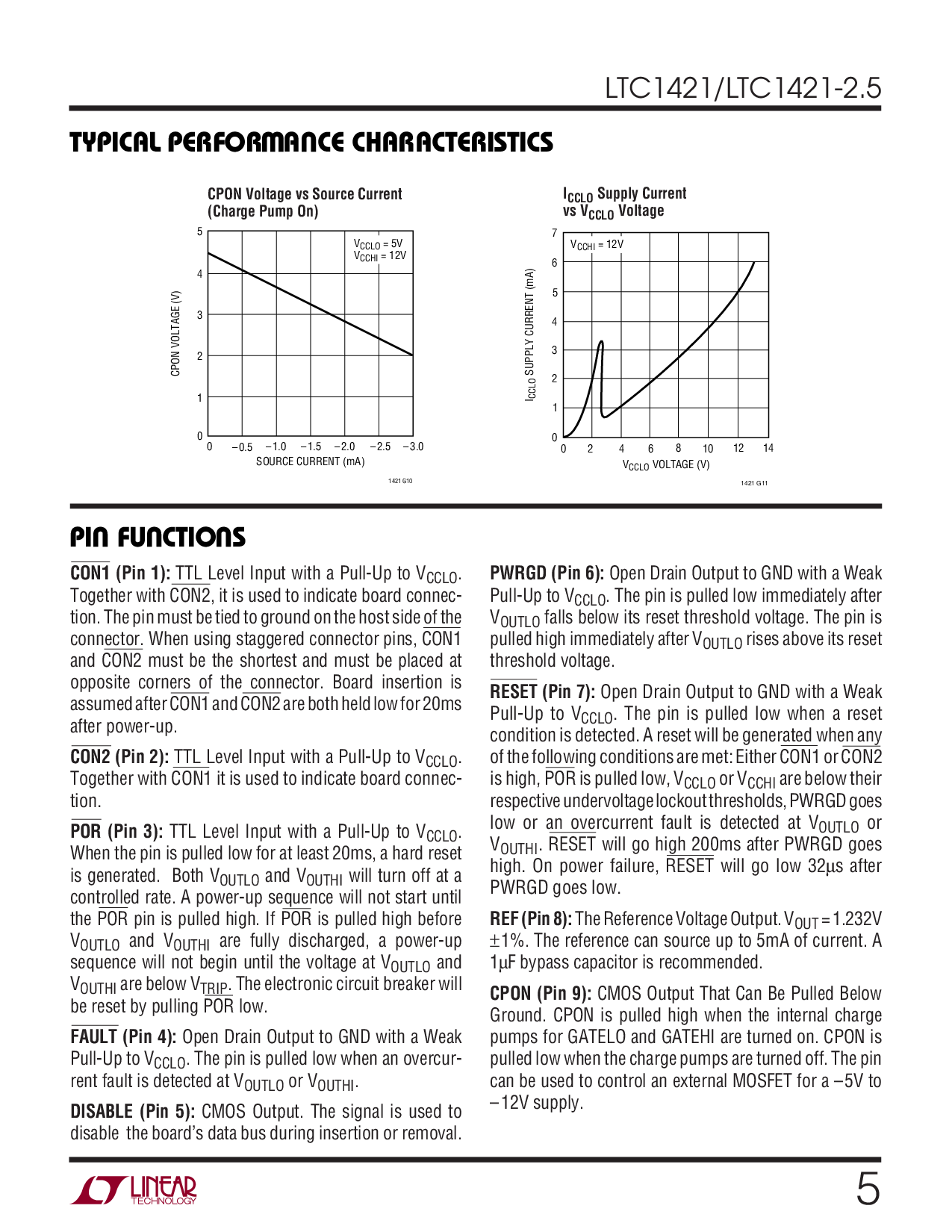

cpon 电压 vs 源 电流

(承担 打气 在)

源 电流 (毫安)

0

0

cpon 电压 (v)

1

2

3

4

5

–0.5

–1.0 –1.5 –2.0

1421 g10

–2.5 –3.0

V

CCLO

= 5v

V

CCHI

= 12v

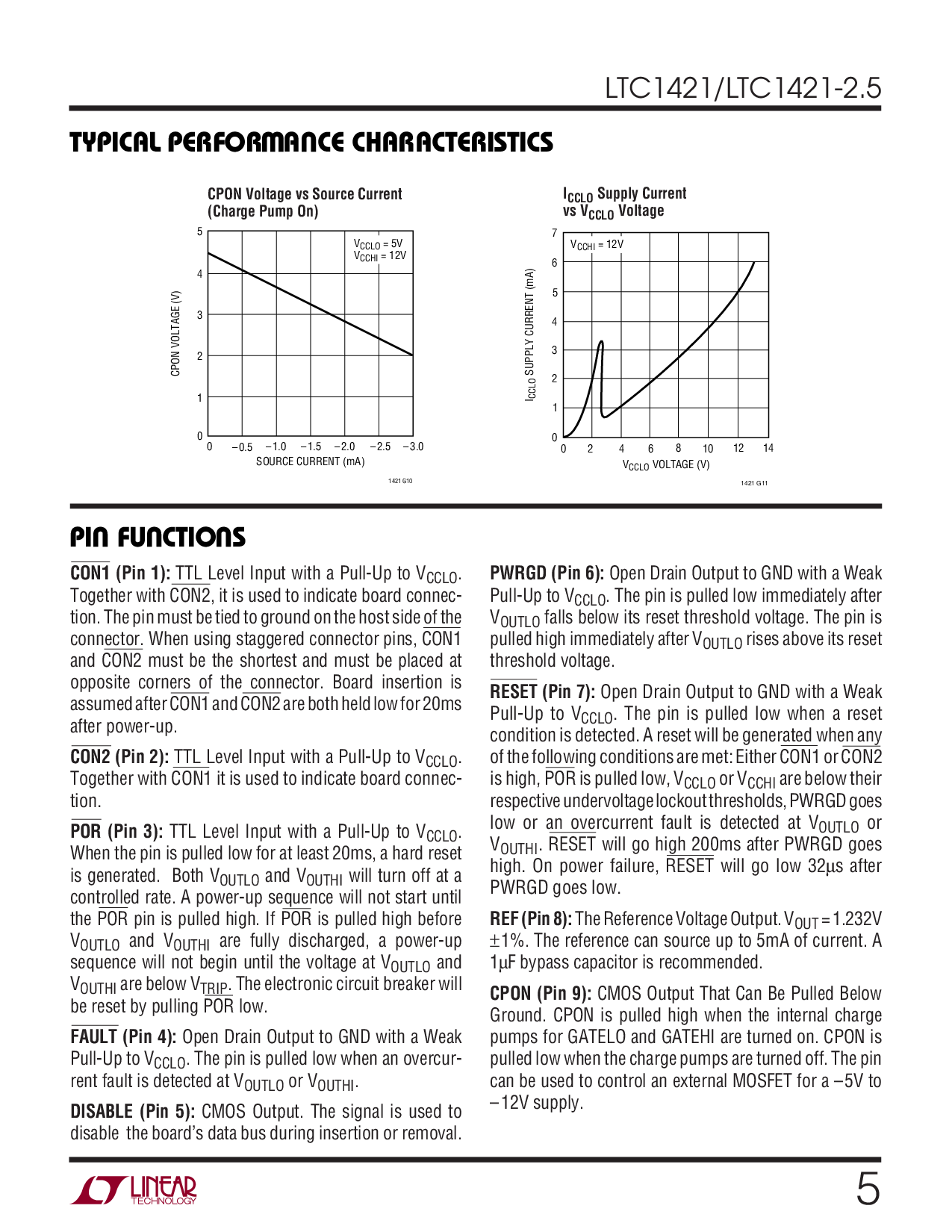

I

CCLO

供应 电流

vs v

CCLO

电压

V

CCLO

电压 (v)

0

4

5

7

610

1421 g11

3

2

24

81214

1

0

6

I

CCLO

供应 电流 (毫安)

V

CCHI

= 12v

PINFUNCTIONS

UUU

con1 (管脚 1):

ttl 水平的 输入 和 一个 拉-向上 至 v

CCLO

.

一起 和 con2, 它 是 使用 至 表明 板 connec-

tion. 这 管脚 必须 是 系 至 地面 在 这 host 一侧 的 这

连接器. 当 使用 staggered 连接器 管脚, con1

和 con2 必须 是 这 shortest 和 必须 是 放置 在

opposite corners 的 这 连接器. 板 嵌入 是

assumed 之后 con1 和 con2 是 两个都 使保持 低 为 20ms

之后 电源-向上.

con2 (管脚 2):

ttl 水平的 输入 和 一个 拉-向上 至 v

CCLO

.

一起 和 con1 它 是 使用 至 表明 板 connec-

tion.

por (管脚 3):

ttl 水平的 输入 和 一个 拉-向上 至 v

CCLO

.

当 这 管脚 是 牵引的 低 为 在 least 20ms, 一个 hard 重置

是 发生. 两个都 v

OUTLO

和 v

OUTHI

将 转变 止 在 一个

控制 比率. 一个 电源-向上 sequence 将 不 开始 直到

这 por 管脚 是 牵引的 高. 如果 por 是 牵引的 高 在之前

V

OUTLO

和 v

OUTHI

是 全部地 释放, 一个 电源-向上

sequence 将 不 begin 直到 这 电压 在 v

OUTLO

和

V

OUTHI

是 在下 v

TRIP

. 这 电子的 电路 breaker 将

是 重置 用 拉 por 低.

故障 (管脚 4):

打开 流 输出 至 地 和 一个 弱

拉-向上 至 v

CCLO

. 这 管脚 是 牵引的 低 当 一个 overcur-

rent 故障 是 发现 在 v

OUTLO

或者 v

OUTHI

.

使不能运转 (管脚 5):

cmos 输出. 这 信号 是 使用 至

使不能运转 这 板’s 数据 总线 在 嵌入 或者 除去.

pwrgd (管脚 6):

打开 流 输出 至 地 和 一个 弱

拉-向上 至 v

CCLO

. 这 管脚 是 牵引的 低 立即 之后

V

OUTLO

falls 在下 它的 重置 门槛 电压. 这 管脚 是

牵引的 高 立即 之后 v

OUTLO

rises 在之上 它的 重置

门槛 电压.

重置 (管脚 7):

打开 流 输出 至 地 和 一个 弱

拉-向上 至 v

CCLO

. 这 管脚 是 牵引的 低 当 一个 重置

情况 是 发现. 一个 重置 将 是 发生 当 任何

的 这 下列的 情况 是 符合: 也 con1 或者 con2

是 高, por 是 牵引的 低, v

CCLO

或者 v

CCHI

是 在下 它们的

各自的 欠压 lockout 门槛, pwrgd 变得

低 或者 一个 overcurrent 故障 是 发现 在 v

OUTLO

或者

V

OUTHI

. 重置 将 go 高 200ms 之后 pwrgd 变得

高. 在 电源 失败, 重置 将 go 低 32

µ

s 之后

pwrgd 变得 低.

ref (管脚 8):

这 涉及 电压 输出. v

输出

= 1.232v

±

1%. 这 涉及 能 源 向上 至 5ma 的 电流. 一个

1

µ

f 绕过 电容 是 推荐.

cpon (管脚 9):

cmos 输出 那 能 是 牵引的 在下

地面. cpon 是 牵引的 高 当 这 内部的 承担

pumps 为 gatelo 和 gatehi 是 转变 在. cpon 是

牵引的 低 当 这 承担 pumps 是 转变 止. 这 管脚

能 是 使用 至 控制 一个 外部 场效应晶体管 为 一个 –5v 至

–12v 供应.