cy7c0850av/cy7c0851av

cy7c0852av/cy7c0853av

文档 #: 38-06070 rev. *e 页 6 的 29

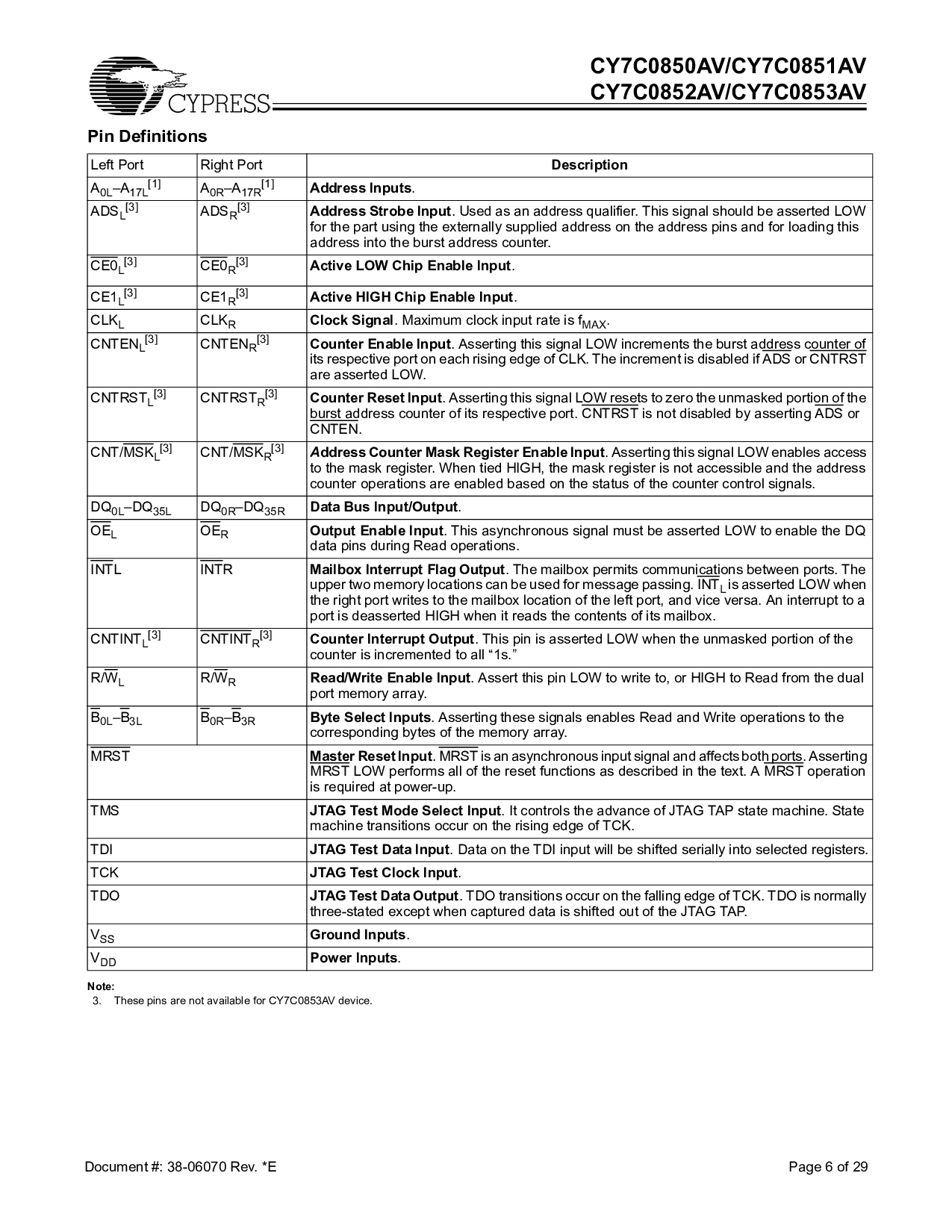

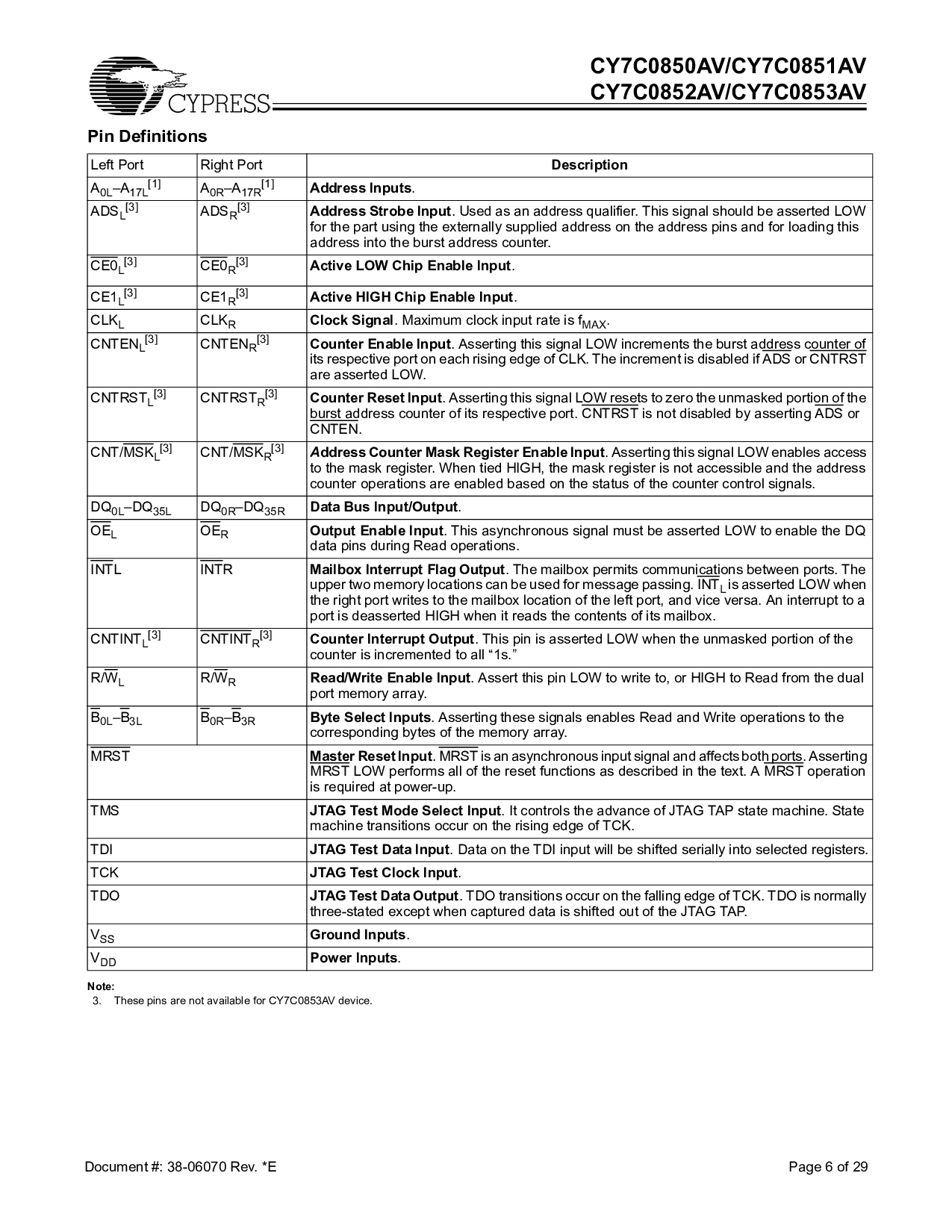

便条:

3. 这些 管脚 是 不 有 为 cy7c0853av 设备.

管脚 定义

left 端口 正确的 端口

描述

一个

0L

–A

17L

[1]

一个

0R

–A

17R

[1]

地址 输入

.

ADS

L

[3]

ADS

R

[3]

地址 strobe 输入

. 使用 作 一个 地址 qualifier. 这个 信号 应当 是 asserted 低

为 这 部分 使用 这 externally 有提供的 一个ddress 在 这 地址 管脚 和 为 加载 这个

地址 在 这 burst 地址 计数器.

CE0

L

[3]

CE0

R

[3]

起作用的 低 碎片 使能 输入

.

CE1

L

[3]

CE1

R

[3]

起作用的 高 碎片 使能 输入

.

CLK

L

CLK

R

时钟 信号

. 最大 时钟 输入 比率 是 f

最大值

.

CNTEN

L

[3]

CNTEN

R

[3]

计数器 使能 输入

.

asserting 这个 信号 低 increments 这 burst 地址 计数器 的

它的 各自的 端口 在 各自 rising 边缘 的clk. 这 increment 是 无能 如果 ads

或者 cntrst

是 asserted 低.

CNTRST

L

[3]

CNTRST

R

[3]

计数器 重置 输入

. asserting 这个 信号 低 resets 至 零 这 unmasked portion 的 这

burst 地址 计数器 的 它s 各自的 端口. cntrst

是 不 无能 用 asserting ads或者

CNTEN

.

cnt/msk

L

[3]

cnt/msk

R

[3]

一个

ddress 计数器 掩饰 寄存器 使能 输入

. asserting 这个 信号 低 使能 进入

至 这 掩饰 寄存器. 当 系 高, 这 掩饰 寄存器 是 不 accessible 和 这 地址

计数器 行动 是 使能 为基础 在 the 状态 的 这 计数器 控制 信号.

DQ

0L

–DQ

35L

DQ

0R

–DQ

35R

数据 总线 输入/输出

.

OE

L

OE

R

输出 使能 输入

. 这个 异步的 信号 必须 是 asserted 低 至 使能 这 dq

数据 管脚 在 读 行动.

INT

LINTR

mailbox 中断 标记 输出

.

这 mailbox 准许 communications 在 端口. 这

upper 二 记忆 locations 能 是 使用 为 message passing. int

L

是 asserted 低 当

这 正确的 端口 写 至 这 mailbox location 的 这 left 端口, 和 恶行 对抗. 一个 中断 至 一个

端口 是 deasserted 高 当 它 reads 这 内容 的 它的 mailbox.

CNTINT

L

[3]

CNTINT

R

[3]

计数器 中断 输出

. 这个 管脚 是 asserted 低 当 这 unmasked portion 的 这

计数器 是 incremented 至 所有 “1s.”

r/w

L

r/w

R

读/写 使能 输入

. assert 这个 管脚 低 至 写 至, 或者 高 至 读 从 这 双

端口 记忆 排列.

B

0L

–B

3L

B

0R

–B

3R

字节 选择 输入

. asserting 这些 信号 使能 读 和 写 行动 至 这

相应的 字节 的 这 记忆 排列.

MRST

主控 重置 输入

. mrst是 一个 异步的 输入 信号 和 affects 两个都 端口. asserting

MRST

低 执行 所有 的 这 重置 功能 作 描述 在 这 text. 一个 mrst运作

是 必需的 在 电源-向上.

TMS

jtag 测试 模式 选择 输入

. 它 控制 这 进步 的 jtag tap 状态 机器. 状态

机器 transitions 出现 在 这 rising 边缘 的 tck.

TDI

jtag 测试 数据 输入

. 数据 在 这 tdi 输入 将 是 shifted serially 在 选择 寄存器.

TCK

jtag 测试 时钟 输入

.

TDO

jtag 测试 数据 输出

. tdo transitions 出现 在 这 下落 边缘 的 tck. tdo 是 正常情况下

三-陈述 除了 当 captured 数据 是 shifted 输出 的 这 jtag tap.

V

SS

地面 输入

.

V

DD

电源 输入

.