差别的 时钟 缓存区/驱动器 ddr400-

和 ddr333-一致的

CY28352

Cypress 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文档 #: 38-07371 rev. *c 修订 sept. 02, 2004

特性

• 支持 333-mhz 和 400-mhz ddr sdram

• 60- – 200-mhz 运行 频率

• 阶段-锁 循环 (pll) 时钟 分发 为 翻倍

数据 比率 同步的 dram 产品

• distributes 一个 时钟 输入 至 六 差别的 输出

• 外部 反馈 管脚 fbin 是 使用 至 同步

输出 至 时钟 输入

• 遵从 至 ddri 规格

•spread 知道

™

为 电磁的干扰 (emi)

减少

• 28-管脚 ssop 包装

描述

这个 pll 时钟 缓存区 是 设计 为 2.5-v

DD

和 2.5-av

DD

运作 和 差别的 输出 水平.

这个 设备 是 一个 零 延迟 buffer 那 distributes 一个 时钟 输入

clkin 至 六 差别的 一双s 的 时钟 输出 (clkt[0:5],

clkc[0:5]) 和 一个 反馈 时钟 输出 fbout. 这 时钟

输出 是 控制 用 这 输入 时钟 clkin 和 这

反馈 时钟 fbin.

这 二-线条 串行 总线 能 设置 各自 输出 时钟 一双

(clkt[0:5], clkc[0:5]) 至这 hi-z 状态. 当 av

DD

是

grounded, 这 pll 是 转变 止 和 绕过 为 测试

目的.

这 pll 在 这个 设备 使用 这 输入 时钟 clkin 和 这

反馈 时钟 fbin 至 提供 高-效能, 低-skew,

low–jitter 输出 differential clocks.

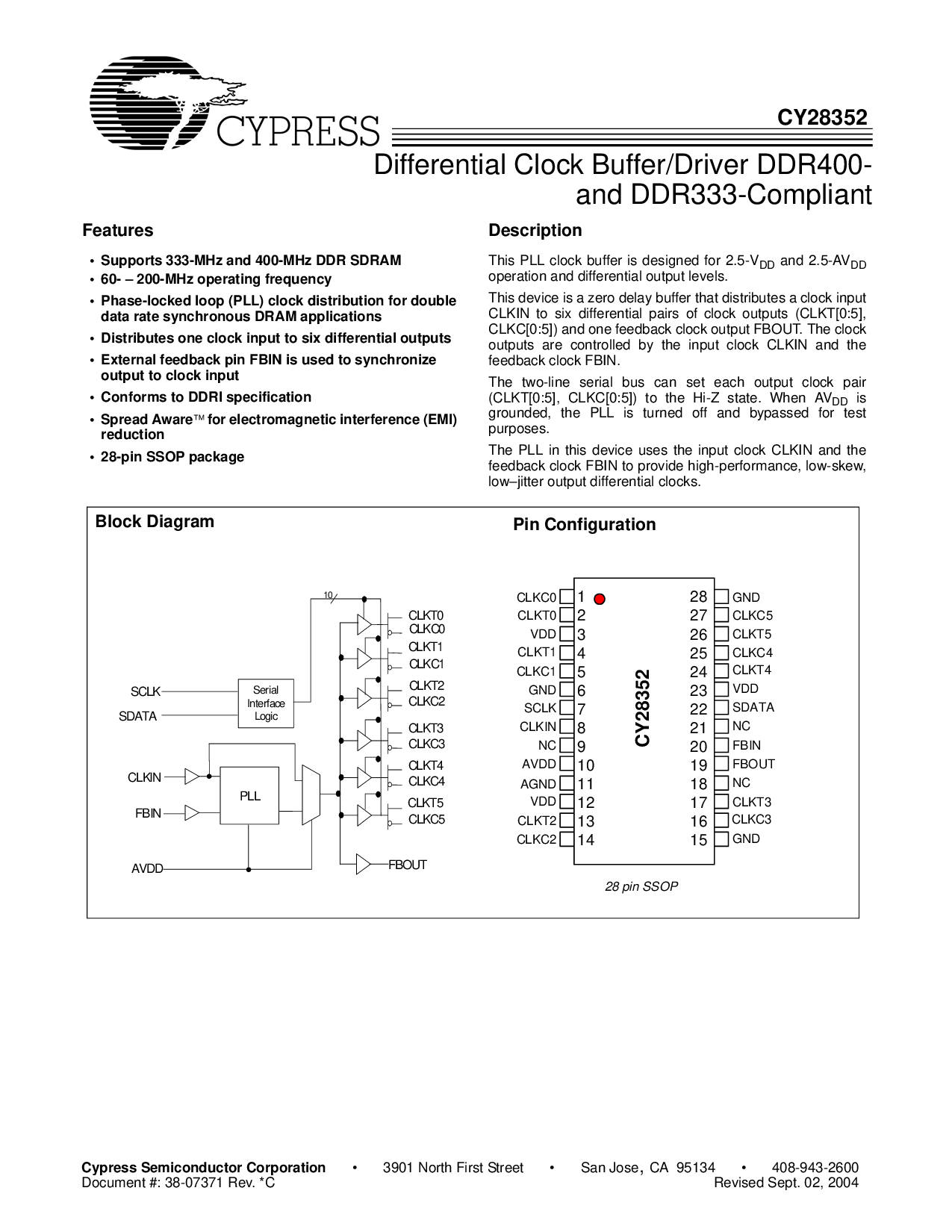

块 图解

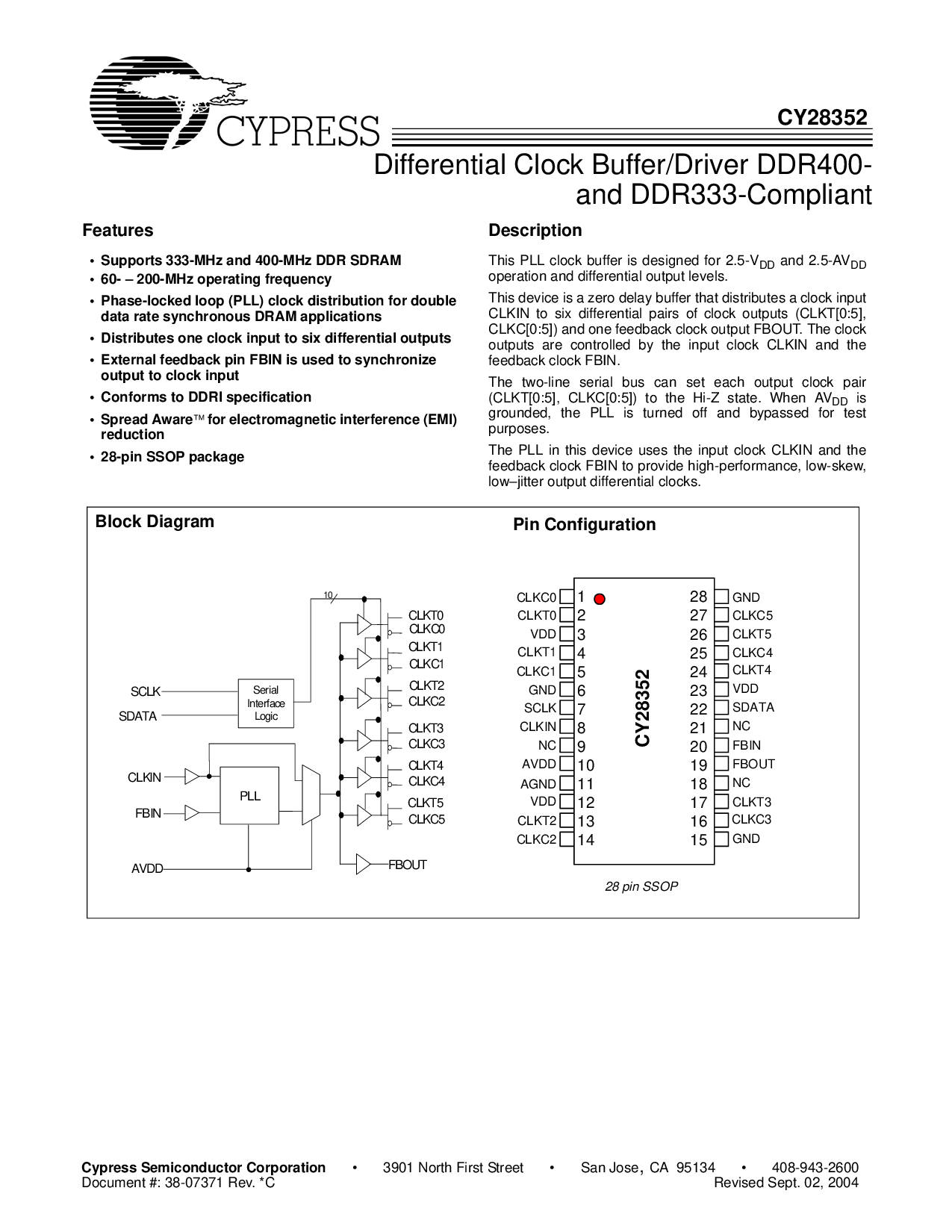

管脚 配置

28 管脚 ssop

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

地

CLKT5

NC

FBOUT

CLKT3

CLKC3

地

NC

FBIN

CLKC5

CLKC4

CLKT4

VDD

SDATA

CLKC0

VDD

CLKIN

AVDD

VDD

CLKT2

CLKC2

AGND

NC

CLKT0

CLKT1

CLKC1

地

SCLK

CY28352

Serial

接口

逻辑

SDATA

SCLK

CLKT0

FBOUT

CLKC0

CLKT1

CLKC1

CLKT2

CLKC2

CLKC3

CLKT3

CLKC4

CLKT4

CLKC5

CLKT5

PLL

FBIN

CLKIN

AVDD

10