adsp-ts101s

rev. b | 页 9 的 44 | 12月 2004

运动 在 125 mhz, 各自 link端口 能 支持 向上 至

250M 字节 每 第二, 为 一个 combined 最大 throughput

的 1g 字节 每 第二.

这 link 端口 提供 一个 optional communications 频道

那 是 有用的 在 multiprocessor 系统 为 implementing 要点

至 要点 interprocessor communications. 产品 能 也

使用 这 link 端口 为 booting.

各自 link 端口 有 它的 自己的 翻倍-缓冲 输入 和 输出

寄存器. 这 dsp’s 核心 能 写直接地 至 一个 link 端口’s trans-

mit 寄存器 和 读 从 一个 receive 寄存器, 或者 这 dma

控制 能 执行 dma transfers 通过 第八 (四

transmit 和 四 receive) 专心致志的 link 端口 dma 途径.

各自 link 端口 有 三 信号s 那 控制 它的 运作.

lxclkout 和 lxclkin 执行 时钟/acknowledge

handshaking. lxdir indicates 这 方向 的 转移 和 是

使用 仅有的 当 buffering 这 lxdat 信号. 一个 例子 appli-

cation 将 是 使用 差别的 低-摆动 缓存区 为 长

twisted-一双 线. lxdat 提供 这 8-位 数据 总线

输入/输出.

产品 能 程序 separate 错误 发现 mechanisms

为 transmit 和 receive 行动 (产品 能 使用 这

checksum mechanism 至 执行 consecutive link 端口

transfers), 这 大小 的 数据 包装ets, 和 这 速 在 这个 字节

是 transmitted.

下面 确实 情况, 这 link端口 接受者 能 initiate 一个

token 转变 至 反转 这 直接ion 的 转移; 这 传输者

变为 这 接受者 和 恶行 对抗.

计时器 和 一般-目的 i/o

这 adsp-ts101s 有 一个 计时器 pin (tmr0e) 那 发生 输出-

放 当 一个 编写程序 计时器 计数器 有 expired. 也, 这

dsp 有 四 可编程序的 一般-目的 i/o 管脚

(flag3–0) 那 能 函数 作 也 单独的 位 输入 或者 输出-

放. 作 输出, 这些 管脚 能 信号 附带的 设备; 作

输入, 它们 能 提供 这 测试 为 conditional branching.

重置 和 booting

这 adsp-ts101s 有 two 水平 的 重置 (看 重置 specifica-

tions在 页 24):

• 电源-向上 reset—after 电源-向上的 这 系统, 和 strap

选项 是 稳固的, 这 重置

管脚 必须 是 asserted (低).

• 正常的 reset—for 任何 resets 下列的 这 电源-向上 重置

sequence, 这 重置

管脚 必须 是 asserted.

这 dsp 能 是 重置 内部(核心 重置) 用 设置 这

swrst 位 在 sqctl. 这 核心 是 重置, 但是 不 这 外部

端口 或者 i/o.

之后 重置, 这 adsp-ts101s has 四 激励 运算tions 为 begin-

ning 运作:

• 激励 从 非易失存储器. 这 dsp defaults 至 非易失存储器 booting

当 这 bms

管脚 strap 选项 是 设置 低. 看strap 管脚

函数 描述 在 页 19.

• 激励 用 一个 外部 主控 (host 或者 另一 adsp-

ts101s). 任何 主控 在 这 cluster 总线 能 激励 这

adsp-ts101s 通过 写 至 它的 内部的 记忆 或者

通过 autodma.

• 激励 用 link 端口. 所有 四receive link dma 途径 是

initialized 之后 重置 至 转移 一个 256-文字 块 至 inter-

nal 记忆 地址 0 至 255, 一个d 至 公布 一个 中断 在

这 终止 的 这 块 (类似的至 ep dma). the correspond-

ing dma 中断 是 set 至 地址 零 (0).

• 非 boot—start 运动 从 一个 外部 记忆. 使用

这 “no boot” 选项, 这 adsp-ts101s 必须 开始 运动

从 一个 外部 记忆, caused 用 asserting 一个 的 这

IRQ3–0

中断 信号.

这 adsp-ts101s 核心 总是 exits 从 重置 在 这 空闲 状态

和 waits 为 一个 中断. 一些的 这 中断 在 这 inter-

rupt vector 表格 是 initialized 和 使能 之后 重置.

低 电源 运作

这 adsp-ts101s 能 enter 一个 low 电源 睡眠 模式 在 这个

它的 核心 做 不 execute instructions, 减少 电源 con-

sumption 至 一个 迷你mum. 这 adsp-ts101s exits 睡眠 模式

当 它 senses 一个 下落边缘 在 任何 的 它的 irq3–0

中断

输入. 这 中断, 如果 使能, 导致 这 adsp-ts101s 至

execute 这 相应的 interrupt 维护 routine. 这个 fea-

ture 是 有用的 为 系统 th在 需要 一个 低 电源 备用物品

模式.

时钟 domains

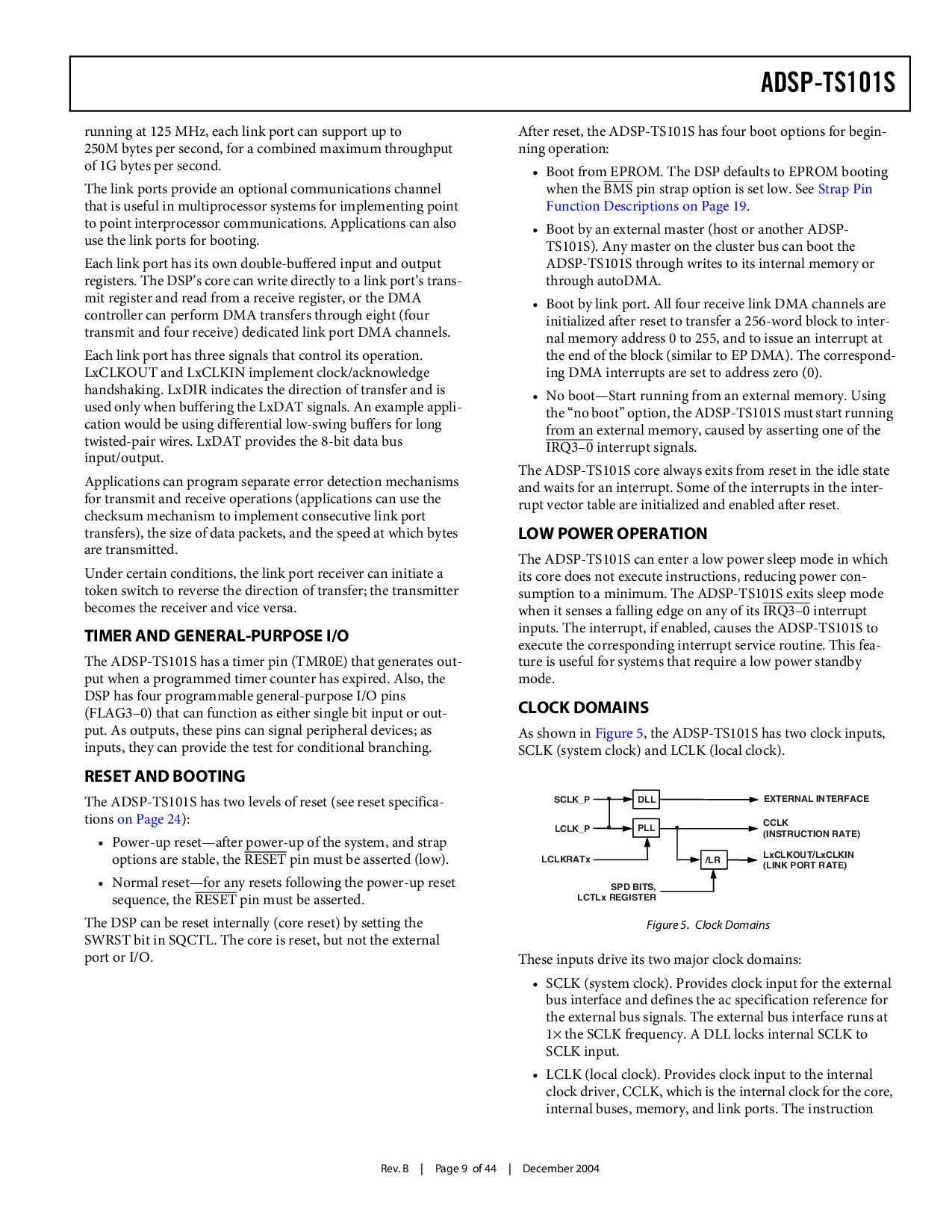

作 显示 在图示 5, 这 adsp-ts101s 有 二 时钟 输入,

sclk (系统 时钟) 和 lclk (local 时钟).

这些 输入 驱动 它的 二 主要的 时钟 domains:

• sclk (系统 时钟). 提供 时钟 输入 为 这 外部

总线 接口 和 定义 这 交流规格 涉及 为

这 外部 总线 信号. 这 外部 总线 接口 runs 在

1

×

这 sclk 频率. 一个 dll locks 内部的 sclk 至

sclk 输入.

• lclk (local 时钟). 提供 时钟 输入 至 这 内部的

时钟 驱动器, cclk, 这个 是 这 内部的 时钟 为 这 核心,

内部的 buses, 记忆, 和link 端口. 这 操作指南

图示 5. 时钟 domains

LCLKRATx

sclk_p

lclk_p

SPD 位,

LCTLx 寄存器

外部 接口

CCLK

(操作指南 比率)

lxclkout/lxclkin

(link 端口 比率)

DLL

DLL

DLL

PLL

DLL

/lr