FM20L08

rev. 1.3

六月 2005 页 2 的 14

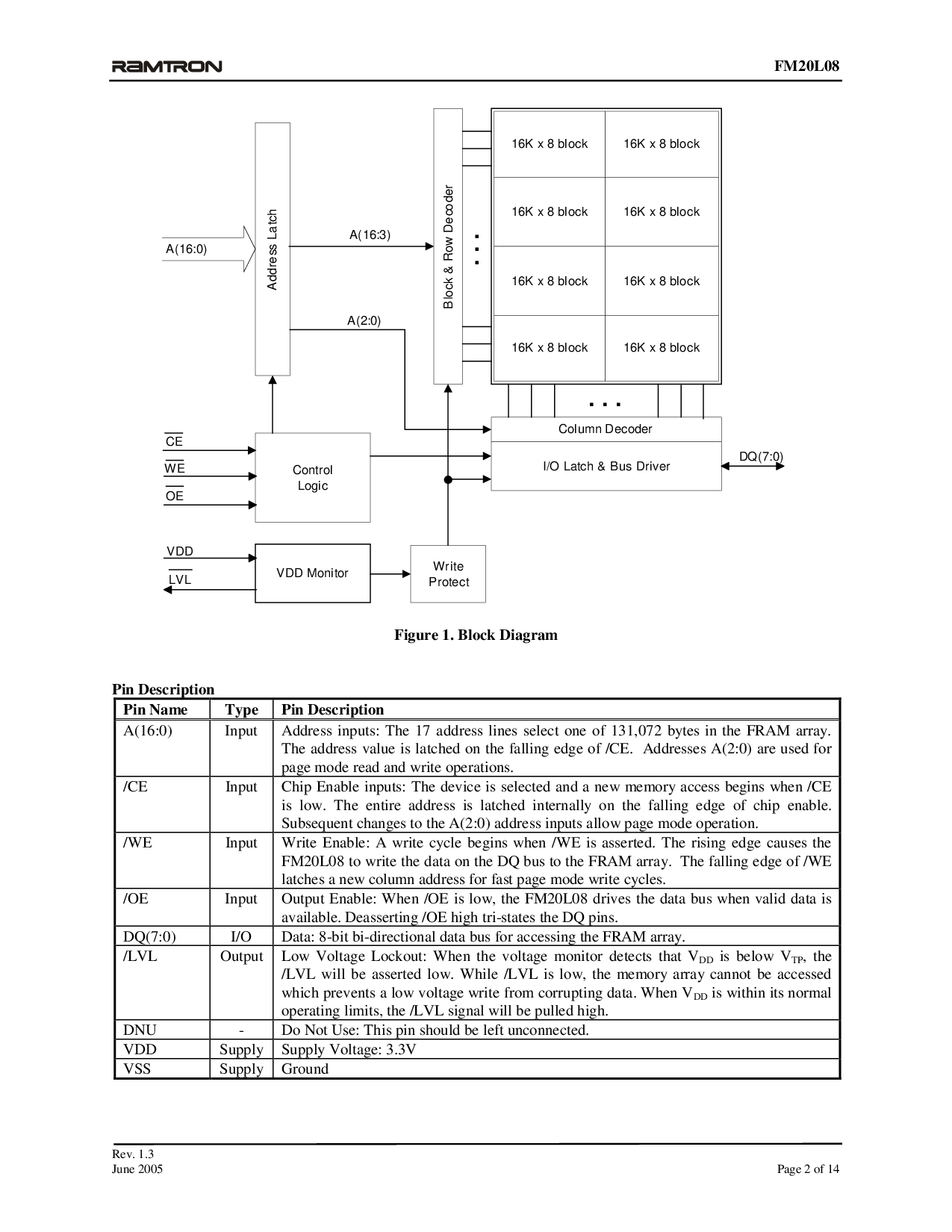

地址 获得

CE

控制

Logic

我们

块 &放大;行 decoder

一个(16:3)

一个(2:0)

i/o latch &放大;B美国Driver

OE

DQ(7:0)

16k x 8 块 16Kx 8 block

16k x 8 块 16Kx 8 block

16k x 8 块 16Kx 8 block

16k x 8 块 16Kx 8 block

vdd 监控

VDD

LVL

一个(16:0)

写

保护

. . .

column 解码器

. . .

图示 1. 块 图解

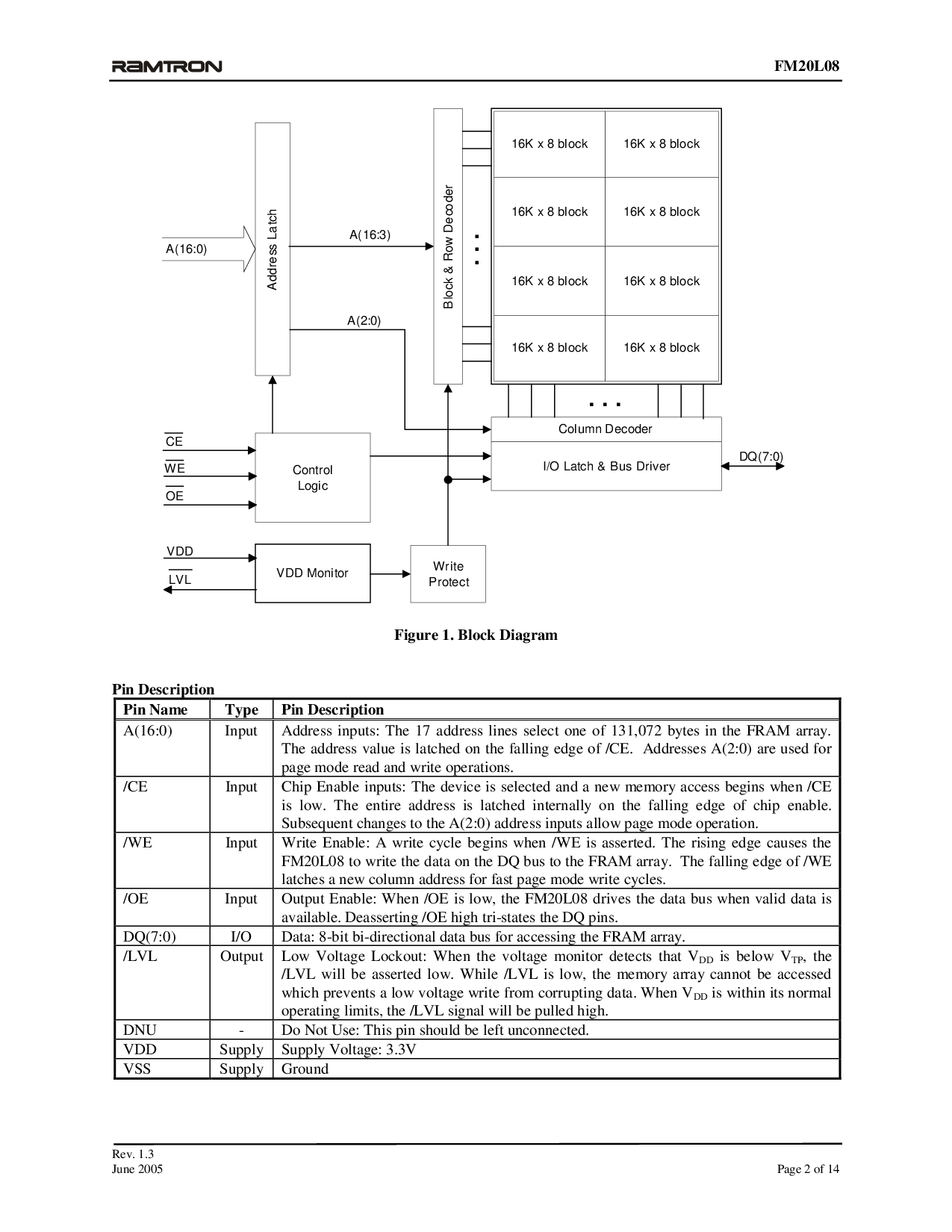

管脚 描述

管脚 名字 类型 管脚 描述

一个(16:0) 输入 地址 输入: 这 17 地址 线条 选择 一个 的 131,072 字节 在 这 fram 排列.

这 地址 值 是 latched 在 这 下落 边缘 的 /ce. 地址 一个(2:0) 是 使用 为

页 模式 读 和 写 行动.

/ce 输入 碎片 使能 输入: 这 设备 是 选择 和 一个 新 记忆 进入 begins 当 /ce

是 低. 这 全部 地址 是 latched 内部 在 这 下落 边缘 的 碎片 使能.

subsequent 改变 至 这 一个(2:0) 地址 输入 准许 页 模式 运作.

/我们 输入 写 使能: 一个 写 循环 begins 当 /我们 是 asserted. 这 rising 边缘 导致 这

fm20l08 至 写 这 数据 在 这 dq 总线 至 这 fram 排列. 这 下落 边缘 的 /我们

latches 一个 新 column 地址 为 快 页 模式 写 循环.

/oe 输入 输出 使能: 当 /oe 是 低, 这 fm20l08 驱动 这 数据 总线 当 有效的 数据 是

有. deasserting /oe 高 触发-states 这 dq 管脚.

dq(7:0) i/o 数据: 8-位 bi-directional 数据 总线 为 accessing 这 fram 排列.

/lvl 输出 低 电压 lockout: 当 这 电压 监控 发现 那 v

DD

是 在下 v

TP

, 这

/lvl 将 是 asserted 低. 当 /lvl 是 低, 这 记忆 排列 不能 是 accessed

这个 阻止 一个 低 电压 写 从 corrupting 数据. 当 v

DD

是 在里面 它的 正常的

运行 限制, 这 /lvl 信号 将 是 牵引的 高.

DNU - 做 不 使用: 这个 管脚 应当 是 left unconnected.

VDD 供应 供应 电压: 3.3v

vss 供应 地面