26

初步的

7-26

ql3012 - pasic 3 fpga

TM

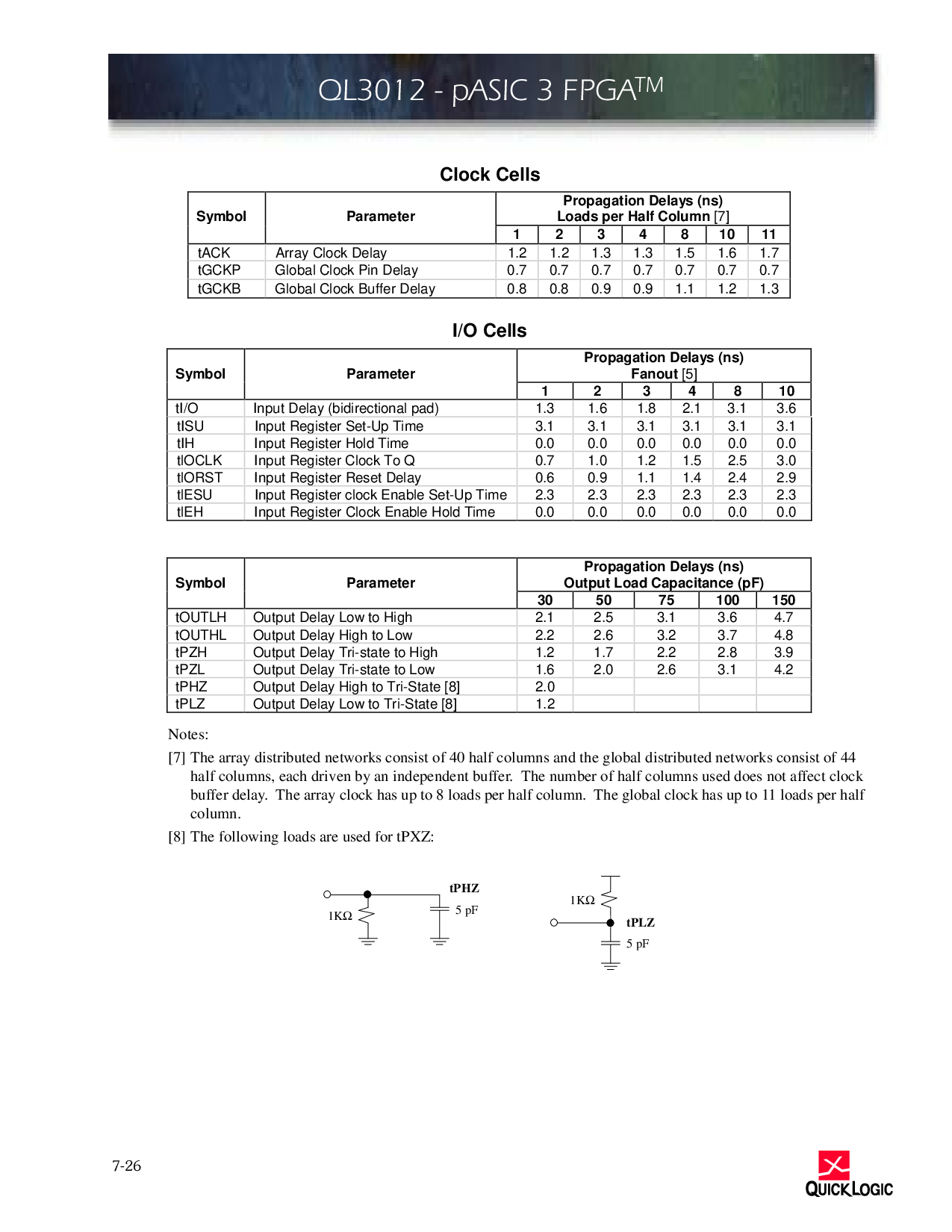

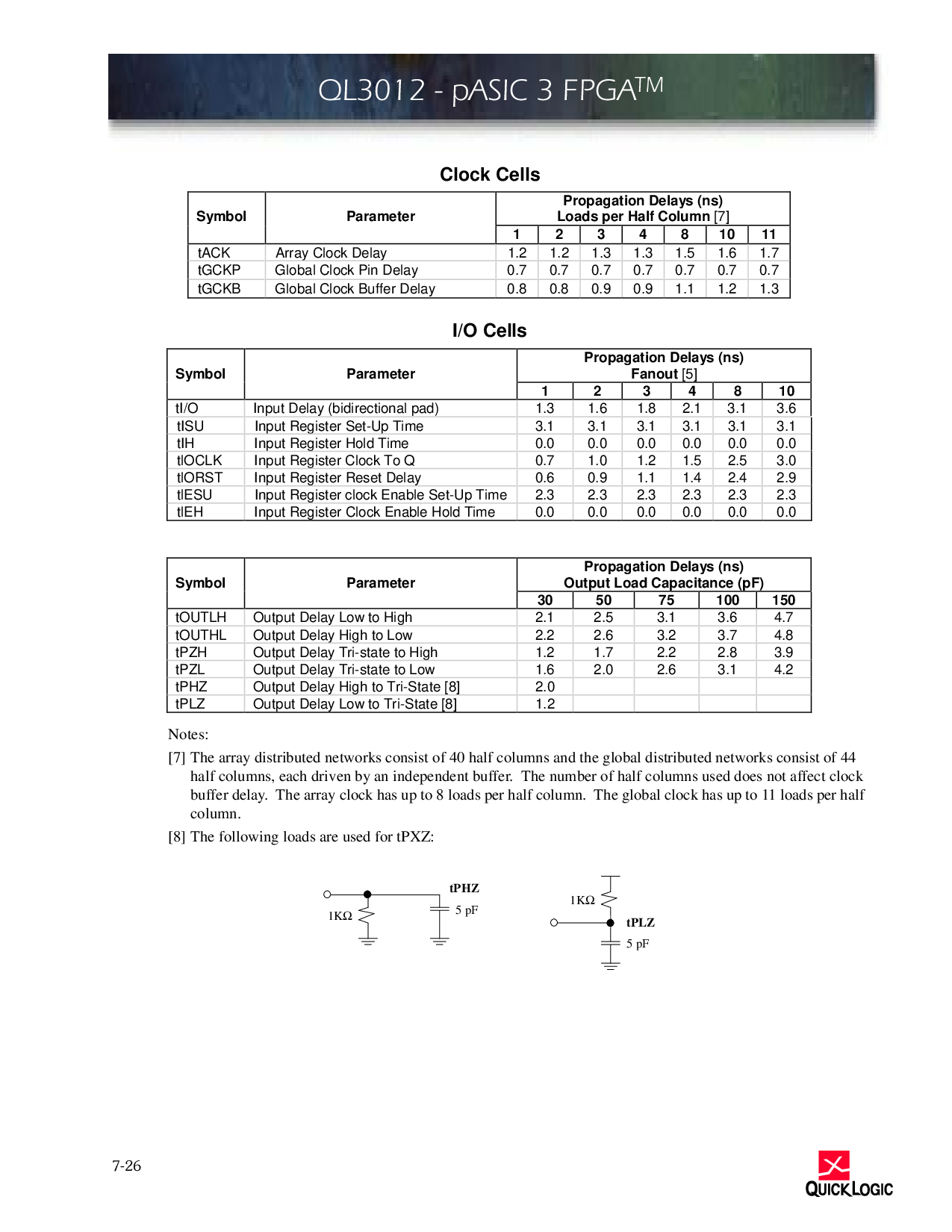

时钟 cells

i/o cells

注释:

[7] 这 排列 distributed 网络 组成 的 40 half columns 和 这 global distributed 网络 组成 的 44

half columns, 各自 驱动 用 一个 独立 缓存区. 这 号码 的 half columns 使用 做 不 影响 时钟

缓存区 延迟. 这 排列 时钟 有 向上 至 8 负载 每 half column. 这 global 时钟 有 向上 至 11 负载 每 half

column.

[8] 这 下列的 负载 是 使用 为 tpxz:

标识 参数

传播 延迟 (ns)

负载 每 half column

[7]

123481011

tACK 排列 时钟 延迟 1.2 1.2 1.3 1.3 1.5 1.6 1.7

tGCKP global 时钟 管脚 延迟 0.7 0.7 0.7 0.7 0.7 0.7 0.7

tGCKB global 时钟 缓存区 延迟 0.8 0.8 0.9 0.9 1.1 1.2 1.3

标识 参数

传播 延迟 (ns)

输出

[5]

1234810

德州仪器/o 输入 延迟 (双向的 垫子) 1.3 1.6 1.8 2.1 3.1 3.6

tISU 输入 寄存器 设置-向上 时间 3.1 3.1 3.1 3.1 3.1 3.1

tIH 输入 寄存器 支撑 时间 0.0 0.0 0.0 0.0 0.0 0.0

tlOCLK 输入 寄存器 时钟 至 q 0.7 1.0 1.2 1.5 2.5 3.0

tlORST 输入 寄存器 重置 延迟 0.6 0.9 1.1 1.4 2.4 2.9

tlESU 输入 寄存器 时钟 使能 设置-向上 时间 2.3 2.3 2.3 2.3 2.3 2.3

tlEH 输入 寄存器 时钟 使能 支撑 时间 0.0 0.0 0.0 0.0 0.0 0.0

标识 参数

传播 延迟 (ns)

输出 加载 电容 (pf)

30 50 75 100 150

tOUTLH 输出 延迟 低 至 高 2.1 2.5 3.1 3.6 4.7

tOUTHL 输出 延迟 高 至 低 2.2 2.6 3.2 3.7 4.8

tPZH 输出 延迟 触发-状态 至 高 1.2 1.7 2.2 2.8 3.9

tPZL 输出 延迟 触发-状态 至 低 1.6 2.0 2.6 3.1 4.2

tPHZ 输出 延迟 高 至 触发-状态 [8] 2.0

tPLZ 输出 延迟 低 至 触发-状态 [8] 1.2

5 pf

1K

Ω

5 pf

1K

Ω

tPHZ

tPLZ