AD7226

rev. 一个

–7–

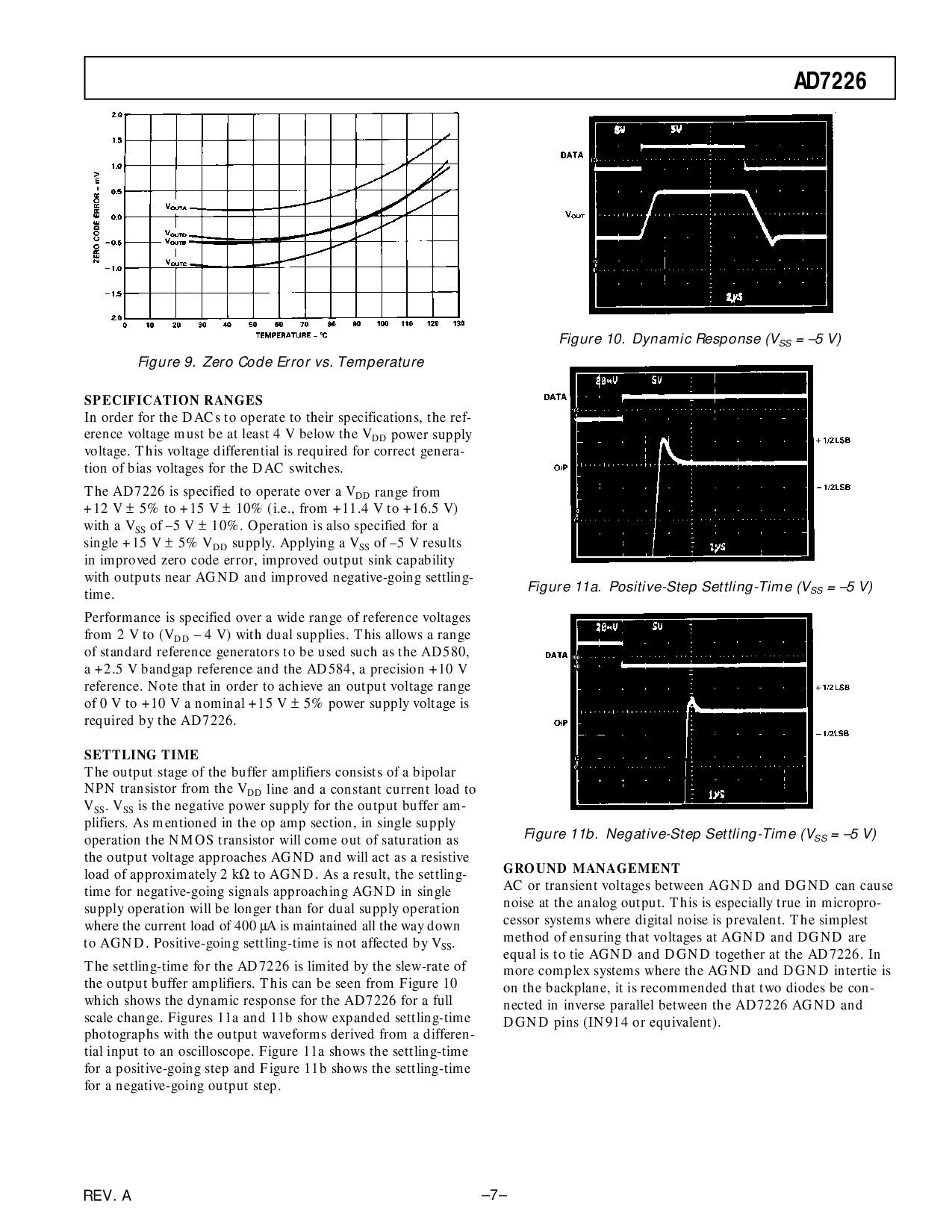

图示 10. 动态 回馈 (v

SS

= –5 v)

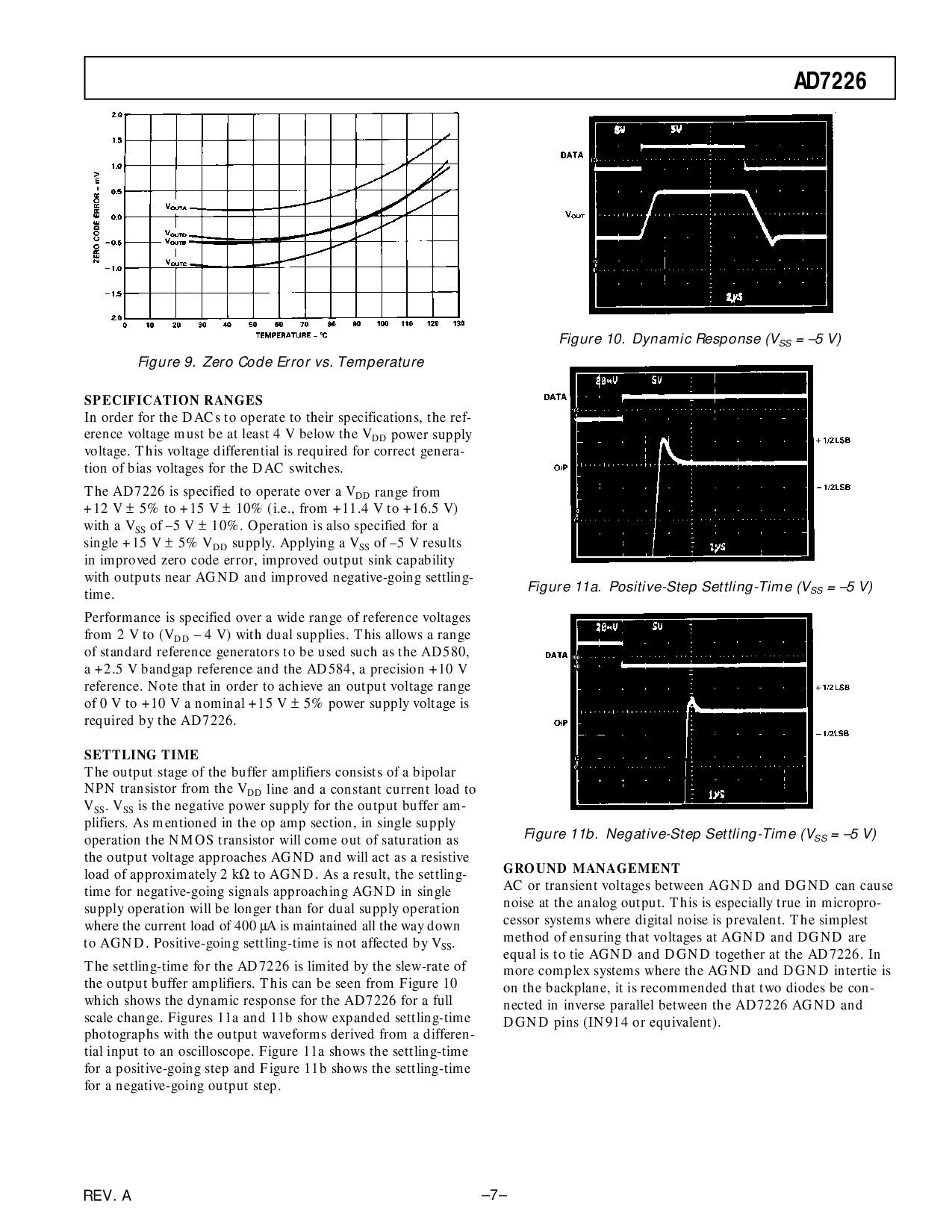

图示 11a. 积极的-步伐 安排好-时间 (v

SS

= –5 v)

图示 11b. 负的-步伐 安排好-时间 (v

SS

= –5 v)

地面 管理

交流 或者 瞬时 电压 在 agnd 和 dgnd 能 导致

噪音 在 这 相似物 输出. 这个 是 特别 真实 在 micropro-

cessor 系统 在哪里 数字的 噪音 是 prevalent. 这 simplest

方法 的 ensuring 那 电压 在 agnd 和 dgnd 是

equal 是 至 系 agnd 和 dgnd 一起 在 这 ad7226. 在

更多 complex 系统 在哪里 这 agnd 和 dgnd intertie 是

在 这 backplane, 它 是 推荐 那 二 二极管 是 con-

nected 在 inverse 并行的 在 这 ad7226 agnd 和

dgnd 管脚 (in914 或者 相等的).

图示 9. 零 代号 错误 vs. 温度

规格 范围

在 顺序 为 这 dacs 至 运作 至 它们的 规格, 这 ref-

erence 电压 必须 是 在 least 4 v 在下 这 v

DD

电源 供应

电压. 这个 电压 差别的 是 必需的 为 准确无误的 genera-

tion 的 偏差 电压 为 这 dac switches.

这 ad7226 是 指定 至 运作 在 一个 v

DD

范围 从

+12 v

±

5% 至 +15 v

±

10% (i.e., 从 +11.4 v 至 +16.5 v)

和 一个 v

SS

的 –5 v

±

10%. 运作 是 也 指定 为 一个

单独的 +15 v

±

5% v

DD

供应. 应用 一个 v

SS

的 –5 v 结果

在 改进 零 代号 错误, 改进 输出 下沉 能力

和 输出 near agnd 和 改进 负的-going 安排好-

时间.

效能 是 指定 在 一个 宽 范围 的 涉及 电压

从 2 v 至 (v

DD

– 4 v) 和 双 供应. 这个 准许 一个 范围

的 标准 涉及 发生器 至 是 使用 此类 作 这 ad580,

一个 +2.5 v bandgap 涉及 和 这 ad584, 一个 精确 +10 v

涉及. 便条 那 在 顺序 至 达到 一个 输出 电压 范围

的 0 v 至 +10 v 一个 名义上的 +15 v

±

5% 电源 供应 电压 是

必需的 用 这 ad7226.

安排好 时间

这 输出 平台 的 这 缓存区 放大器 组成 的 一个 双极

npn 晶体管 从 这 v

DD

线条 和 一个 常量 电流 加载 至

V

SS

. v

SS

是 这 负的 电源 供应 为 这 输出 缓存区 am-

plifiers. 作 提到 在 这 运算 放大 部分, 在 单独的 供应

运作 这 nmos 晶体管 将 来到 输出 的 饱和 作

这 输出 电压 approaches agnd 和 将 act 作 一个 resistive

加载 的 大概 2 k

Ω

至 agnd. 作 一个 结果, 这 安排好-

时间 为 负的-going 信号 approaching agnd 在 单独的

供应 运作 将 是 变长 比 为 双 供应 运作

在哪里 这 电流 加载 的 400

µ

一个 是 maintained 所有 这 方法向下

至 agnd. 积极的-going 安排好-时间 是 不 影响 用 v

SS

.

这 安排好-时间 为 这 ad7226 是 限制 用 这 回转-比率 的

这 输出 缓存区 放大器. 这个 能 是 seen 从 图示 10

这个 显示 这 动态 回馈 为 这 ad7226 为 一个 全部

规模 改变. 计算数量 11a 和 11b 显示 expanded 安排好-时间

photographs 和 这 输出 波形 获得 从 一个 differen-

tial 输入 至 一个 oscilloscope. 图示 11a 显示 这 安排好-时间

为 一个 积极的-going 步伐 和 图示 11b 显示 这 安排好-时间

为 一个 负的-going 输出 步伐.