adg411/adg412/adg413

rev. 一个–6–

频率 – hz

120

100

40

100 10M1k

止 分开 – db

10k 100k 1M

80

60

V

DD

= +15v

V

SS

= –15v

V

L

= +5v

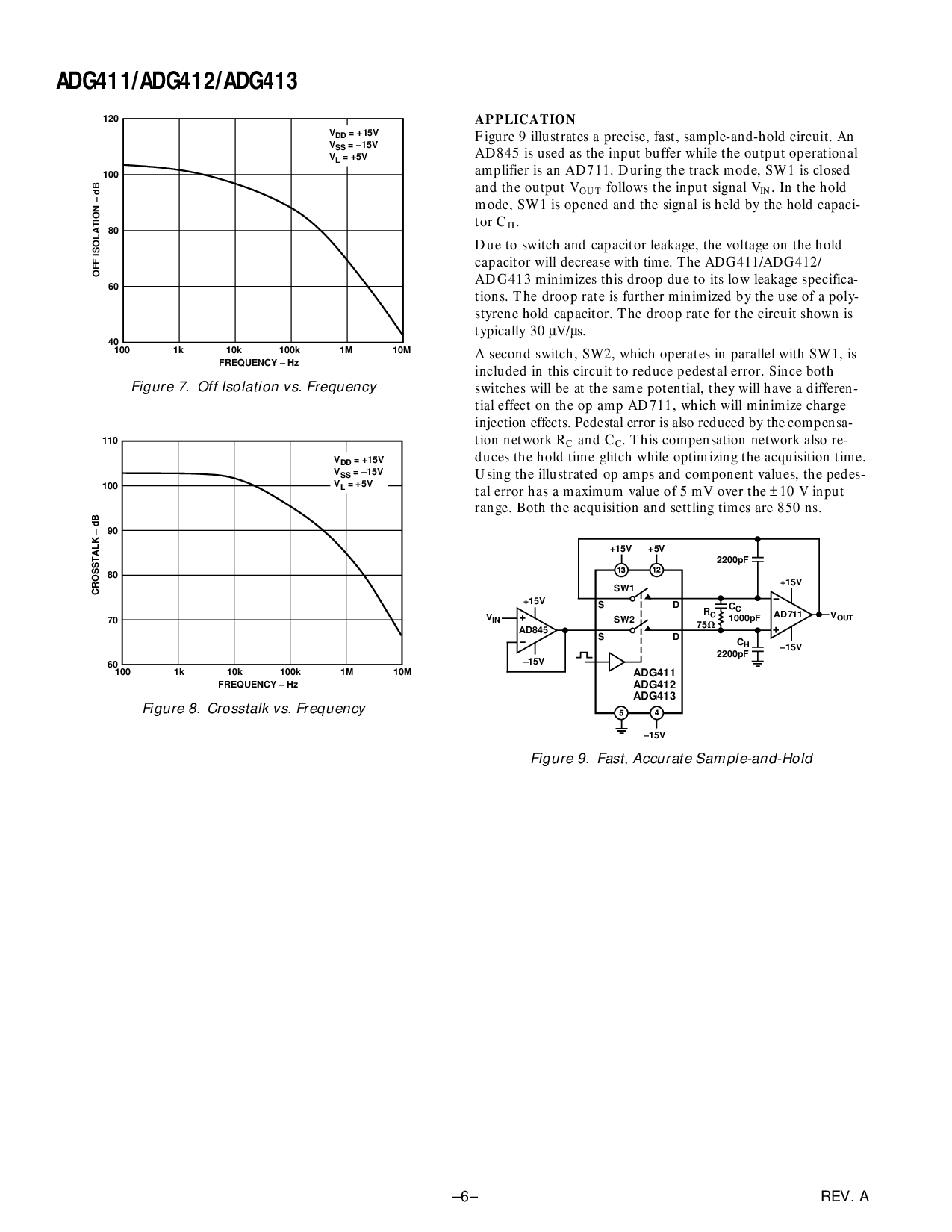

图示 7. 止 分开 vs. 频率

频率 – hz

110

100

60

100 10M1k

串扰 – db

10k 100k 1M

90

80

70

V

DD

= +15v

V

SS

= –15v

V

L

= +5v

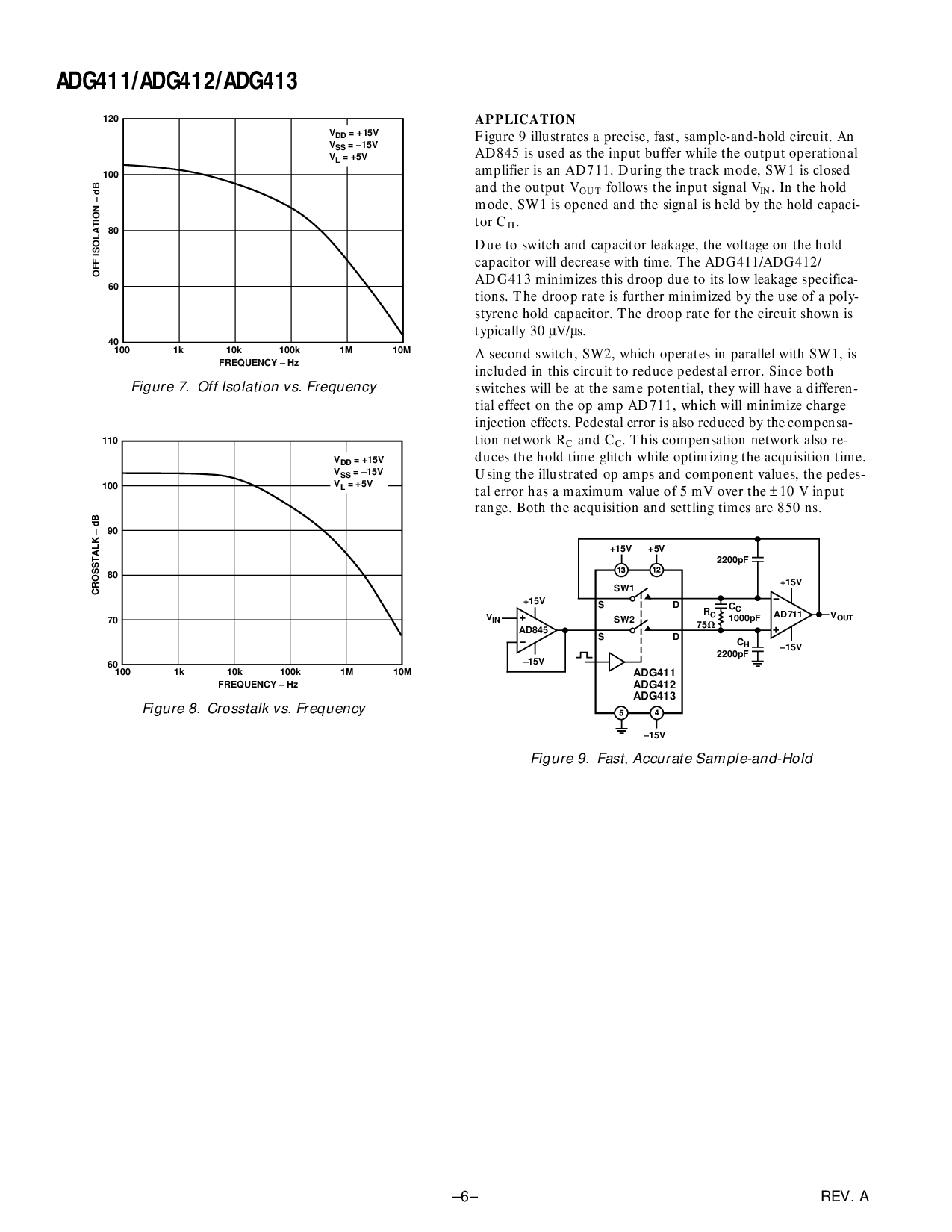

图示 8. 串扰 vs. 频率

应用

图示 9 illustrates 一个 准确的, 快, 样本-和-支撑 电路. 一个

ad845 是 使用 作 这 输入 缓存区 当 这 输出 运算的

放大器 是 一个 ad711. 在 这 追踪 模式, sw1 是 关闭

和 这 输出 v

输出

跟随 这 输入 信号 v

在

. 在 这 支撑

模式, sw1 是 opened 和 这 信号 是 使保持 用 这 支撑 capaci-

tor c

H

.

预定的 至 转变 和 电容 泄漏, 这 电压 在 这 支撑

电容 将 decrease 和 时间. 这 adg411/adg412/

adg413 降低 这个 droop 预定的 至 它的 低 泄漏 specifica-

tions. 这 droop 比率 是 更远 使减少到最低限度 用 这 使用 的 一个 poly-

styrene 支撑 电容. 这 droop 比率 为 这 电路 显示 是

典型地 30

µ

v/

µ

s.

一个 第二 转变, sw2, 这个 运作 在 并行的 和 sw1, 是

包含 在 这个 电路 至 减少 pedestal 错误. 自从 两个都

switches 将 是 在 这 一样 潜在的, 它们 将 有 一个 differen-

tial 效应 在 这 运算 放大 ad711, 这个 将 降低 承担

injection 影响. pedestal 错误 是 也 减少 用 这compensa-

tion 网络 r

C

和 c

C

. 这个 补偿 网络 也 re-

duces 这 支撑 时间 glitch 当 optimizing 这 acquisition 时间.

使用 这 illustrated 运算 放大器 和 组件 值, 这 pedes-

tal 错误 有 一个 最大 值 的 5 mv 在 这

±

10 v 输入

范围. 两个都 这 acquisition 和 安排好 时间 是 850 ns.

+15V

–15V

2200pF

R

C

75

C

C

1000pF

C

H

2200pF

V

输出

ADG411

ADG412

ADG413

SW2

SW1

S

S

D

D

+15V +5V

–15V

AD845

+15V

–15V

V

在

AD711

图示 9. 快, 精确 样本-和-支撑