®

5

ads1212, 1213

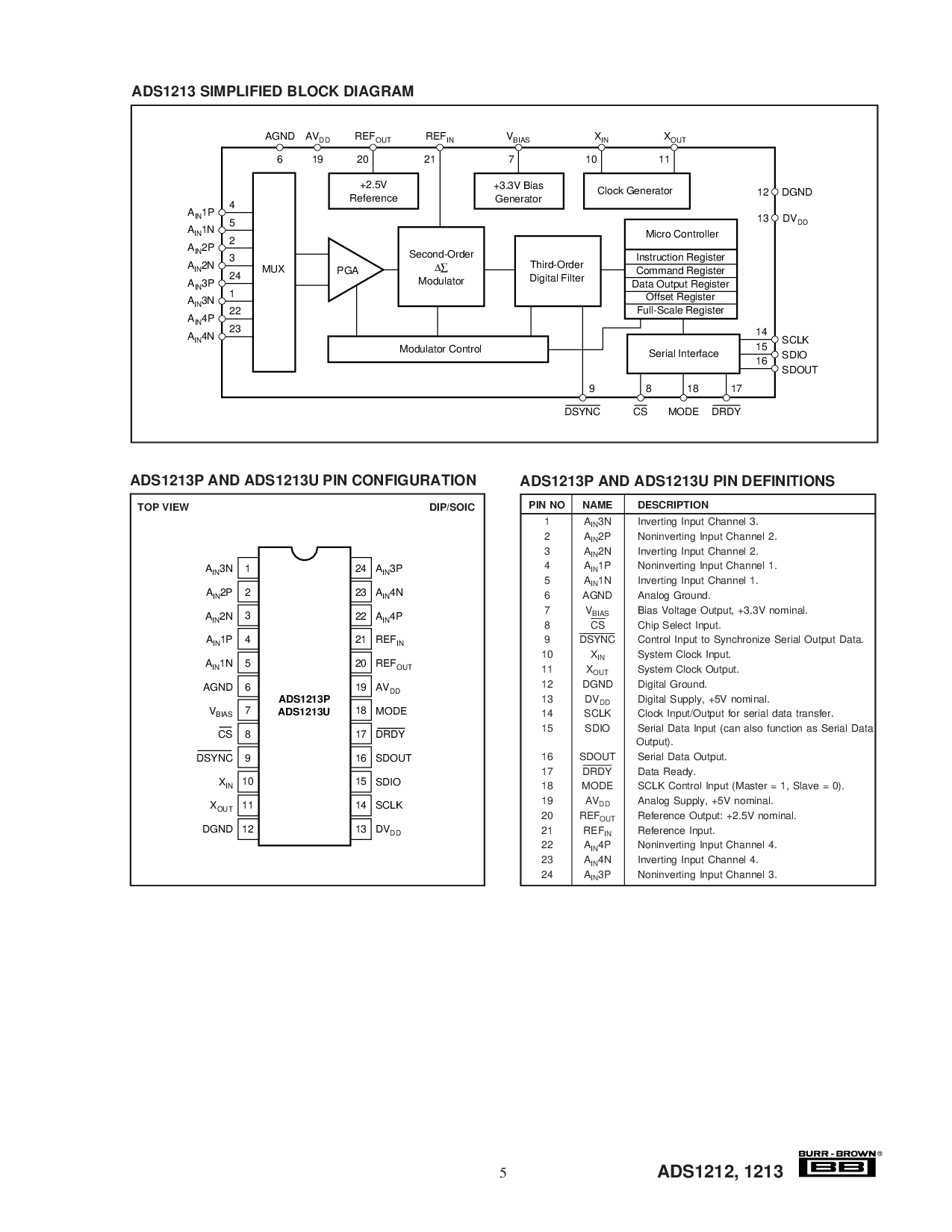

PGA

+2.5v

涉及

+3.3v 偏差

发生器

时钟 发生器

串行 接口

第二-顺序

∆∑

Modulator

第三-顺序

数字的 过滤

modulator 控制

14

12

13

15

16

AGND AV

DD

REF

输出

REF

在

V

偏差

X

在

X

输出

6 19 20 21 7 10 11

98 1718

DSYNC CS DRDYMODE

SCLK

DGND

DV

DD

SDIO

SDOUT

4

5

2

3

24

1

22

23

MUX

一个

在

1P

一个

在

1N

一个

在

2P

一个

在

2N

一个

在

3P

一个

在

3N

一个

在

4P

一个

在

4N

操作指南 寄存器

command 寄存器

数据 输出 寄存器

补偿 寄存器

全部-规模 寄存器

微观的 控制

ads1213 simplified 块 图解

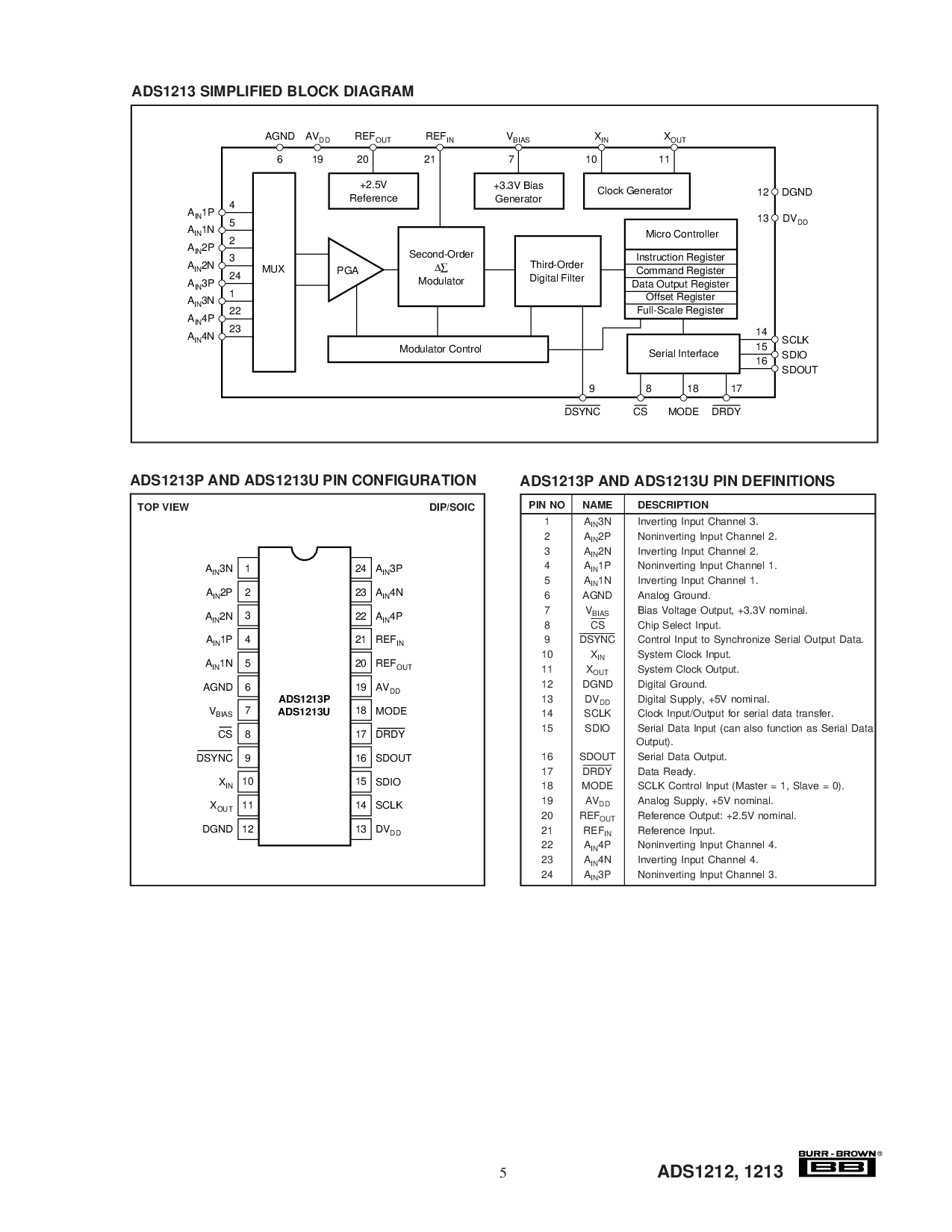

ads1213p 和 ads1213u 管脚 定义

顶 视图 插件/soic

ads1213p 和 ads1213u 管脚 配置

管脚 非 名字 描述

1A

在

3N 反相的 输入 频道 3.

2A

在

2P 同相 输入 频道 2.

3A

在

2N 反相的 输入 频道 2.

4A

在

1P 同相 输入 频道 1.

5A

在

1N 反相的 输入 频道 1.

6 AGND 相似物 地面.

7V

偏差

偏差 电压 输出, +3.3v 名义上的.

8 CS 碎片 选择 输入.

9 DSYNC 控制 输入 至 同步 串行 输出 数据.

10 X

在

系统 时钟 输入.

11 X

输出

系统 时钟 输出.

12 DGND 数字的 地面.

13 DV

DD

数字的 供应, +5v 名义上的.

14 SCLK 时钟 输入/输出 为 串行 数据 转移.

15 SDIO 串行 数据 输入 (能 也 函数 作 串行 数据

输出).

16 SDOUT 串行 数据 输出.

17 DRDY 数据 准备好.

18 模式 sclk 控制 输入 (主控 = 1, 从动装置 = 0).

19 AV

DD

相似物 供应, +5v 名义上的.

20 REF

输出

涉及 输出: +2.5v 名义上的.

21 REF

在

涉及 输入.

22 一个

在

4P 同相 输入 频道 4.

23 一个

在

4N 反相的 输入 频道 4.

24 一个

在

3P 同相 输入 频道 3.

ADS1213P

ADS1213U

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

一个

在

3N

一个

在

2P

一个

在

2N

一个

在

1P

一个

在

1N

AGND

V

偏差

CS

DSYNC

X

在

X

输出

DGND

一个

在

3P

一个

在

4N

一个

在

4P

REF

在

REF

输出

AV

DD

模式

DRDY

SDOUT

SDIO

SCLK

DV

DD