40mx 和 42mx fpga 家庭

v6.0 1-9

固定 电容 数值 用于 mx fpgas (pf)

测试一下 电路 和 silicon explorer 二 探头

mx 设备 包含 探测 电路 那 提供 已建成-

入点 访问权限 至 每 节点 入点 一个设计, 通过 这 使用 的 硅

explorer 二. 硅 explorer 二 是 一个 综合 硬件

和 软件 解决方案 那, 入点 连接词 与 这

设计师 软件, 允许 用户 至 检查 任何 的 这

内部 nets 的 这 设备 同时 它 是 操作 入点 一个

原型设计 或 一个 生产 系统. 这 用户 可以 探头

进入 一个 mx 设备 无变化 这 放置位置 和

路由 的 这 设计 和 无 使用 任何 附加

资源. 硅 explorer 二's 非侵入性 方法 是否

不 改变 计时 或 正在加载 效果, 因此 缩短 这

调试 循环 和 提供 一个 真 表示法 的 这

设备 下 实际 功能 情况.

硅 explorer 二 样品 数据 在 100 mhz

(异步) 或 66 mhz (syn时间). 硅 explorer

二 附件 至 一个 pc's standard com 港口, 车削 这 pc

进入 一个 完全 功能 18-频道 逻辑 分析仪. 硅

explorer 二 允许 设计师 至 完成 这 设计

验证 流程 在 他们的 desks 和 减少

验证 时间 从 几个 小时数 按 循环 至 一个 很少

秒.

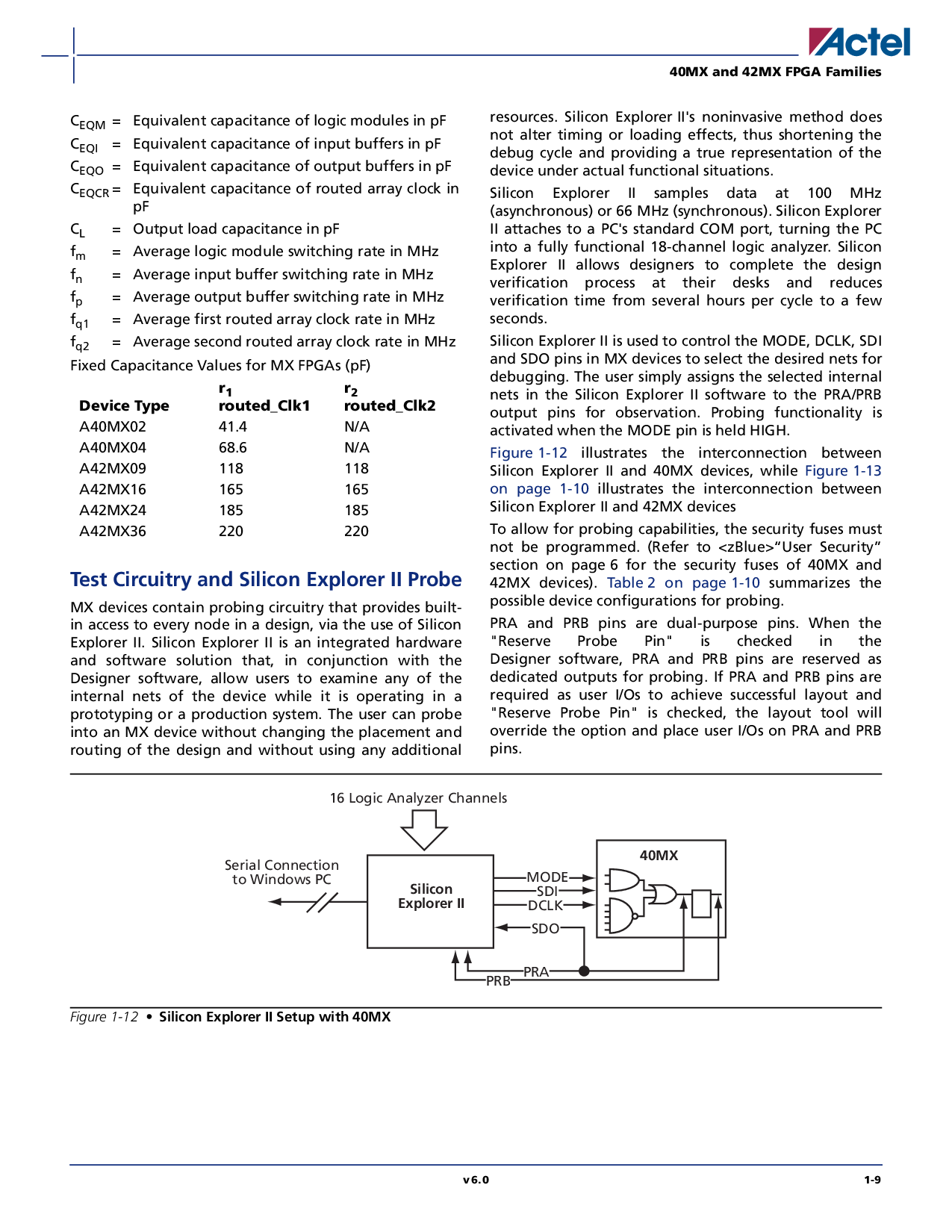

硅 explorer 二 是 已使用 至 控制 这 模式, dclk, sdi

和 sdo 针脚 入点 mx 设备 至 选择 这 需要 nets 用于

调试. 这 用户 简单地分配 这 已选择 内部

nets 入点 这 硅 explorer二 软件 至 这 pra/prb

输出 针脚 用于 观察. 探测 功能 是

已激活 当 这 模式 管脚 是 持有 高.

图 1-12说明 这 互连 之间

硅 explorer 二 和 40mx 设备, 同时图 1-13

开启 第页 1-10说明 这 互连 之间

硅 explorer 二 和 42mx 设备

至 允许 用于 探测 能力ies, 这 安全 保险丝 必须

不 是 编程. (参考 至 &指示灯;zblue>“user security”

截面 开启 第页 6 用于 这 安全 保险丝 的 40mx 和

42mx 设备).表 2 开启 第页 1-10总结 这

可能 设备 配置urations 用于 探测.

pra 和 prb 针脚 是 双-目的 针脚. 当 这

"储备金 探头 管脚" 是 已检查 入点 这

设计师 软件, pra 和 prb 针脚 是 保留 作为

专用 产出 用于 探测. 如果 pra 和 prb 针脚 是

必填项 作为 用户 我/操作系统 至 交流电hieve 成功 布局 和

"储备金 探头 管脚" 是 checked, 这 布局 工具 将

超控 这 选项 和 place 用户 我/操作系统 开启 pra 和 prb

针脚.

c

EQM

= 等效 电容 的 逻辑 模块 入点 pf

c

EQI

= 等效 电容 的 输入 缓冲区 入点 pf

c

EQO

= 等效 电容 的 输出 缓冲区 入点 pf

c

EQCR

= 等效 电容 的 已布线 阵列 时钟 入点

pf

c

l

= 输出 荷载 电容 入点 pf

f

m

= 平均值 逻辑 模块 开关 费率 入点 mhz

f

n

= 平均值 输入 缓冲区 开关 费率 入点 mhz

f

p

= 平均值 输出 缓冲区 开关 费率 入点 mhz

f

q1

= 平均值 第一 已布线 阵列 时钟 费率 入点 mhz

f

q2

= 平均值 第二 已布线 阵列 时钟 费率 入点 mhz

设备 类型

右

1

已布线_clk1

右

2

已布线_clk2

A40MX02 41.4 n/一个

A40MX04 68.6 n/一个

A42MX09 118 118

A42MX16 165 165

A42MX24 185 185

A42MX36 220 220

图 1-12 •

硅 explorer 二 设置 与 40mx

40MX

硅

explorer 二

PRA

PRB

SDO

DCLK

SDI

模式

串行 连接

至 窗户 pc

16 逻辑 分析仪 频道