40mx 和 42mx fpga families

v6.0 1-3

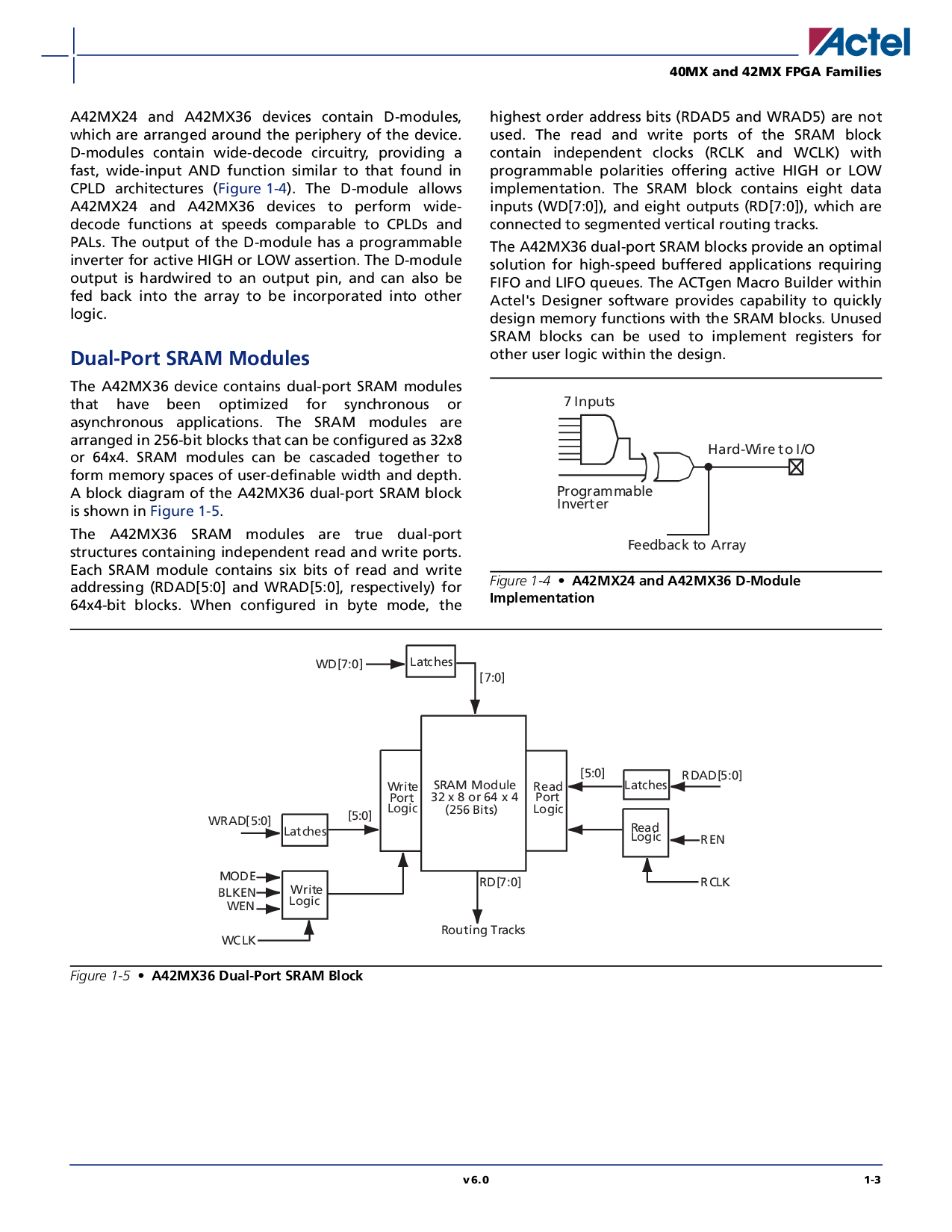

a42mx24 和 a42mx36 devices 包含 d-modules,

这个 是 arranged 周围 the periphery 的 这 设备.

d-modules 包含 宽-decode 电路系统, 供应 一个

快, 宽-输入 和 函数 类似的 至 那 建立 在

cpld architectures (图示 1-4). 这 d-单元 准许

a42mx24 和 a42mx36 设备 至 执行 宽-

decode 功能 在 speedscomparable 至 cplds 和

pals. 这 输出 的 这 d-单元 有 一个 可编程序的

反相器 为 起作用的 高 或者 低 assertion. 这 d-单元

输出 是 hardwired 至 一个 输出 管脚, 和 能 也 是

喂养 后面的 在 这 排列 至 是 组成公司的 在 其它

逻辑.

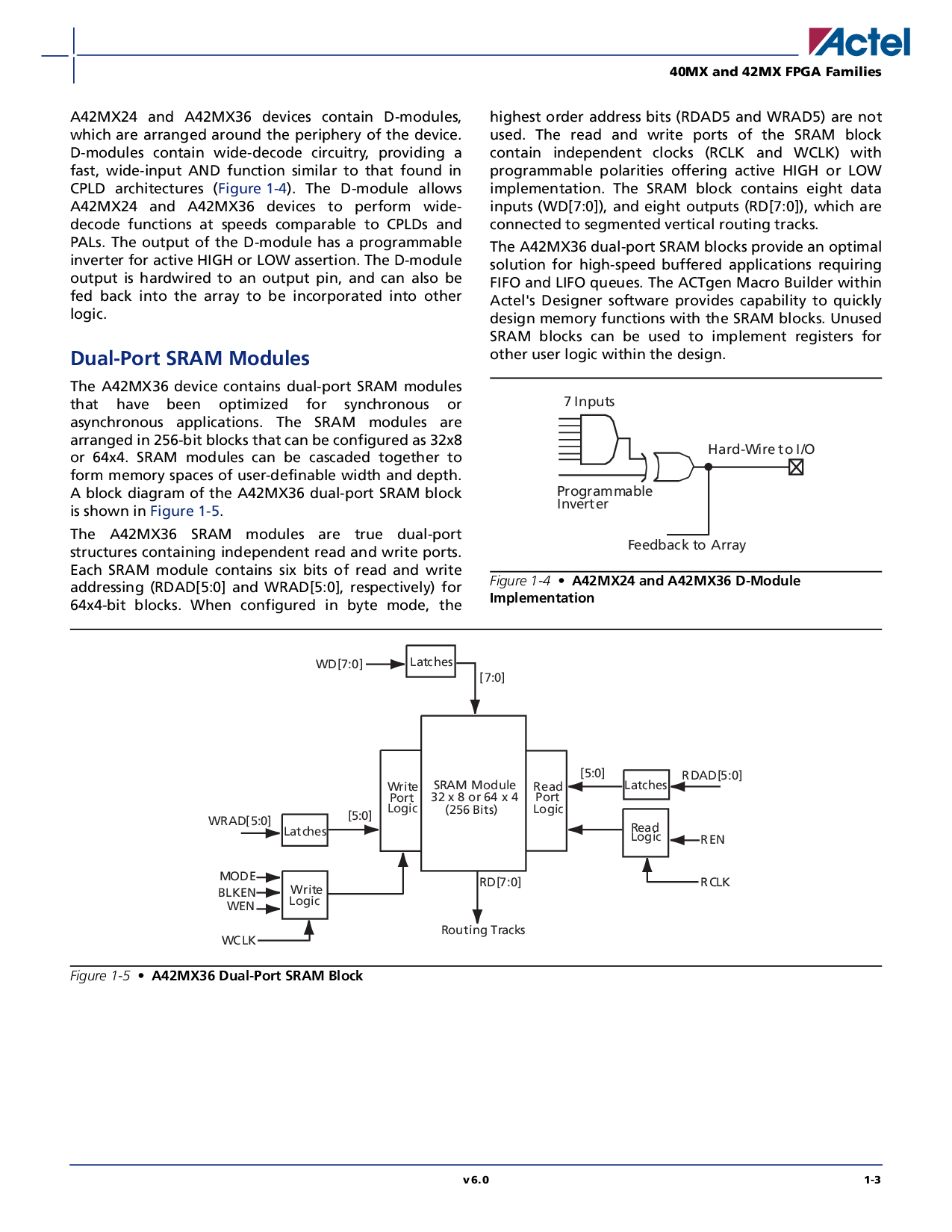

双-端口 sram modules

这 a42mx36 设备 包含双-端口 sram modules

那 有 被 优化 为 同步的 或者

异步的 产品. 这 sram modules 是

arranged 在 256-位 blocks 那 能 是 配置 作 32x8

或者 64x4. sram modules 能 是 倾泻 一起 至

表格 记忆 spaces 的 用户-definable 宽度 和 depth.

一个 块 图解 的 这 a42mx36 双-端口 sram 块

是 显示 在图示 1-5.

这 a42mx36 sram 单元s 是 真实 双-端口

结构 containing 独立 读 和 写 端口.

各自 sram 单元 包含 六 位 的 读 和 写

寻址 (rdad[5:0] 和 wrad[5:0], 各自) 为

64x4-位 blocks. 当 configured 在 字节 模式, 这

最高的 顺序 地址 位 (rdad5 和 wrad5) 是 不

使用. 这 读 和 写端口 的 这 sram 块

包含 独立 clocks (rclk 和 wclk) 和

可编程序的 polarities offering 起作用的 高 或者 低

implementation. 这 sram块 包含 第八 数据

输入 (wd[7:0]), 和 第八输出 (rd[7:0]), 这个 是

连接 至 segmented vertical routing 轨道.

这 a42mx36 双-端口 sram blocks 提供 一个 最优的

解决方案 为 高-速 缓冲 产品 需要

先进先出 和 lifo queues. 这actgen macro builder 在里面

actel's 设计者 软件 提供 能力 至 quickly

设计 记忆 功能 和 这 sram blocks. unused

sram blocks 能 是 使用 至 执行 寄存器 为

其它 用户 逻辑 在里面 这 设计.

图示 1-4 •

a42mx24 和 a42mx36 d-单元

Implementation

7 输入

Hard-线 to i/o

Feedback 至 排列

程序mable

反相器

图示 1-5 •

a42mx36 双-端口 sram 块

SRAM单元

32 x 8或者 64x4

(256 位)

读

端口

逻辑

写

端口

逻辑

RD[7:0]

routing 轨道

Latches

读

逻辑

[5:0]

rdad[5:0]

REN

RCLK

Latches

WD[7:0]

Latches

WRAD[5:0]

写

逻辑

MODE

BLKEN

WEN

WCLK

[5:0]

[7:0]