32-macrocell 最大值

®

EPLD

CY7C344B

使用 ultra37000

TM

为

所有 新 设计

Cypress 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文档 #: 38-03006 rev. *a 修订 april 19, 2004

特性

• 高-效能, 高-密度 替换 为 ttl,

74hc, 和 custom 逻辑

• 32 macrocells, 64 expander 产品 条款 在 一个 lab

• 8 专心致志的 输入, 16 i/o 管脚

• 0.8-micron 翻倍-metal cmos 非易失存储器 技术

• 28-管脚, 300-mil 插件, cerdip 或者 28-管脚 hlcc, plcc

包装

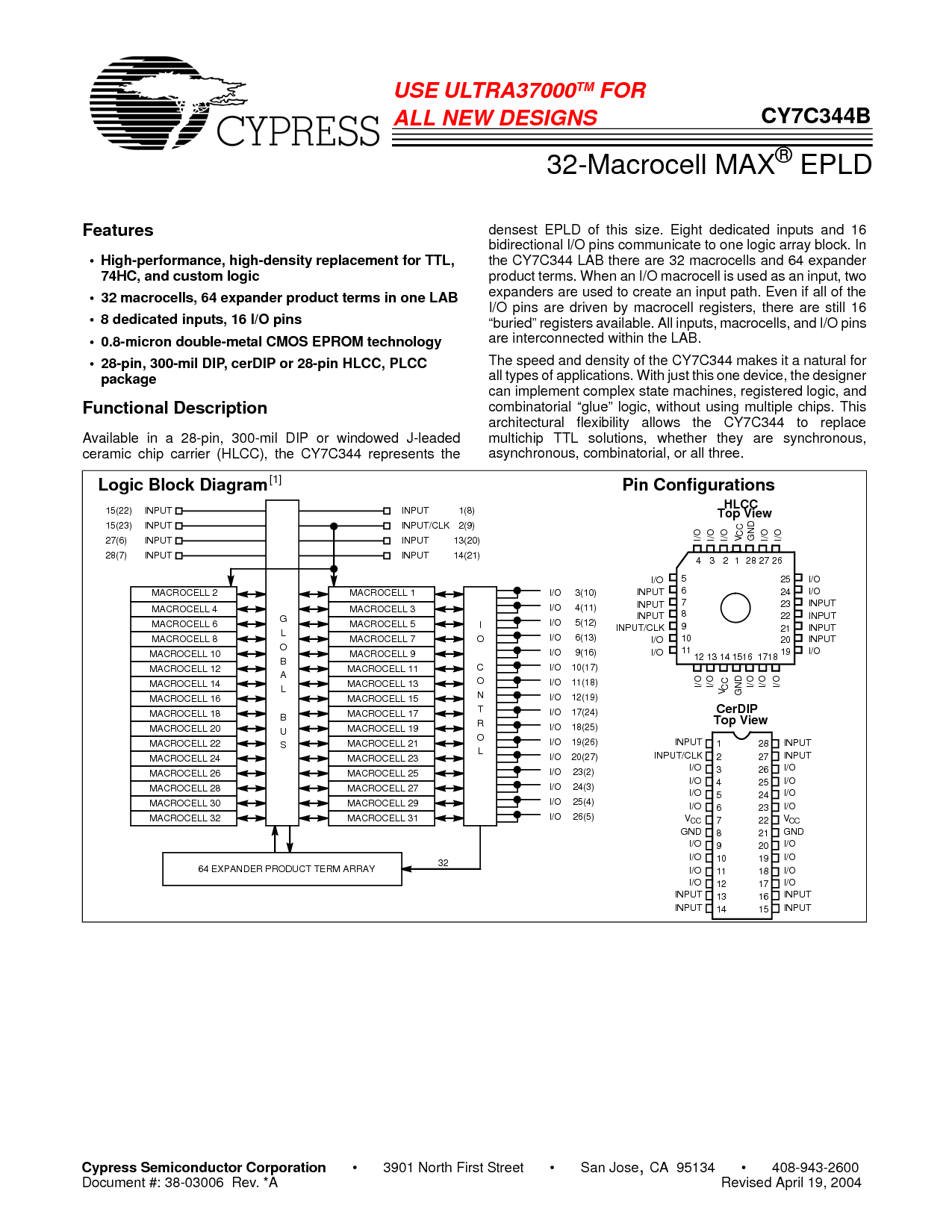

函数的 描述

有 在 一个 28-管脚, 300-mil 插件 或者 windowed j-含铅的

陶瓷的 碎片 运输车 (hlcc), 这 cy7c344 代表 这

densest epld 的 这个 大小. 第八 专心致志的 输入 和 16

双向的 i/o 管脚 communicate 至 一个 逻辑 排列 块. 在

这 cy7c344 lab 那里 是 32 macrocells 和 64 expander

产品 条款. 当 一个 i/o macrocell 是 使用 作 一个 输入, 二

expanders 是 使用 至 create 一个 输入 path. 甚至 如果 所有 的 这

i/o 管脚 是 驱动 用 macrocell 寄存器,那里 是 安静的 16

“buried” 寄存器 有. 所有 输入, macrocells, 和 i/o 管脚

是 interconnected 在里面 这 lab.

这 速 和 密度 的 这 cy7c344 制造 它 一个 自然的 为

所有 类型 的 产品. 和 just 这个 一个 设备, 这 设计者

能 执行 complex 状态 machines, 注册 逻辑, 和

combinatorial “glue” 逻辑, 没有 使用 多样的 碎片. 这个

architectural flexibility 准许 这 cy7c344 至 替代

multichip ttl 解决方案, whether 它们 是 同步的,

异步的, combinatorial, 或者 所有 三.

逻辑 块 图解

macrocell 2

macrocell 4

macrocell 6

macrocell 8

macrocell 10

macrocell 12

macrocell 14

macrocell 16

macrocell 18

macrocell 20

macrocell 22

macrocell 24

macrocell 26

macrocell 28

macrocell 30

macrocell 32

macrocell 1

macrocell 3

macrocell 5

macrocell 7

macrocell 9

macrocell 11

macrocell 13

macrocell 15

macrocell 17

macrocell 19

macrocell 21

macrocell 23

macrocell 25

macrocell 27

macrocell 29

macrocell 31

G

L

O

B

一个

L

B

U

S

I

O

C

O

N

T

R

O

L

输入

输入

输入

输入

15(22)

15(23)

27(6)

28(7)

输入 1(8)

输入/clk 2(9)

输入 13(20)

输入

14(21)

i/o 3(10)

i/o 4(11)

i/o 5(12)

i/o 6(13)

i/o 9(16)

i/o 10(17)

i/o 11(18)

i/o 12(19)

i/o 17(24)

i/o 18(25)

i/o 19(26)

i/o 20(27)

i/o 23(2)

i/o 24(3)

i/o 25(4)

i/o

26(5)

64 expander 产品 期 排列

32

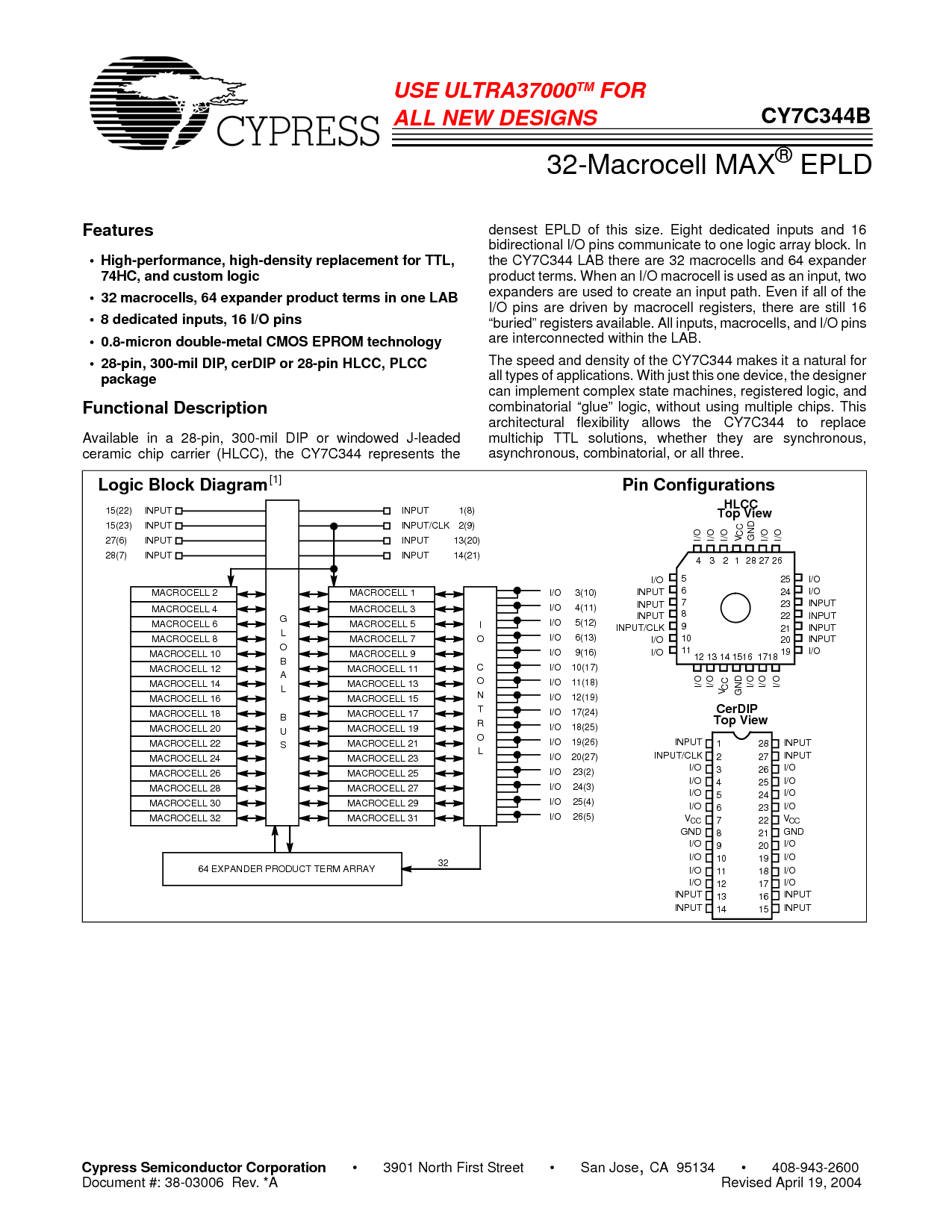

管脚 配置

顶 视图

HLCC

25

24

23

22

21

20

19

5

6

7

8

9

10

11

12 13 14 1516 1718

432 28 2726

i/o

i/o

输入

输入

输入

i/o

i/o

输入

输入

输入/clk

i/o

i/o

i/o

i/o

i/o

地

i/o

i/o

i/o

i/o

V

CC

1

V

CC

输入

i/o

地

i/o

i/o

输入

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

输入

输入

顶 视图

CerDIP

输入/clk

i/o

i/o

i/o

i/o

V

CC

地

i/o

i/o

i/o

i/o

输入

输入

输入

i/o

i/o

i/o

i/o

V

CC

地

i/o

i/o

i/o

i/o

输入

输入

[1]