scas685e −12月 2002 − 修订 十一月 2004

3

邮递 办公室 盒 655303

•

达拉斯市, 德州 75265

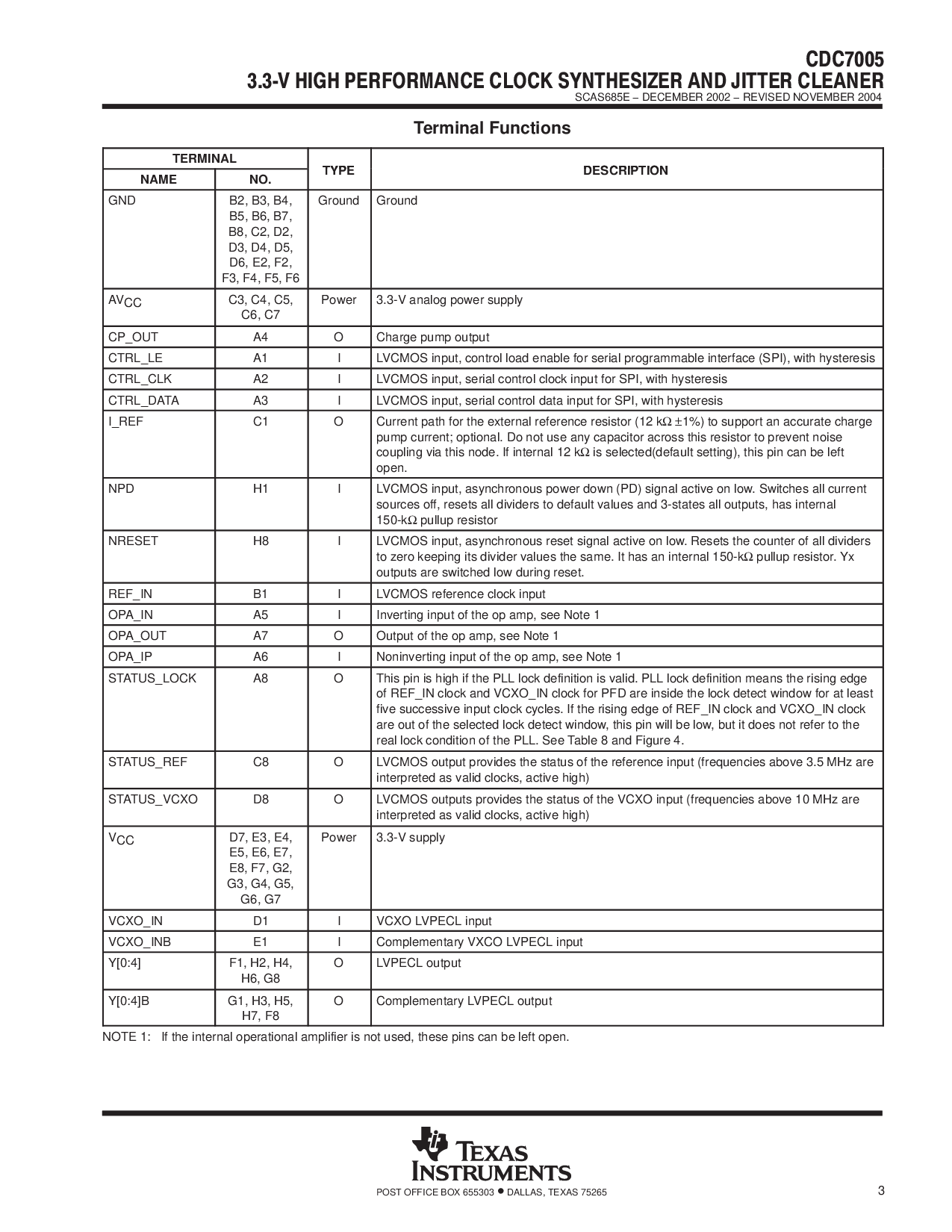

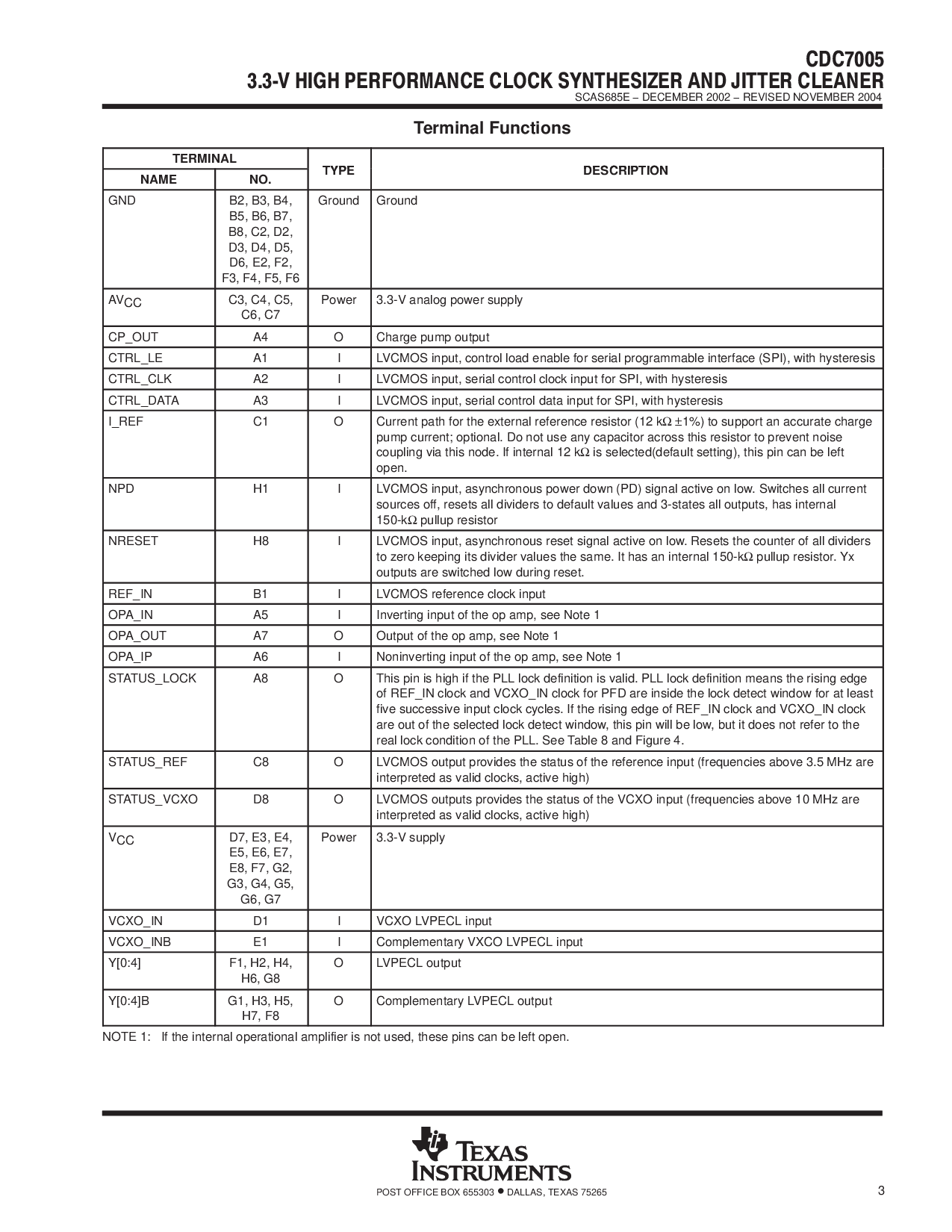

终端 功能

终端

类型 描述

名字 非.

类型 描述

地 b2, b3, b4,

b5, b6, b7,

b8, c2, d2,

d3, d4, d5,

d6, e2, f2,

f3, f4, f5, f6

地面 地面

AV

CC

c3, c4, c5,

c6, c7

电源 3.3-v 相似物 电源 供应

cp_输出 A4 O 承担 打气 输出

ctrl_le A1 I lvcmos 输入, 控制 加载 使能 为 串行 可编程序的 接口 (spi), 和 hysteresis

ctrl_clk A2 I lvcmos 输入, 串行 控制 时钟 输入 为 spi, 和 hysteresis

ctrl_数据 A3 I lvcmos 输入, 串行 控制 数据 输入 为 spi, 和 hysteresis

i_ref C1 O 电流 path 为 这 外部 涉及 电阻 (12 k

Ω

±

1%) 至 支持 一个 精确 承担

打气 电流; optional. 做 不 使用 任何 电容 横过 这个 电阻 至 阻止 噪音

连接 通过 这个 node. 如果 内部的 12 k

Ω

是 选择(default 设置), 这个 管脚 能 是 left

打开.

NPD H1 I lvcmos 输入, 异步的 电源 向下 (pd) 信号 起作用的 在 低. switches 所有 电流

来源 止, resets 所有 dividers 至 default 值 和 3-states 所有 输出, 有 内部的

150-k

Ω

pullup 电阻

NRESET H8 I lvcmos 输入, 异步的 重置 信号 起作用的 在 低. resets 这 计数器 的 所有 dividers

至 零 keeping 它的 分隔物 值 这 一样. 它 有 一个 内部的 150-k

Ω

pullup 电阻. yx

输出 是 切换 低 在 重置.

ref_在 B1 I lvcmos 涉及 时钟 输入

opa_在 A5 I 反相的 输入 的 这 运算 放大, 看 便条 1

opa_输出 A7 O 输出 的 这 运算 放大, 看 便条 1

opa_ip A6 I 同相 输入 的 这 运算 放大, 看 便条 1

状态_锁 A8 O 这个 管脚 是 高 如果 这 pll 锁 定义 是 有效的. pll 锁 定义 意思 这 rising 边缘

的 ref_在 时钟 和 vcxo_在 时钟 为 pfd 是 inside 这 锁 发现 window 为 在 least

five successive 输入 时钟 循环. 如果 这 rising 边缘 的 ref_在 时钟 和 vcxo_在 时钟

是 输出 的 这 选择 锁 发现 window, 这个 管脚 将 是 低, 但是 它 做 不 谈及 至 这

real 锁 情况 的 这 pll. 看 表格 8 和 图示 4.

状态_ref C8 O lvcmos 输出 提供 这 状态 的 这 涉及 输入 (发生率 在之上 3.5 mhz 是

interpreted 作 有效的 clocks, 起作用的 高)

状态_vcxo D8 O lvcmos 输出 提供 这 状态 的 这 vcxo 输入 (发生率 在之上 10 mhz 是

interpreted 作 有效的 clocks, 起作用的 高)

V

CC

d7, e3, e4,

e5, e6, e7,

e8, f7, g2,

g3, g4, g5,

g6, g7

电源 3.3-v 供应

vcxo_在 D1 I vcxo lvpecl 输入

vcxo_inb E1 I complementary vxco lvpecl 输入

y[0:4] f1, h2, h4,

h6, g8

O lvpecl 输出

y[0:4]b g1, h3, h5,

h7, f8

O complementary lvpecl 输出

便条 1: 如果 这 内部的 运算的 放大器 是 不 使用, 这些 管脚 能 是 left 打开.