201-0000-030 rev 2.0, 6/2/99 1

CH7202

CHRONTEL

mpeg 至 tv encoder 和 8-位 输入

特性

• Outputs ntsc, pal (b,d,g,h,i) 和pal-m (ntsc-

j orPAL-60一个vailable作运算tions)

• 8-b它 yCrCb(4:2:2) 在放format

• 主控 或者 从动装置 mode 运算限定

• Triple9-b它 d交流 for composite和s-video output

• 27 mhz d交流 运行frequency eliminates

这 需要 为 1/sinc(x)纠正 过滤

• 低-jitter阶段-锁 lo运算 电路系统 o每ates使用一个

低-cost 14.31818 mhzcrystal

• 40.5 或者 33.9 mhzvideodecoder clock output

• 16.934或者11.289 mhz 一个udio decoder clock output

• 13.5 mhz 一个nd 27 mhz video pixel clock outputs

• Internal 4.6 mhz (m ax) luminance 一个nd 1.3 mhz

ch只读存储器在一个ce 过滤

• sub-carriergenlocked至HSYNC*一个d vSYNC*

• 睡眠 模式

• CMOs technology 在44-管脚PLCC

• 5Vsingle-supply operation

Description

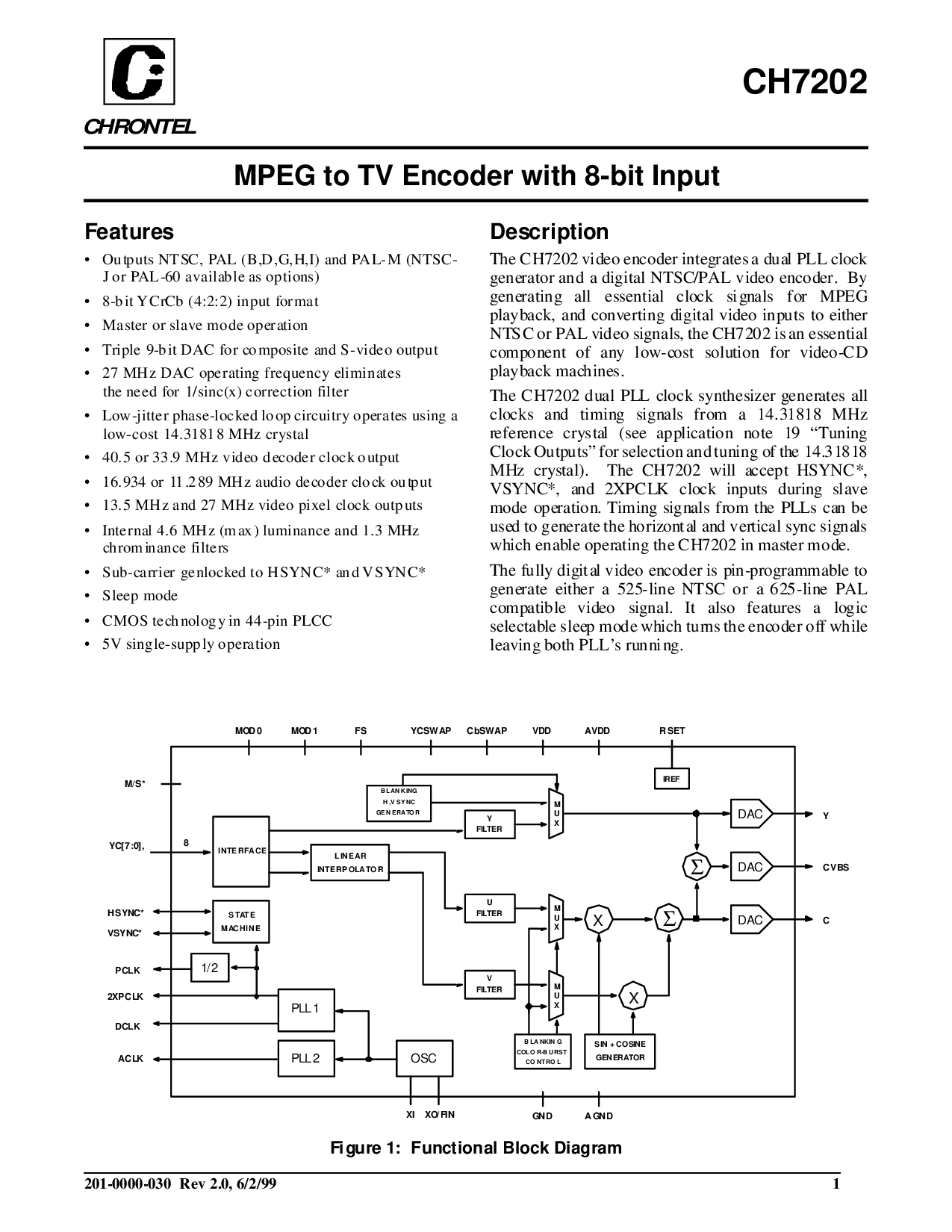

TheCH7202vi deoencoder在tegr一个tes 一个dual PLLclock

gener一个tor 一个nd一个digital nTsc/paLvideoencoder.用

generating 所有essential 时钟signals为 mpeg

播放后面的, 和converting digital video在puts 至 也

ntsc 或者PALvideo信号, 这 ch7202是 一个 essential

组件 的 任何 低-费用 解决方案 为 video-cd

playback machines.

TheCH7202dual pllclock synthesizer generates 一个ll

clocks 和 定时 信号 从 一个 14.31818 mhz

涉及 crystal(看 应用便条19“Tuning

Clock outputs”f或者selection 一个nd tuning的这14.31818

mhz 结晶). 这 ch7202 将 一个ccept hsync*,

VSYNc*,一个d 2xPCLKclockinputsduringsl ave

mode运算er一个tion.Timingsignalsfrom 这PLLs c一个be

美国edtogener一个tethehorizont al一个ndvertic一个lsyncsignals

这个en能 运算erating the cH7202 在master mode.

这 全部地 数字的 video encoder 是 管脚-可编程序的 至

generate 也 一个 525-line ntsc or 一个 625-线条 pal

兼容 video 信号. 它 也 特性 一个 逻辑

可选择的 sleepmode 这个turns the encoder off while

leaving both pll’srunning.

Figure 1: functional block 图解

U

过滤

V

过滤

DAC

DAC

DAC

Σ

Σ

X

M

U

X

M

U

X

M

U

X

Y

过滤

BLANKING

COLO r-b URST

CO NTRO L

BLAN KING

H ,v 同步

GEN ERATO R

X

sin + cosine

发生器

交流 LK

2XPCLK

Y

CVBS

C

YC[7:0],

IR EF

R设置AVDDVDD

AGNDGN D

XI xo/fin

MOD 0 MOD 1 FS

LINEAR

INTERPOLATO R

接口

PLL1

状态

机器

OSCPLL2

PCLK

DCLK

H SYNC*

VSYNC*

8

CbSWAPYCSWAP

m/s*

1/ 2