CS4351

6 DS566PP2

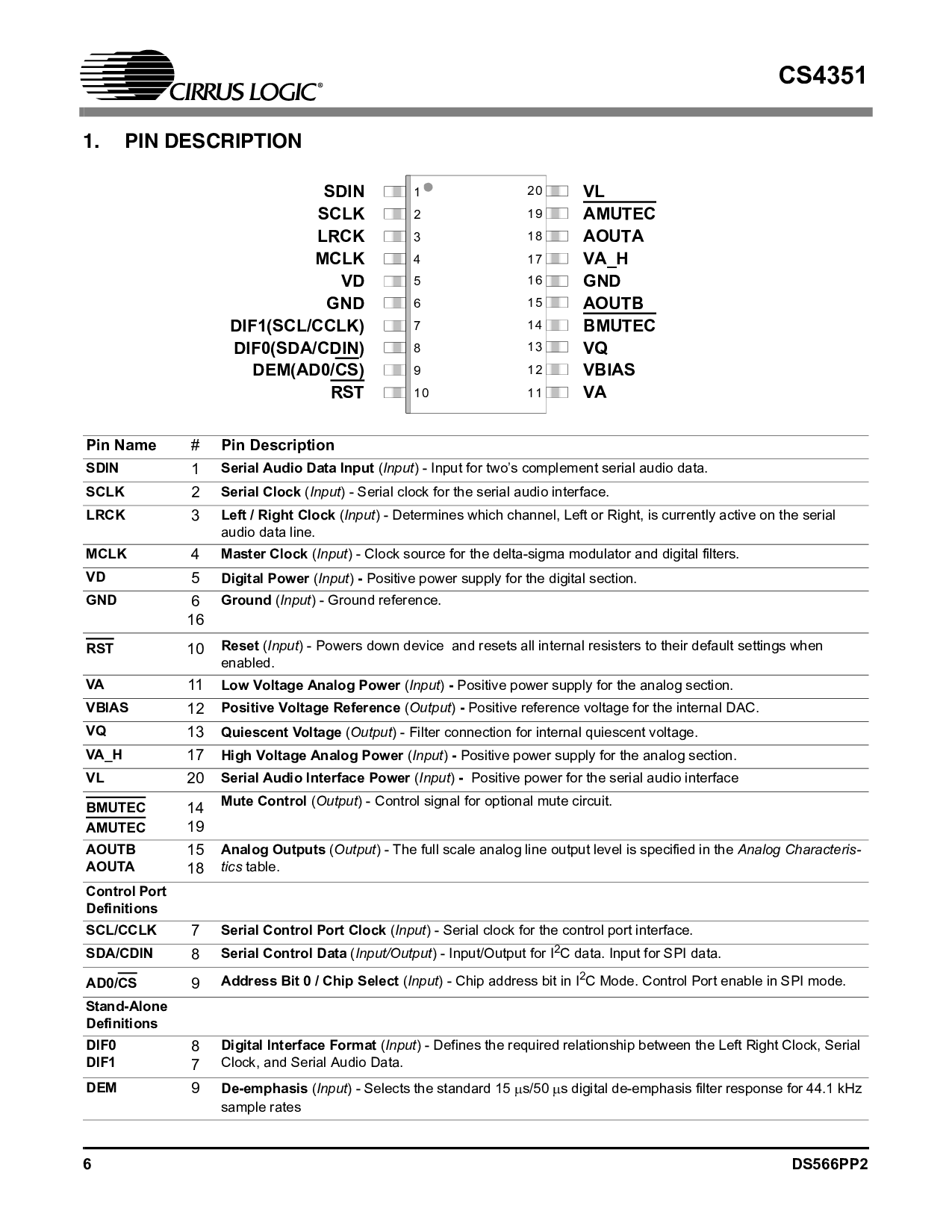

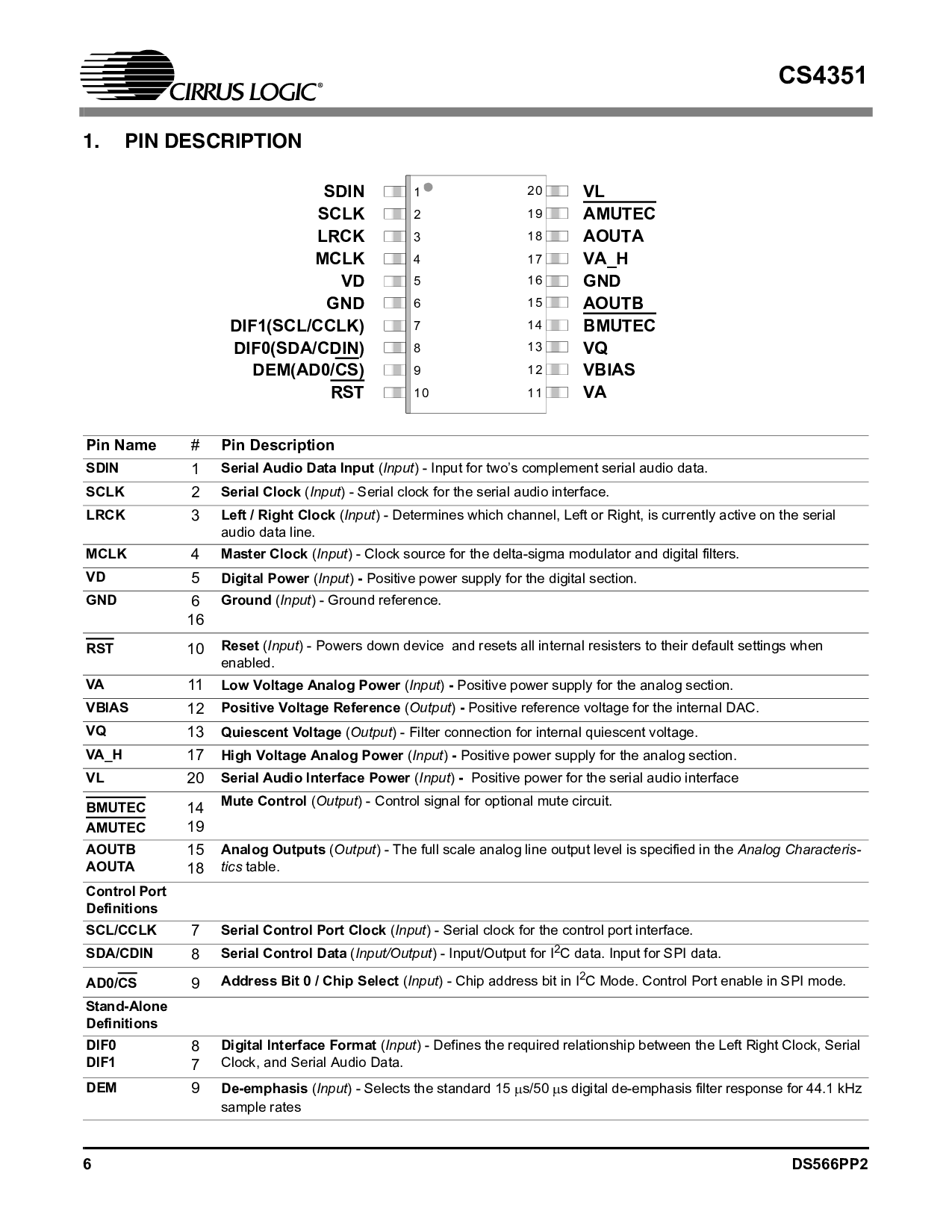

1. 管脚 描述

管脚 名字

#

管脚 描述

SDIN

1

串行 音频的 数据 输入

(

输入

) - 输入 为 二’s complement 串行 音频的 数据.

SCLK

2

串行

时钟

(

输入

) - 串行 时钟 为 这 串行 音频的 接口.

LRCK

3

left / 正确的 时钟

(

输入

) - 确定 这个 频道, left 或者 right, 是 目前 起作用的 在 这 串行

音频的 数据 线条.

MCLK

4

主控 时钟

(

输入

) - 时钟 源 为 这 delta-sigmamodulator 和 数字的 过滤.

VD

5

数字的 电源

(

输入

)

-

积极的 电源 供应 为 这 数字的 部分.

地

6

16

地面

(

输入

) - 地面 涉及.

RST

10

重置

(

输入

) - powers 向下 设备 和 resets 所有 internal resisters 至 它们的 default settings 当

使能.

VA

11

低 电压 相似物 电源

(

输入

)

-

积极的 电源 供应 为 这 相似物 部分.

VBIAS

12

积极的 电压 涉及

(

输出

)

-

积极的 涉及 电压 为 这 内部的 dac.

VQ

13

安静的 电压

(

输出

) - 过滤 连接 为 内部的 安静的 电压.

VA_H

17

高 电压 相似物 电源

(

输入

)

-

积极的 电源 供应 为 这 相似物 部分.

VL

20

串行 音频的 接口 电源

(

输入

)

-

积极的 电源 为 这 串行 音频的 接口

BMUTEC

AMUTEC

14

19

沉默的 控制

(

输出

) - 控制 信号 为optional 沉默的 电路.

AOUTB

AOUTA

15

18

相似物 输出

(

输出

) - 这 全部 规模 相似物 线条 输出 水平的 是 指定 在 这

相似物 characteris-

tics

表格.

控制 端口

定义

scl/cclk

7

串行 控制 端口 时钟

(

输入

) - 串行 时钟 为 这控制 端口 接口.

sda/cdin

8

串行 控制 数据

(

输入/输出

) - 输入/输出 为 i

2

c 数据. 输入 为 spi 数据.

ad0/cs

9

地址 位 0 / 碎片 选择

(

输入

) - 碎片 地址 位 在 i

2

c 模式. 控制 端口 使能 在 spi 模式.

保卫-alone

定义

DIF0

DIF1

8

7

数字的 接口 format

(

输入

) - 定义 这 必需的 relationship 在 这 left 正确的 时钟, 串行

时钟, 和 串行 音频的 数据.

DEM

9

de-emphasis

(

输入

) - 选择 这 标准 15

µ

s/50

µ

s 数字的 de-emphasis 过滤 回馈 为 44.1 khz

样本 比率

SDIN VL

SCLK AMUTEC

LRCK AOUTA

MCLK va_h

VD 地

地 AOUTB

dif1(scl/cclk) BMUTEC

dif0(sda/cdin) VQ

dem(ad0/cs

) VBIAS

RST

VA

1

2

3

4

5

6

7

8

9

10

11

12

17

18

19

20

13

14

15

16