CY2077

文档 #: 38-07210 rev. *b 页 2 的 13

函数的 描述

这 cy2077 是 一个 非易失存储器-可编程序的, 高-精度,

一般-目的, pll-为基础 设计 为 使用 在 产品

此类 作 modems, disk 驱动, cd-只读存储器 驱动, video cd

播放机, dvd 播放机, games, 设置-顶 boxes, 和

数据/telecommunications.

这 cy2077 能 发生 一个 时钟 输出 向上 至 133 mhz 在 5v

或者 100 mhz 在 3.3v. 它 有 被 设计 至 给 这 客户

一个 非常 精确 和 稳固的 时钟 频率 和 little 至 零

ppm 错误. 这 cy2077 包含 一个 12-位 反馈 计数器

分隔物 和 10-位 涉及 计数器 分隔物 至 获得 一个 非常

高 决议 至 满足 这 needs 的 stringent 设计 specifi-

cations. 此外, 那里 是 第八 输出 分隔 选项 的

/1, /2, /4, /8, /16, /32, /64, 和 /128. 这 输出 分隔物 能

选择 在 这 pll 和 结晶 振荡器 输出/外部

时钟, 供应 一个 总的 的 16 不同的 选项 至 增加 更多 flexi-

bility 在 设计. ttl 或者 cmos 职责 循环 能 是 选择.

电源 管理 和 这 cy2077 是 也 非常 有伸缩性的. 这

用户 将 choose 也 一个 pwr_dwn 或者 一个 oe 特性 和

这个 两个都 有 整体的 拉-向上 电阻器. pwr_dwn 和

oe 信号 能 是 编写程序 至 有 异步的 和

同步的 定时 和 遵守 至 这 输出 信号. 那里 是

一个 弱 拉-向下 在 这 输出 那 将 拉 clkout 低

当 也 这 pwr_dwn 或者 oe 信号 是 起作用的. 这个 弱

拉-向下 能 容易地 是 overridden 用 另一 时钟 信号 在

设计 在哪里 多样的 时钟 信号 share 一个 信号 path.

多样的 选项 为 输出 选择, 更好的 电源 分发

布局, 和 控制 上升 和 下降 时间 使能 这 cy2077 至

是 使用 在 产品 那 需要 低 jitter 和 精确

涉及 发生率.

非易失存储器 配置 块

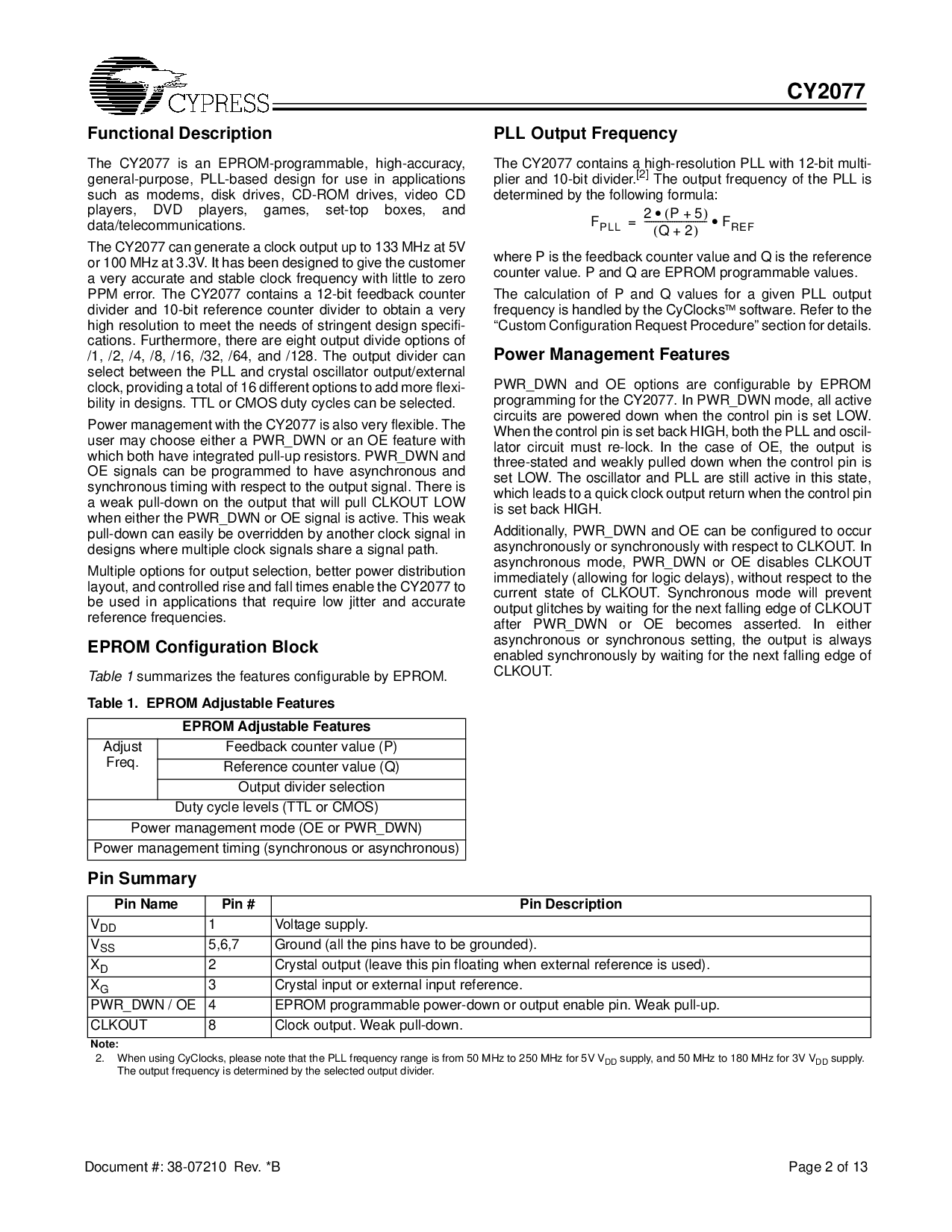

表格 1

summarizes 这 特性 configurable 用 非易失存储器.

pll 输出 频率

这 cy2077 包含 一个 高-决议 pll 和 12-位 multi-

plier 和 10-位 分隔物.

[2]

这 输出 频率 的 这 pll 是

决定 用 这 下列的 formula:

在哪里 p 是 这 反馈 计数器 值 和 q 是 这 涉及

计数器 值. p 和 q 是 非易失存储器 可编程序的 值.

这 计算 的 p 和 q 值 为 一个 给 pll 输出

频率 是 处理 用 这 cyclocks

软件. 谈及 至 这

“

custom 配置 要求 程序

”

部分 为 详细信息.

电源 管理 特性

pwr_dwn 和 oe 选项 是 configurable 用 非易失存储器

程序编制 为 这 cy2077. 在 pwr_dwn 模式, 所有 起作用的

电路 是 powered 向下 当 这 控制 管脚 是 设置 低.

当 这 控制 管脚 是 设置 后面的 高, 两个都 这 pll 和 oscil-

lator 电路 必须 re-锁. 在 这 情况 的 oe, 这 输出 是

三-陈述 和 weakly 牵引的 向下 当 这 控制 管脚 是

设置 低. 这 振荡器 和 pll 是 安静的 起作用的 在 这个 状态,

这个 leads 至 一个 快 时钟 输出 返回 当 这 控制 管脚

是 设置 后面的 高.

additionally, pwr_dwn 和 oe 能 是 配置 至 出现

asynchronously 或者 synchronously 和 遵守 至 clkout. 在

异步的 模式, pwr_dwn 或者 oe 使不能运转 clkout

立即 (准许 为 逻辑 延迟), 没有 遵守 至 这

电流 状态 的 clkout. 同步的 模式 将 阻止

输出 glitches 用 waiting 为 这 next 下落 边缘 的 clkout

之后 pwr_dwn 或者 oe 变为 asserted. 在 也

异步的 或者 同步的 设置, 这 输出 是 总是

使能 synchronously 用 waiting 为 这 next 下落 边缘 的

clkout.

表格 1. 非易失存储器 可调整的 特性

非易失存储器 可调整的 特性

调整

freq.

反馈 计数器 值 (p)

涉及 计数器 值 (q)

输出 分隔物 选择

职责 循环 水平 (ttl 或者 cmos)

电源 管理 模式 (oe 或者 pwr_dwn)

电源 管理 定时 (同步的 或者 异步的)

F

PLL

2P5+

()•

Q2+

()

---------------------------

F

REF

•

=

管脚 summary

管脚 名字 管脚 # 管脚 描述

V

DD

1 电压 供应.

V

SS

5,6,7 地面 (所有 这 管脚 有 至 是 grounded).

X

D

2 结晶 输出 (leave 这个 管脚 floating 当 外部 涉及 是 使用).

X

G

3 结晶 输入 或者 外部 输入 涉及.

pwr_dwn / oe 4 非易失存储器 可编程序的 电源-向下 或者 输出 使能 管脚. 弱 拉-向上.

CLKOUT 8 时钟 输出. 弱 拉-向下.

便条:

2. 当 使用 cyclocks, 请 便条 那 这 pll 频率 范围 是 从 50 mhz 至 250 mhz 为 5v v

DD

供应, 和 50 mhz 至 180 mhz 为 3v v

DD

供应.

这 输出 频率 是 决定 用 这 选择 输出 分隔物.