rev. f–4–

ad5305/ad5315/ad5325

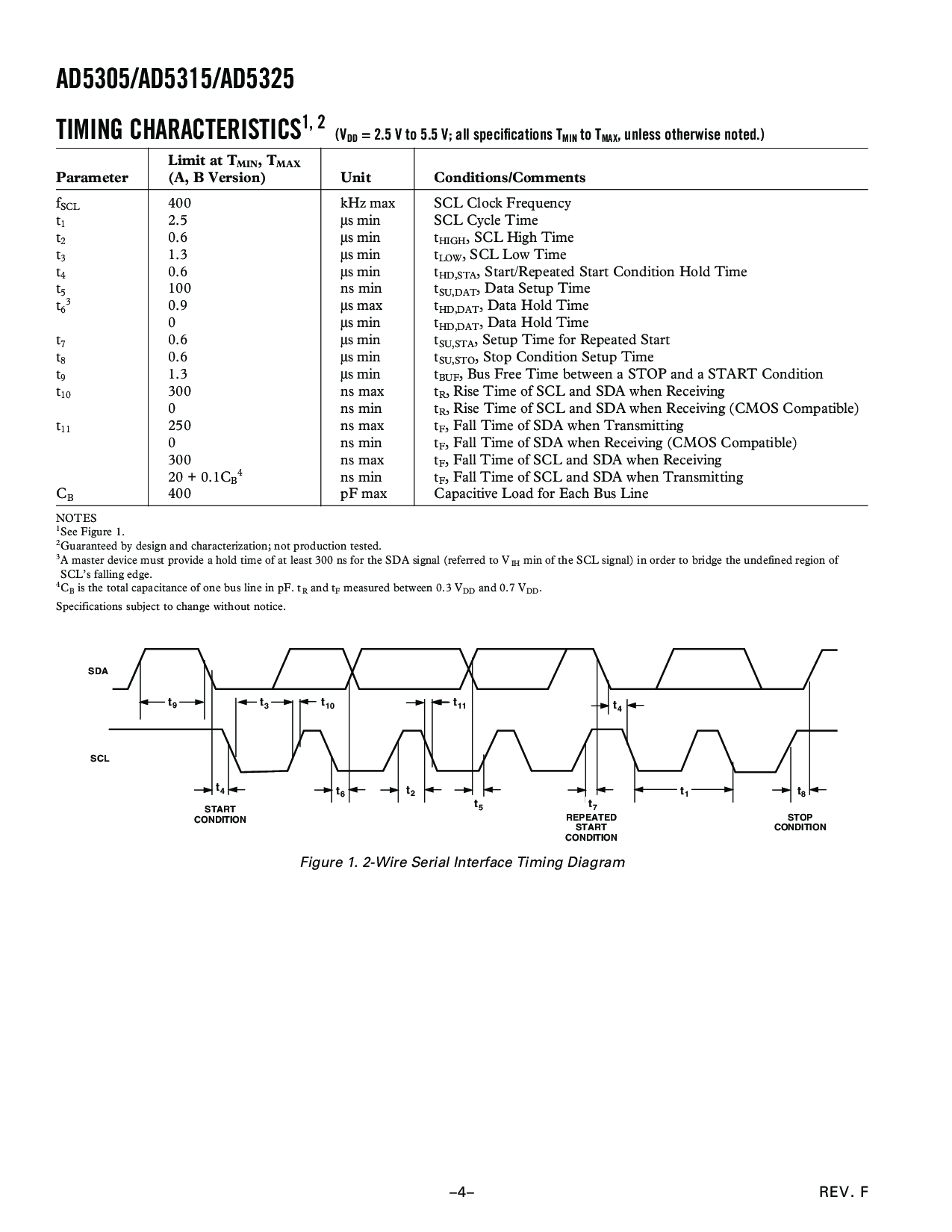

定时 特性

1, 2

(v

DD

= 2.5 v 至 5.5 v; 所有 specifications t

最小值

至 t

最大值

, 除非 否则 指出.)

限制 在 t

最小值

, t

最大值

参数 (一个, b 版本) 单位 情况/comments

f

SCL

400 khz 最大值 scl 时钟 频率

t

1

2.5

µ

s 最小值 scl 循环 时间

t

2

0.6

µ

s 最小值 t

高

, scl 高 时间

t

3

1.3

µ

s 最小值 t

低

, scl 低 时间

t

4

0.6

µ

s 最小值 t

hd,sta

, 开始/重复的 开始 情况 支撑 时间

t

5

100 ns 最小值 t

su,dat

, 数据 建制 时间

t

6

3

0.9

µ

s 最大值 t

hd,dat

, 数据 支撑 时间

0

µ

s 最小值 t

hd,dat

, 数据 支撑 时间

t

7

0.6

µ

s 最小值 t

su,sta

, 建制 时间 为 重复的 开始

t

8

0.6

µ

s 最小值 t

su,sto

, 停止 情况 建制 时间

t

9

1.3

µ

s 最小值 t

BUF

, 总线 自由 时间 在 一个 停止 和 一个 开始 情况

t

10

300 ns 最大值 t

R

, 上升 时间 的 scl 和 sda 当 接到

0 ns 最小值 t

R

, 上升 时间 的 scl 和 sda 当 接到 (cmos 兼容)

t

11

250 ns 最大值 t

F

, 下降 时间 的 sda 当 transmitting

0 ns 最小值 t

F

, 下降 时间 的 sda 当 接到 (cmos 兼容)

300 ns 最大值 t

F

, 下降 时间 的 scl 和 sda 当 接到

20 + 0.1c

B

4

ns 最小值 t

F

, 下降 时间 的 scl 和 sda 当 transmitting

C

B

400 pf 最大值 电容的 加载 为 各自 总线 线条

注释

1

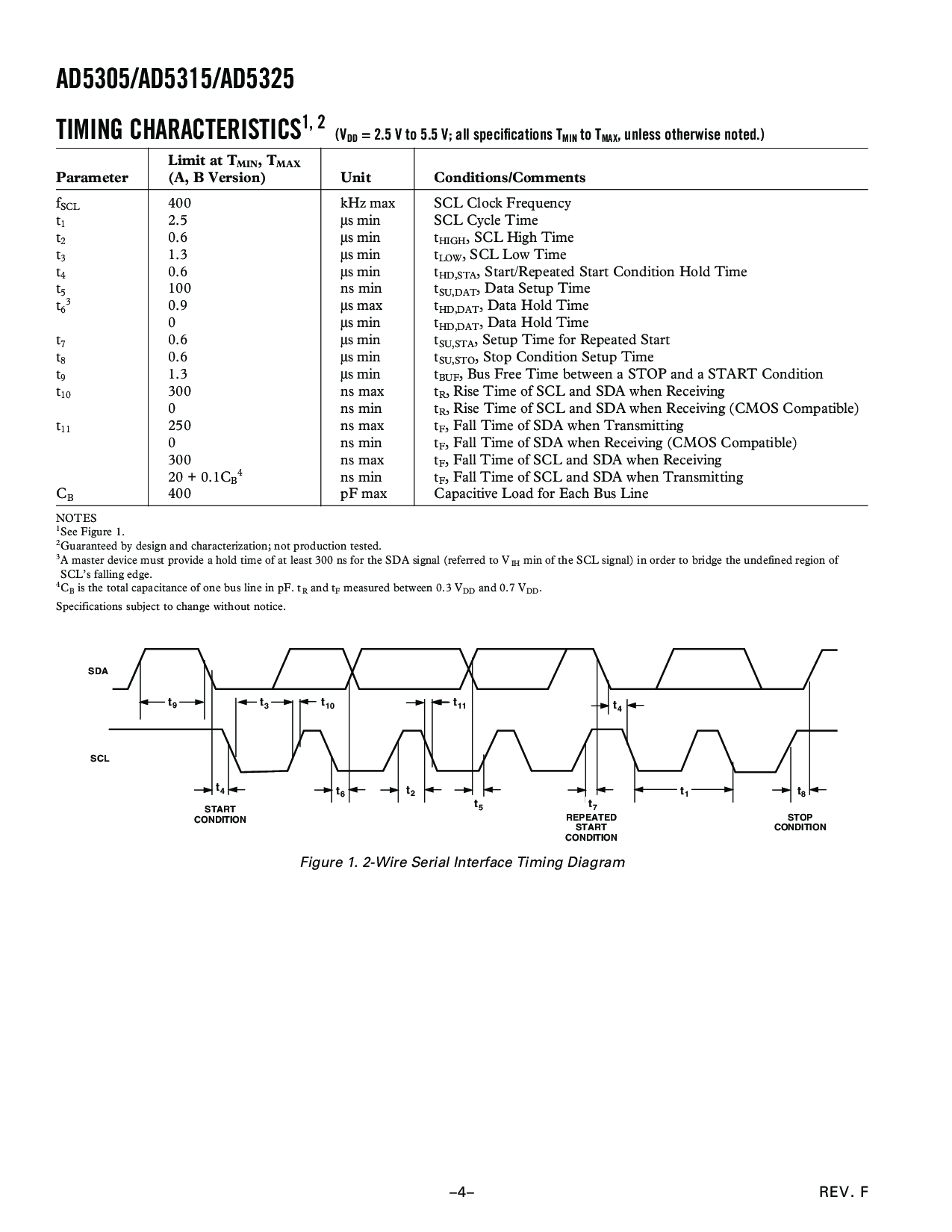

看 图示 1.

2

有保证的 用 设计 和 描绘; 不 生产 测试.

3

一个 主控 设备 必须 提供 一个 支撑 时间 的 在 least 300 ns 为 这 sda 信号 (涉及 至 v

IH

最小值 的 这 scl 信号) 在 顺序 至 桥 这 未阐明的 区域 的

scl’s 下落 边缘.

4

C

B

是 这 总的 电容 的 一个 总线 线条 在 pf. t

R

和 t

F

量过的 在 0.3 v

DD

和 0.7 v

DD

.

规格 主题 至 改变 没有 注意.

SCL

SDA

开始

情况

t

9

t

3

t

4

t

6

t

2

t

5

t

7

t

8

t

1

t

4

t

11

t

10

重复的

开始

情况

停止

情况

图示 1. 2-线 串行 接口 定时 图解