AD7575

–5–

rev. b

定时 和 控制 的 这 ad7575

这 二 逻辑 输入 在 这 ad7575,

CS

和

RD

, 控制 两个都

这 开始 的 转换 和 这 读 的 数据 从 这 部分.

一个 转换 是 initiated 用 bringing 两个都 的 这些 控制 输入

低. 二 接口 选项 然后 exist 为 读 这 输出

数据 从 这 ad7575. 这些 是 这 慢 记忆 接口

和 只读存储器 接口, 它们的 运作 是 概述 在下. 它 应当

是 指出 那 这 tp 管脚 的 这 ad7575 必须 是 hard-连线的

高 至 确保 准确无误的 运作 的 这 部分. 这个 管脚 是 使用

在 测试 这 设备 和 应当 不 是 使用 作 一个 feedthrough 管脚

在 翻倍-sided 打印 电路 boards.

慢 记忆 接口

这 第一 接口 选项 是 将 为 使用 和 microproces-

sors 那 能 是 强迫 在 一个 wait 状态 为 在 least 5

µ

s.

这 微处理器 (此类 作 这 8085a) 开始 一个 转换 和

是 halted 直到 这 结果 的 这 转换 是 读 从 这 con-

verter. 转换 是 initiated 用 executing 一个 记忆 读 至

这 ad7575 地址, bringing

CS

和

RD

低.

BUSY

subse-

quently 变得 低 (forcing 这 微处理器 准备好 输入

低), 放置 这 处理器 在 一个 wait 状态. 这 输入

信号, 这个 had 被 tracked 用 这 相似物 输入, 是 使保持 在

这 第三 下落 时钟 边缘 的 这 输入 时钟 之后

CS

和

RD

有 gone 低 (看 图示 12). 这 ad7575 然后 执行 一个

转换 在 这个 acquired 输入 信号 值. 当 这 con-

版本 是 完全 (

BUSY

变得 高), 这 处理器 com-

pletes 这 记忆 读 和 acquires 这 newly 转变

数据. 这 定时 图解 为 这个 接口 是 显示 在 图示 3.

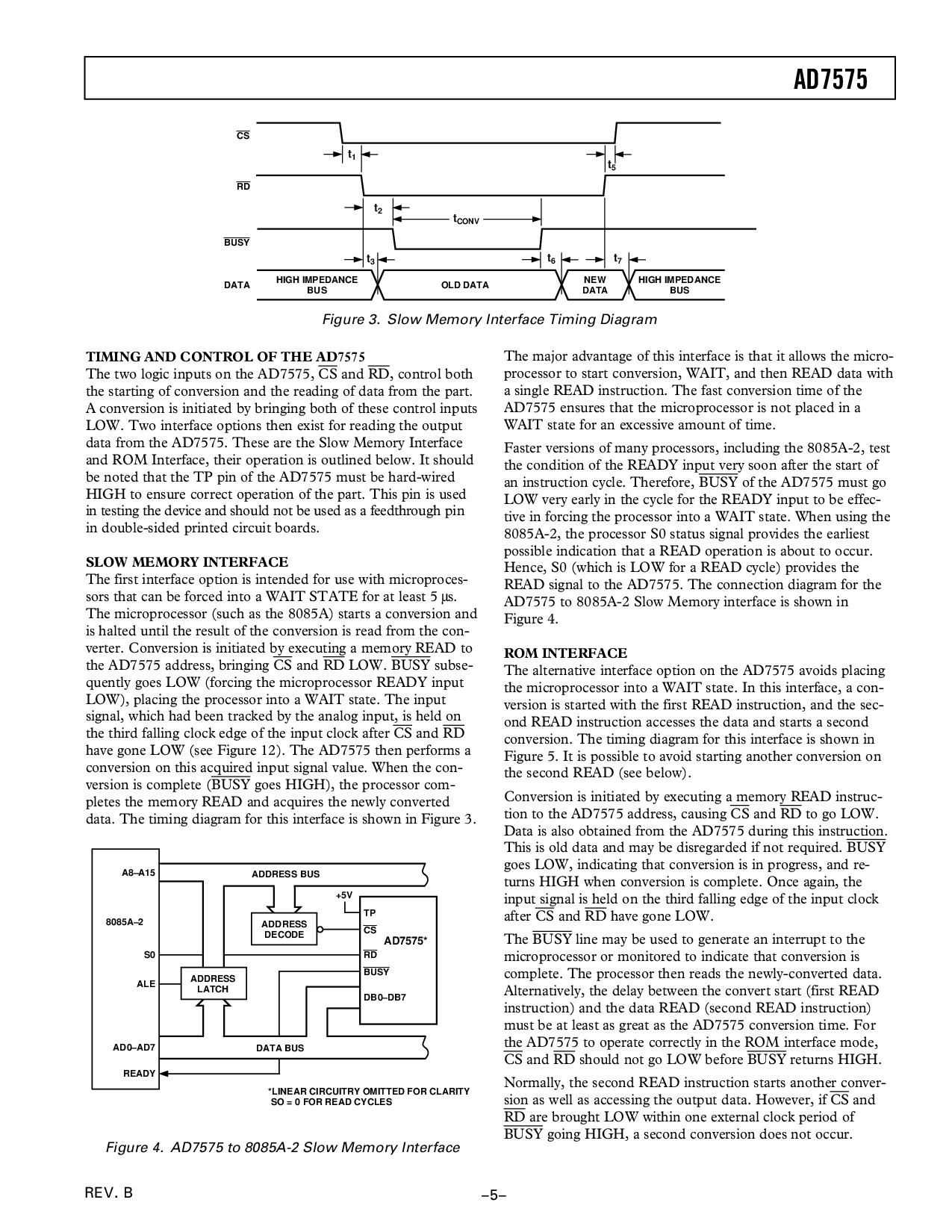

地址

DECODE

地址

获得

AD7575*

TP

CS

RD

BUSY

DB0–DB7

地址 总线

数据 总线

+5V

A8–A15

S0

ALE

AD0–AD7

准备好

8085A–2

*linear 电路系统 omitted 为 clarity

所以 = 0 为 读 循环

图示 4. ad7575 至 8085a-2 慢 记忆 接口

这 主要的 有利因素 的 这个 接口 是 那 它 准许 这 微观的-

处理器 至 开始 转换, wait, 和 然后 读 数据 和

一个 单独的 读 操作指南. 这 快 转换 时间 的 这

ad7575 确保 那 这 微处理器 是 不 放置 在 一个

wait 状态 为 一个 过度的 数量 的 时间.

faster 版本 的 许多 processors, 包含 这 8085a-2, 测试

这 情况 的 这 准备好 输入 非常 soon 之后 这 开始 的

一个 操作指南 循环. 因此,

BUSY

的 这 ad7575 必须 go

低 非常 early 在 这 循环 为 这 准备好 输入 至 是 effec-

tive 在 forcing 这 处理器 在 一个 wait 状态. 当 使用 这

8085a-2, 这 处理器 s0 状态 信号 提供 这 earliest

可能 indication 那 一个 读 运作 是 关于 至 出现.

hence, s0 (这个 是 低 为 一个 读 循环) 提供 这

读 信号 至 这 ad7575. 这 连接 图解 为 这

ad7575 至 8085a-2 慢 记忆 接口 是 显示 在

图示 4.

只读存储器 接口

这 alternative 接口 选项 在 这 ad7575 避免 放置

这 微处理器 在 一个 wait 状态. 在 这个 接口, 一个 con-

版本 是 started 和 这 第一 读 操作指南, 和 这 秒-

ond 读 操作指南 accesses 这 数据 和 开始 一个 第二

转换. 这 定时 图解 为 这个 接口 是 显示 在

图示 5. 它 是 可能 至 避免 开始 另一 转换 在

这 第二 读 (看 在下).

转换 是 initiated 用 executing 一个 记忆 读 instruc-

tion 至 这 ad7575 地址, 造成

CS

和

RD

至 go 低.

数据 是 也 得到 从 这 ad7575 在 这个 操作指南.

这个 是 old 数据 和 将 是 disregarded 如果 不 必需的.

BUSY

变得 低, 表明 那 转换 是 在 progress, 和 re-

转变 高 当 转换 是 完全. once 又一次, 这

输入 信号 是 使保持 在 这 第三 下落 边缘 的 这 输入 时钟

之后

CS

和

RD

有 gone 低.

这

BUSY

线条 将 是 使用 至 发生 一个 中断 至 这

微处理器 或者 监控 至 表明 那 转换 是

完全. 这 处理器 然后 读 这 newly-转变 数据.

alternatively, 这 延迟 在 这 转变 开始 (第一 读

操作指南) 和 这 数据 读 (第二 读 操作指南)

必须 是 在 least 作 好 作 这 ad7575 转换 时间. 为

这 ad7575 至 运作 correctly 在 这 只读存储器 接口 模式,

CS

和

RD

应当 不 go 低 在之前

BUSY

returns 高.

正常情况下, 这 第二 读 操作指南 开始 另一 变换器-

sion 作 好 作 accessing 这 输出 数据. 不管怎样, 如果

CS

和

RD

是 brought 低 在里面 一个 外部 时钟 时期 的

BUSY

going 高, 一个 第二 转换 做 不 出现.

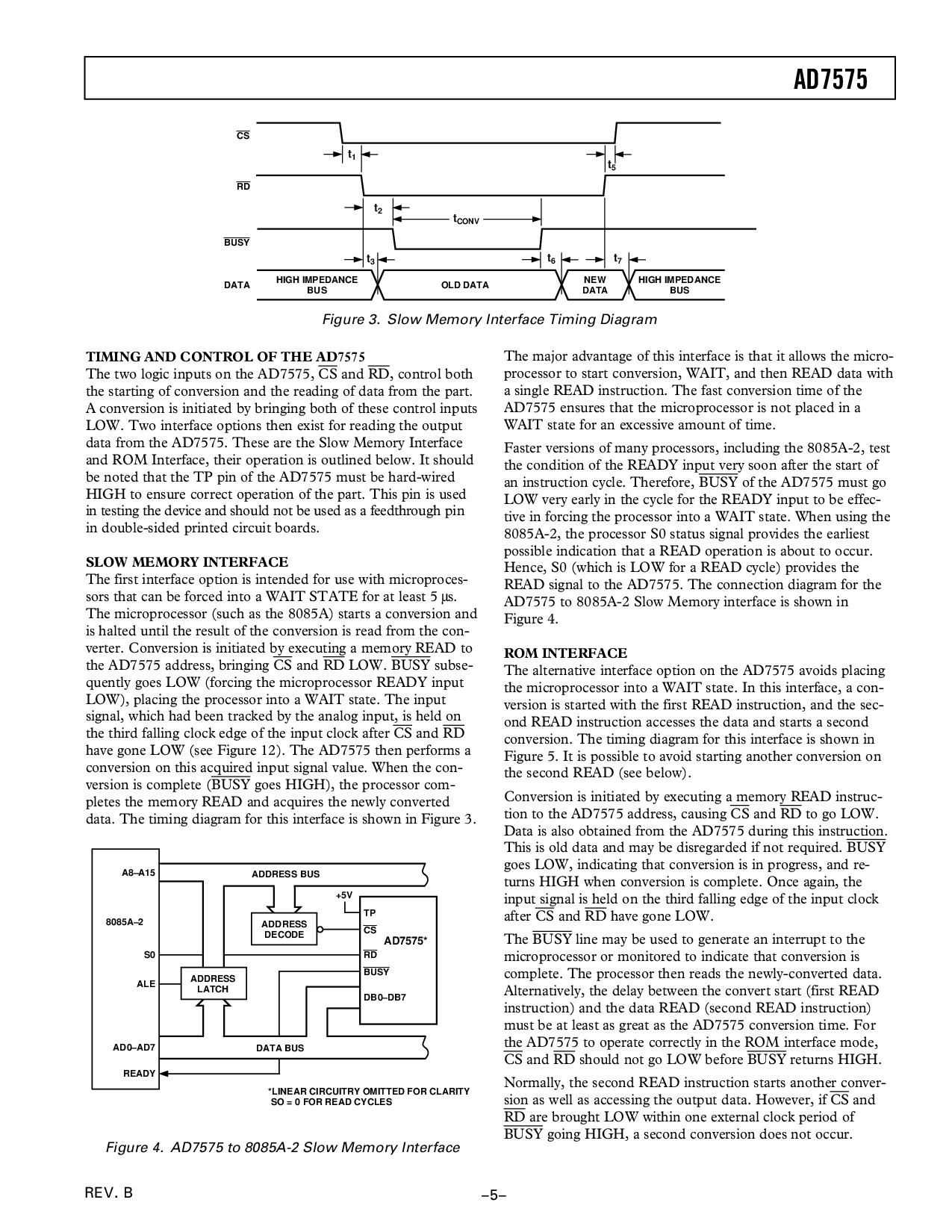

t

5

t

1

t

2

t

6

t

7

t

CONV

高 阻抗

总线

新

数据

old 数据

高 阻抗

总线

CS

RD

BUSY

数据

t

3

图示 3. 慢 记忆 接口 定时 图解