2

AD7711A

–7–rev. c

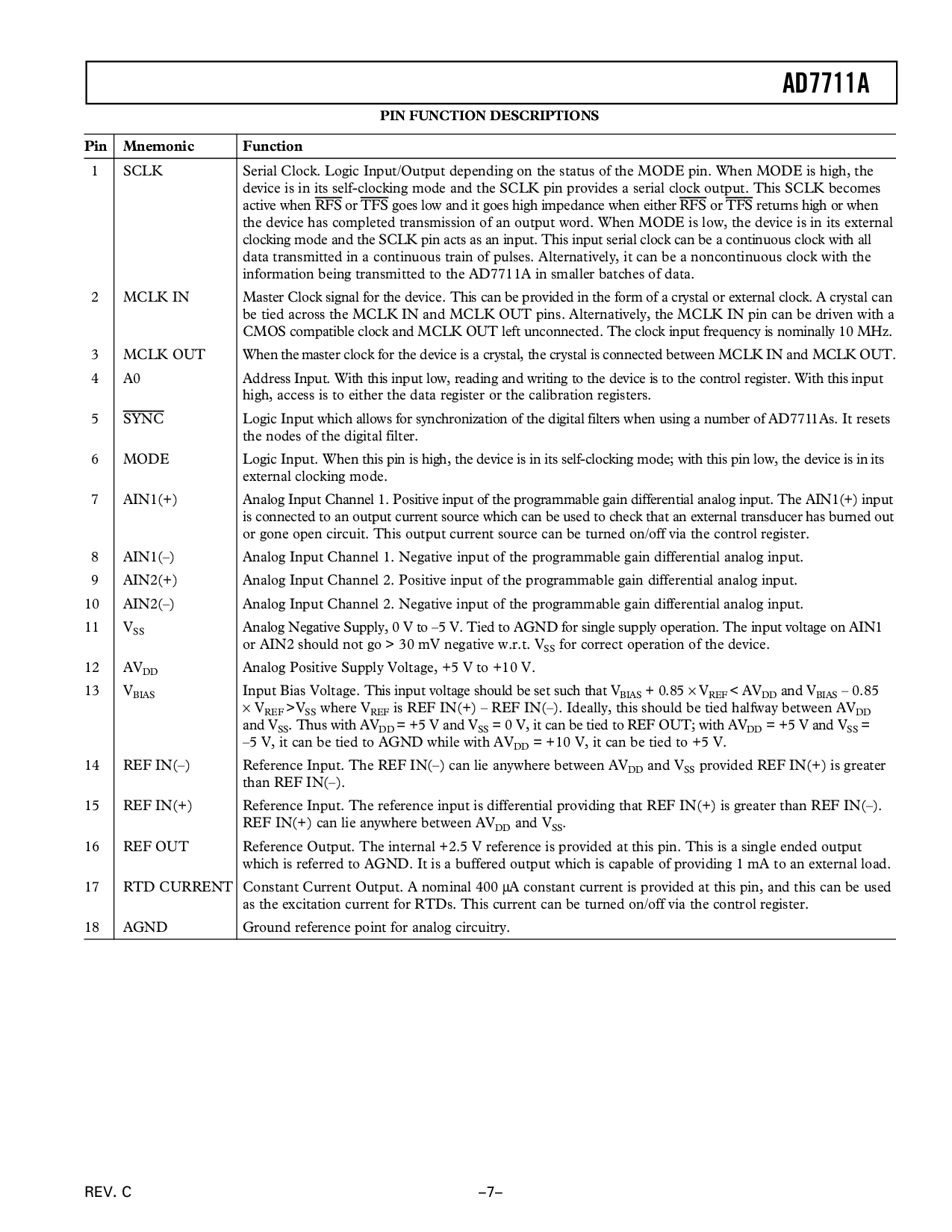

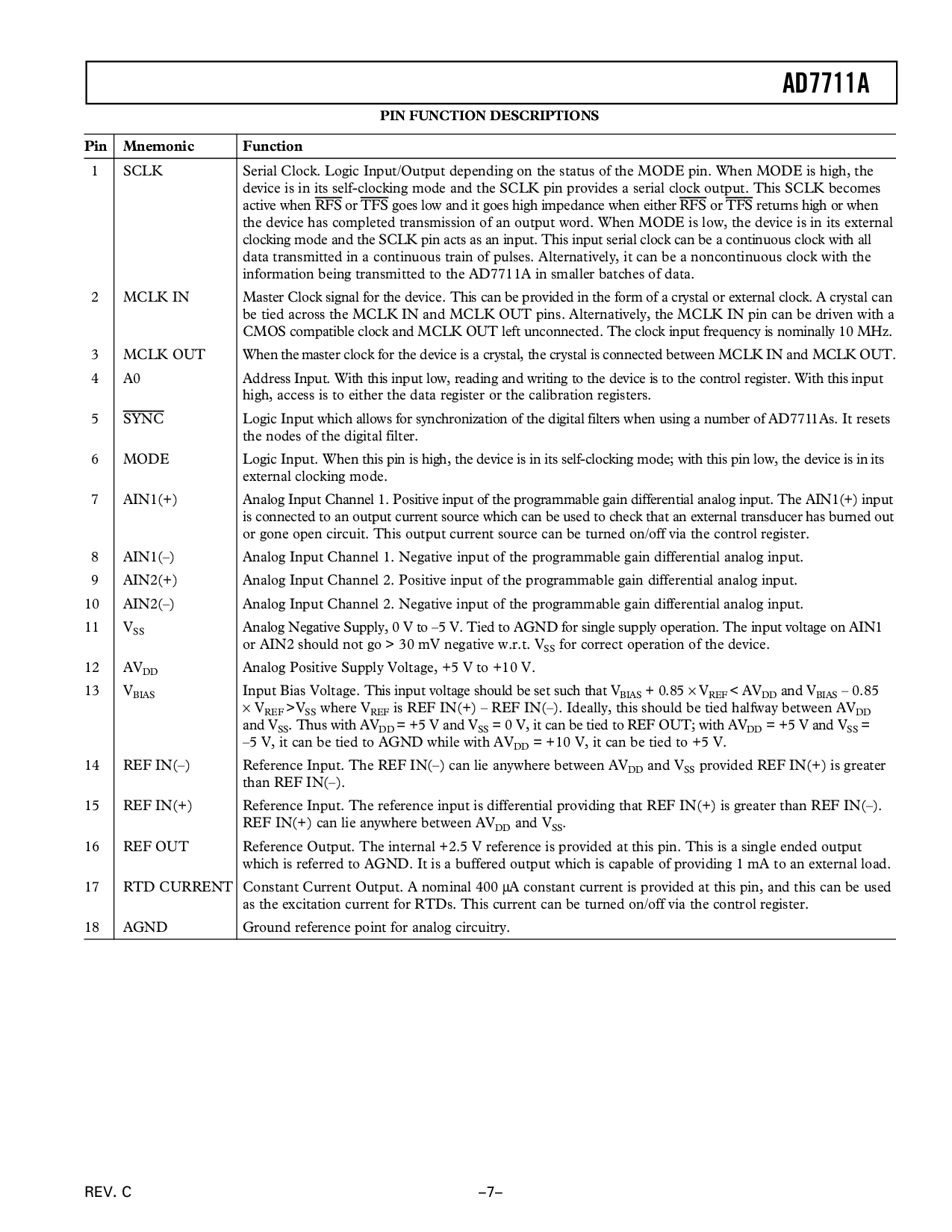

管脚 函数 描述

管脚 Mnemonic 函数

1 SCLK 串行 时钟. 逻辑 输入/输出 取决于 在 这 状态 的 这 模式 管脚. 当 模式 是 高, 这

设备 是 在 它的 自-clocking 模式 和 这 sclk 管脚 提供 一个 串行 时钟 输出. 这个 sclk 变为

起作用的 当

RFS

或者

TFS

变得 低 和 它 变得 高 阻抗 当 也

RFS

或者

TFS

returns 高 或者 当

这 设备 有 完成 传递 的 一个 输出 文字. 当 模式 是 低, 这 设备 是 在 它的 外部

clocking 模式 和 这 sclk 管脚 acts 作 一个 输入. 这个 输入 串行 时钟 能 是 一个 持续的 时钟 和 所有

数据 transmitted 在 一个 持续的 train 的 脉冲. alternatively, 它 能 是 一个 noncontinuous 时钟 和 这

信息 正在 transmitted 至 这 ad7711a 在 小 batches 的 数据.

2 mclk 在 主控 时钟 信号 为 这 de恶行. this 能 是 提供 在 这 表格 的 一个 结晶 或者 外部 时钟. 一个 crystal 能

是 系 横过 这 mclk 在 和 mclk 输出 管脚. alternatively, 这 mclk 在 管脚 能 是 驱动 和 一个

cmos 兼容 时钟 和 mclk 输出 left unconnected. 这 时钟 输入 频率 是 nominally 10 mhz.

3 mclk 输出 当这 master 时钟 为 这 设备 是 一个 结晶, 这 结晶 是 连接 在 mclk 在 和 mclk 输出.

4 A0 地址 输入. 和 这个 输入 低, 读 和 writing 至 这 设备 是 至 这 控制 寄存器. 和 这个输入

高, 进入 是 至 也 这 数据 寄存器 或者 这 校准 寄存器.

5

同步

逻辑 在放 这个 准许 为 同步 的 这 数字的 过滤 当 使用 一个 号码 的 ad7711as. 它resets

这 nodes 的 这 数字的 过滤.

6 模式 逻辑 输入. when 这个 管脚 是 高, 这 设备 是 在 它的 自-clocking 模式; 和 这个 管脚 低, 这 设备 是 在 它的

外部 clocking 模式.

7 ain1(+) 相似物输入 频道 1. 积极的 输入 的 这 可编程序的 增益 差别的 相似物 输入. 这 ain1(+) 输入

是 连接 至 一个 输出 电流 源 这个 能 是 使用 至 审查 那 一个 外部 transducer 有 burned 输出

或者 gone 打开 电路. 这个 输出 电流 源 能 是 转变 开关 通过 这 控制 寄存器.

8 ain1(–) 相似物 输入 频道 1. 负的 输入 的 这 可编程序的 增益 差别的 相似物 输入.

9 ain2(+) 相似物 输入 频道 2. 积极的 输入 的 这 可编程序的 增益 差别的 相似物 输入.

10 ain2(–) 相似物 输入 频道 2. 负的 输入 的 这 可编程序的 增益 差别的 相似物 输入.

11 V

SS

相似物 负的 供应, 0 v 至 –5 v. 系 至 agnd 为 单独的 供应 运作. 这 输入 电压 在 ain1

或者 ain2 应当 不 go > 30 mv 负的 w.r.t. v

SS

为 准确无误的 运作 的 这 设备.

12 AV

DD

相似物 积极的 供应 电压, +5 v 至 +10 v.

13 V

偏差

输入 偏差 电压. 这个输入 电压 应当 是 设置 此类 那 v

偏差

+ 0.85

×

V

REF

< av

DD

和 v

偏差

– 0.85

×

V

REF

>v

SS

在哪里 v

REF

是 ref 在(+) – ref 在(–). ideally, 这个 应当 是 系 halfway 在 av

DD

和 v

SS

. 因此 和 av

DD

= +5 v 和 v

SS

= 0 v, 它 能 是 系 至 ref 输出; 和 av

DD

= +5 v 和 v

SS

=

–5 v, 它 能 是 系 至 agnd 当 和 av

DD

= +10 v, 它 能 是 系 至 +5 v.

14 ref 在(–) 涉及 输入. 这 ref 在(–) 能 lie anywhere 在 av

DD

和 v

SS

提供 ref 在(+) 是 更好

比 ref 在(–).

15 ref 在(+) 涉及 输入. 这 涉及 输入 是 差别的 供应 那 ref 在(+) 是 更好 比 ref 在(–).

ref 在(+) 能 lie anywhere 在 av

DD

和 v

SS

.

16 ref 输出 涉及 输出. 这 内部的 +2.5 v 涉及 是 提供 在 这个 管脚. 这个 是 一个 单独的 结束 输出

这个 是 涉及 至 agnd. 它 是 一个 缓冲 输出 这个 是 有能力 的 供应 1 毫安 至 一个 外部 加载.

17 rtd 电流 常量 电流 输出. 一个 名义上的 400

µ

一个 常量 电流 是 提供 在 这个 管脚, 和 这个 能 是 使用

作 这 excitation 电流 为 rtds. 这个 电流 能 是 转变 开关 通过 这 控制 寄存器.

18 AGND 地面 涉及 要点 为 相似物 电路系统.