rev. 一个

AD974

–7–

转换 控制

这 ad974 是 控制 用 二 信号: r/

C

和

CS

. 当

r/

C

是 brought低, 和

CS

低, 为 一个 最小 的 50ns, 这

输入 信号 将 是 使保持 在 这 内部的 电容 排列 和 一个

转换 “n” 将 begin. once 这 转换 处理 做

begin, 这

BUSY

信号 将 go 低 直到 这 转换 是 com-

plete. 内部, 这 信号 r/

C

和

CS

是 ored 一起 和

那里 是 非 必要条件 在 这个 信号 是 带去 低 第一 当

初始的 一个 转换. 这 仅有的 必要条件 是 那 那里 是 在

least 10 ns 的 延迟 在 这 二 信号 正在 带去 低.

之后 这 转换 是 完全, 这

BUSY

信号 将 返回

高 和 这 ad974 将 又一次 重新开始 追踪 这 输入 信号.

下面 确实 情况 这

CS

管脚 能 是 系 低 和 r/

C

将 是 使用 至 决定 whether 你 是 初始的 一个 变换器-

sion 或者 读 数据. 在 这 第一 转换, 之后 这 ad974 是

powered 向上, 这 数据 输出 将 是 indeterminate.

转换 结果 能 是 clocked serially, 使用 也 一个

内部的 时钟 发生 用 这 ad974 或者 一个 外部 时钟.

这 ad974 是 配置 为 这 内部的 数据 时钟 模式 用

拉 这 ext/

INT

管脚 低. 它 是 配置 为 这 外部

时钟 模式 用 拉 这 ext/

INT

管脚 高.

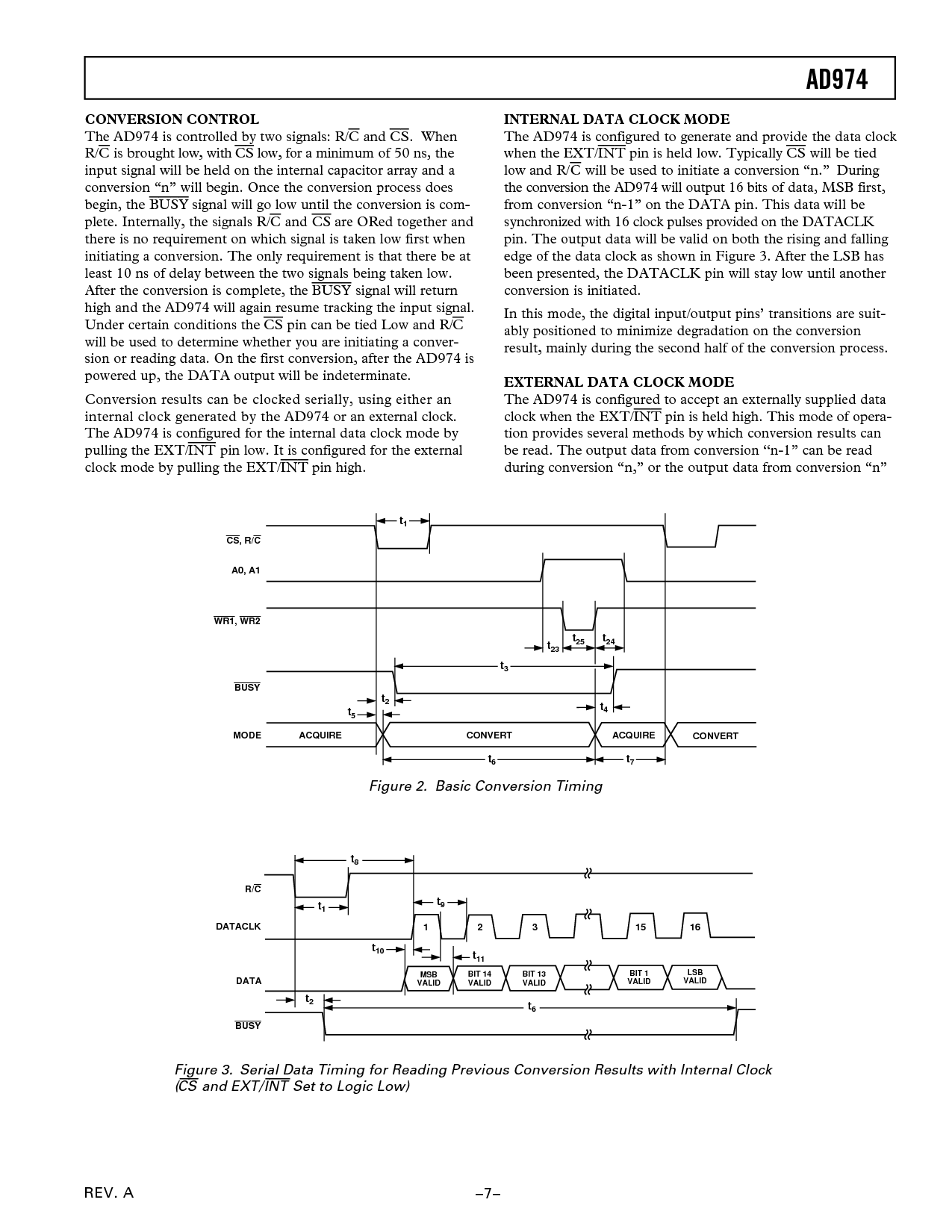

内部的 数据 时钟 模式

这 ad974 是 配置 至 发生 和 提供 这 数据 时钟

当 这 ext/

INT

管脚 是 使保持 低. 典型地

CS

将 是 系

低 和 r/

C

将 是 使用 至 initiate 一个 转换 “n.”在

这 转换 这 ad974 将 输出 16 位 的数据, msb 第一,

从 转换 “n-1” 在 这 数据 管脚. 这个 数据将 是

synchronized 和 16 时钟 脉冲 提供 在 这 dataclk

管脚. 这 输出 数据 将 是 有效的 在 两个都 这 rising 和 下落

边缘 的 这 数据 时钟 作 显示 在 图示 3. 之后 这 lsb 有

被 提交, 这 dataclk 管脚 将 停留 低 直到 另一

转换 是 initiated.

在 这个 模式, 这 数字的 输入/输出 管脚’ transitions 是 合适-

ably positioned 至 降低 降级 在 这 转换

结果, mainly 在 这 第二 half 的 这 转换 处理.

外部 数据 时钟 模式

这 ad974 是 配置 至 接受 一个 externally 有提供的 数据

时钟 当 这 ext/

INT

管脚 是 使保持 高. 这个 模式 的 opera-

tion 提供 一些 方法 用 这个 转换 结果 能

是 读. 这 输出 数据 从 转换 “n-1” 能 是 读

在 转换 “n,” 或者 这 输出 数据 从 转换 “n”

CS

, r/

C

BUSY

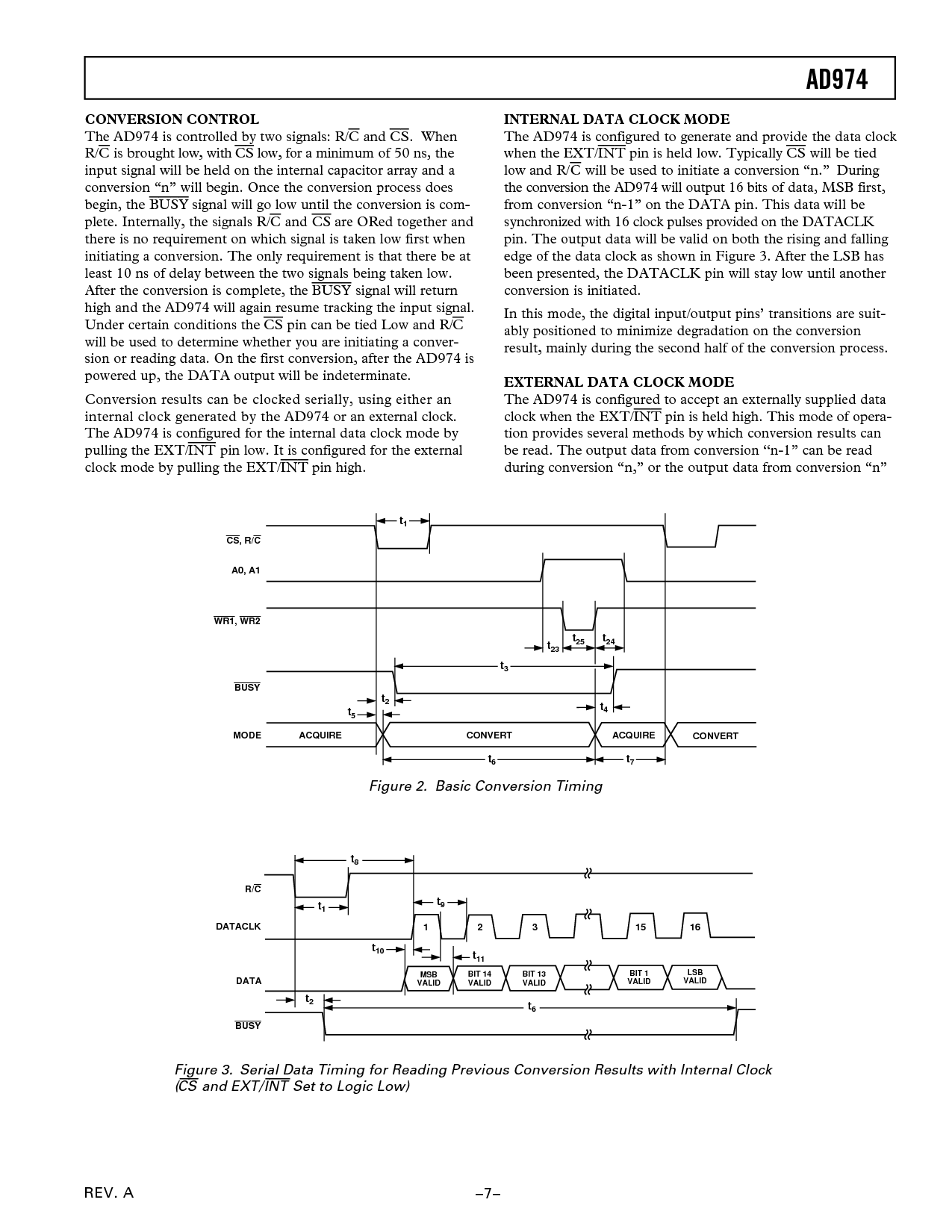

模式

ACQUIRE 转变

t

1

转变

ACQUIRE

t

3

t

2

t

5

t

6

t

4

t

7

t

23

t

25

t

24

a0, a1

WR1

,

WR2

图示 2. 基本 转换 定时

r/

C

DATACLK

数据

BUSY

1

MSB

有效的

位 14

有效的

t

8

t

1

t

9

2 3 15 16

t

10

t

11

位 13

有效的

位 1

有效的

LSB

有效的

t

2

t

6

图示 3. 串行 数据 定时 为 读 previous 转换 结果 和 内部的 时钟

(

CS

和 ext/

INT

设置 至 逻辑 低)