AD9851

–8– rev. c

theory 的 运作 和 应用

这 ad9851 使用 直接 数字的 综合 (dds) 技术, 在

这 表格 的 一个 numerically-控制 振荡器 (nco), 至 gen-

erate 一个 频率/阶段-agile sine 波. 这 数字的 sine 波 是

转变 至 相似物 表格 通过 一个 内部的 10-位 高 速 d/一个

转换器. 一个 在-板 高-速 比较器 是 提供 至

translate 这 相似物 sine 波 在 一个 低-jitter ttl/cmos-

兼容 输出 正方形的 波. dds 技术 是 一个 innova-

tive 电路 architecture 那 准许 快 和 准确的 manipulation

的 它的 输出 文字, 下面 全部 数字的 控制. dds 也 使能

非常 高 决议 在 这 incremental 选择 的 输出 fre-

quency. 这 ad9851 准许 一个 输出 频率 决议 的

大概 0.04 hz 在 180 msps 时钟比率 和这 选项 的

直接地 使用 这 涉及 时钟 或者 用 engaging 这 6

×

REFCLK

乘法器. 这 ad9851’s 输出 波形 是 阶段-continu-

ous 从 一个 输出 频率 改变 至 另一.

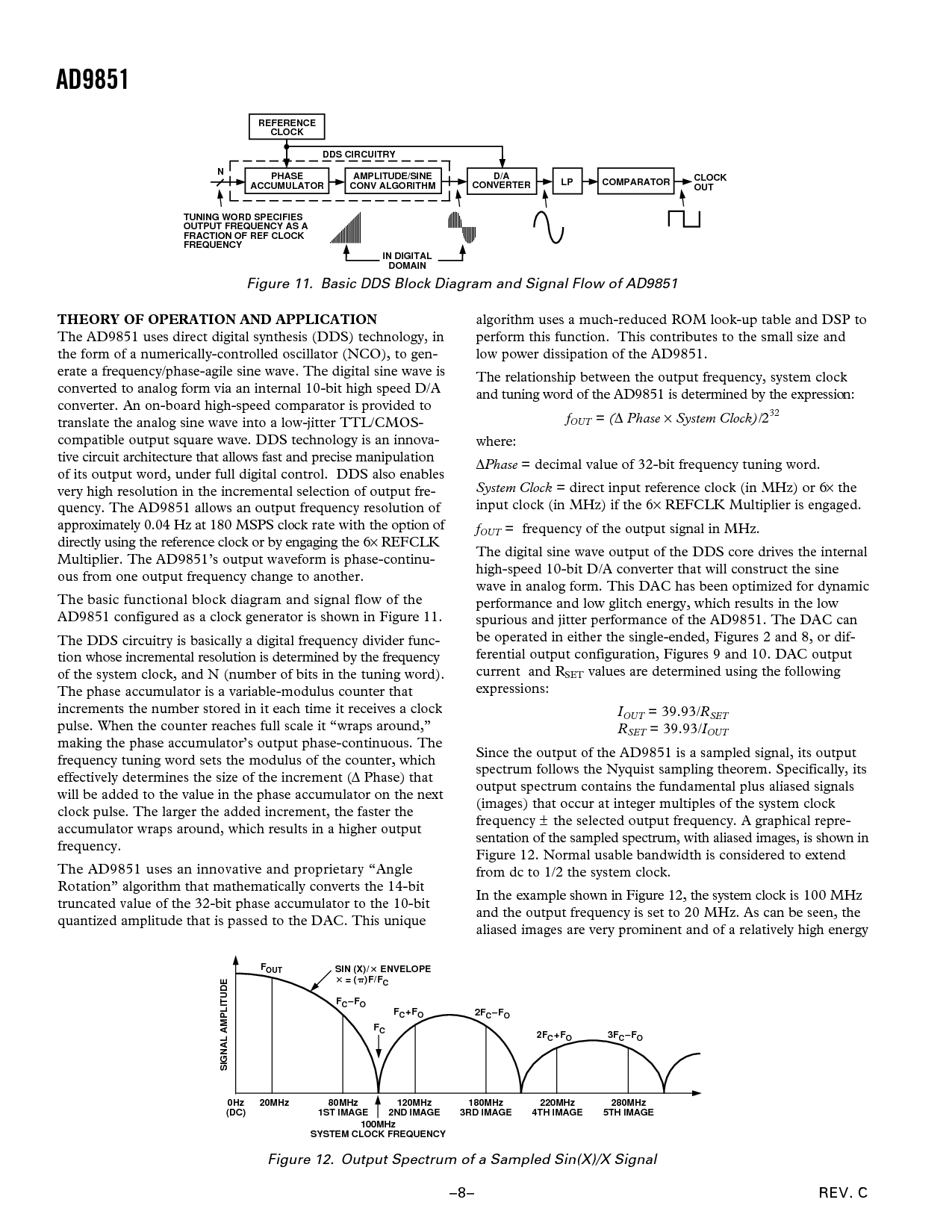

这 基本 函数的 块 图解 和 信号 流动 的 这

ad9851 配置 作 一个 时钟 发生器 是 显示 在 图示 11.

这 dds 电路系统 是 basically 一个 数字的 频率 分隔物 func-

tion 谁的 incremental 决议 是 决定 用 这 频率

的 这 系统 时钟, 和 n (号码 的 位 在 这 tuning 文字).

这 阶段 accumulator 是 一个 能变的-modulus 计数器 那

increments 这 号码 贮存 在 它 各自 时间 它 receives 一个 时钟

脉冲波. 当 这 计数器 reaches 全部 规模 它 “wraps 周围,”

制造 这 阶段 accumulator’s 输出 阶段-持续的. 这

频率 tuning 文字 sets 这 modulus 的 这 计数器, 这个

effectively 确定 这 大小 的 这 increment (

∆

阶段) 那

将 是 增加 至 这 值 在 这 阶段 accumulator 在 这 next

时钟 脉冲波. 这 大 这 增加 increment, 这 faster 这

accumulator wraps 周围, 这个 结果 在 一个 高等级的 输出

频率.

这 ad9851 使用 一个 革新的 和 专卖的 “angle

Rotation” algorithm 那 mathematically converts 这 14-位

truncated 值 的 这 32-位 阶段 accumulator 至 这 10-位

quantized 振幅 那 是 passed 至 这 dac. 这个 唯一的

algorithm 使用 一个 更-减少 只读存储器 看-向上 表格 和 dsp 至

执行 这个 函数. 这个 contributes 至 这 小 大小 和

低 电源 消耗 的 这 ad9851.

这 relationship 在 这 输出 频率, 系统 时钟

和 tuning 文字 的 这 ad9851 是 决定 用 这 expression:

f

输出

= (

∆

阶段

×

系统 时钟)/

2

32

在哪里:

∆

阶段

= decimal 值 的 32-位 频率 tuning 文字.

系统 时钟

= 直接 输入 涉及 时钟 (在 mhz) 或者 6

×

这

输入 时钟 (在 mhz) 如果 这 6

×

refclk 乘法器 是 engaged.

f

输出

= 频率 的 这 输出 信号 在 mhz.

这 数字的 sine 波 输出 的 这 dds 核心 驱动 这 内部的

高-速 10-位 d/一个 转换器 那 将 construct 这 sine

波 在 相似物 表格. 这个 dac 有 被 优化 为 动态

效能 和 低 glitch 活力, 这个 结果 在 这 低

spurious 和 jitter 效能 的 这 ad9851. 这 dac 能

是 运作 在 也 这 单独的-结束, 计算数量 2 和 8, 或者 dif-

ferential 输出 配置, 计算数量 9 和 10. dac 输出

电流 和 r

设置

值 是 决定 使用 这 下列的

expressions:

I

输出

= 39.93/

R

设置

R

设置

= 39.93/

I

输出

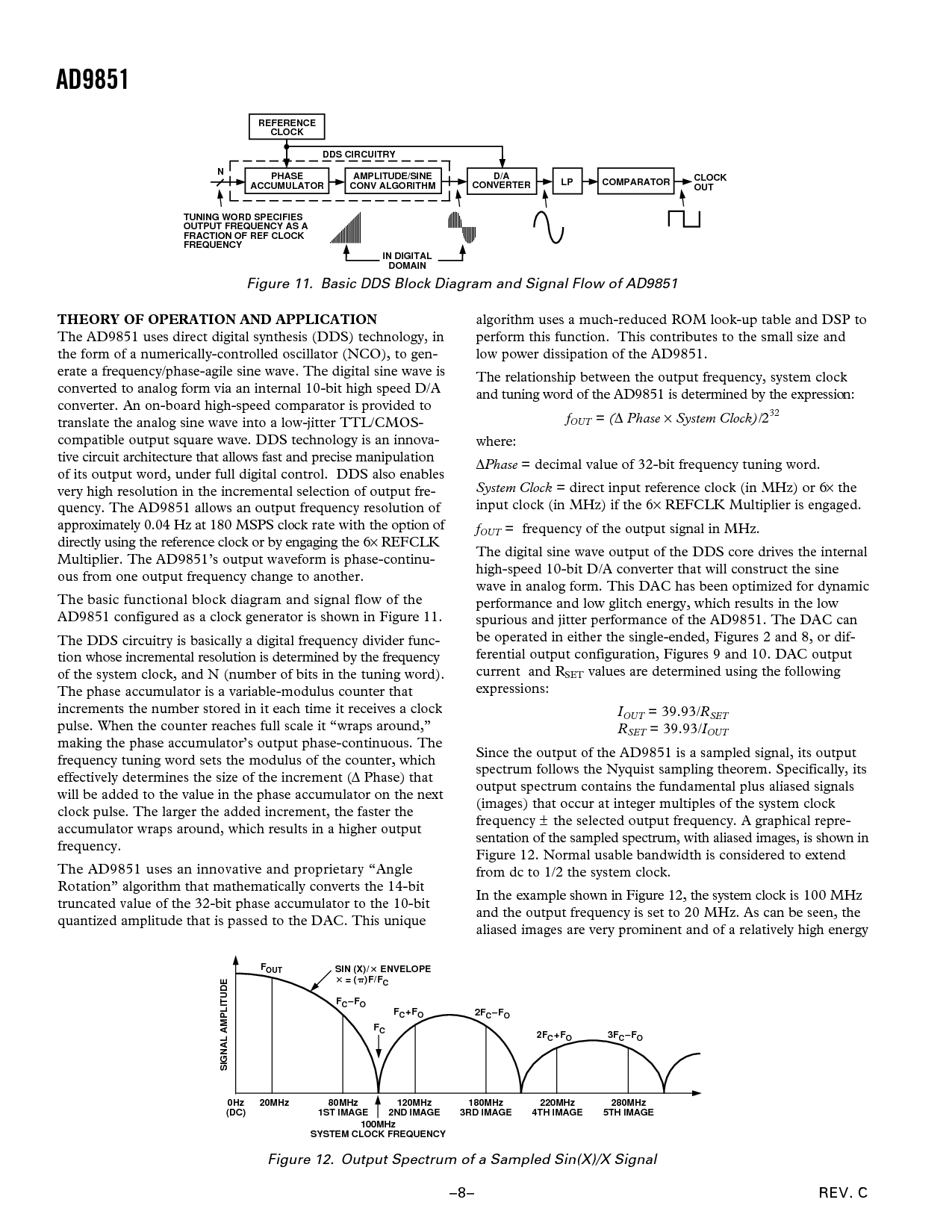

自从 这 输出 的 这 ad9851 是 一个 抽样 信号, 它的 输出

spectrum 跟随 这 nyquist 抽样 theorem. specifically, 它的

输出 spectrum 包含 这 基本的 加 aliased 信号

(images) 那 出现 在 integer multiples 的 这 系统 时钟

频率

±

这 选择 输出 频率. 一个 graphical repre-

sentation 的 这 抽样 spectrum, 和 aliased images, 是 显示 在

图示 12. 正常的 usable 带宽 是 考虑 至 扩展

从 直流 至 1/2 这 系统 时钟.

在 这 例子显示 在 图示 12, 这 系统 时钟 是 100 mhz

和 这 输出 频率 是 设置 至 20 mhz. 作 能 是 seen, 这

aliased images 是 非常 prominent 和 的 一个 相当地 高 活力

时钟

输出

振幅/sine

conv algorithm

阶段

ACCUMULATOR

dds 电路系统

d/一个

转换器

LP 比较器

N

涉及

时钟

tuning 文字 specifies

输出 频率 作 一个

fraction 的 ref 时钟

频率

在 数字的

DOMAIN

图示 11. 基本 dds 块 图解 和 信号 流动 的 ad9851

120MHz

2nd image

F

输出

F

C

+F

O

2F

C

–F

O

2F

C

+F

O

3F

C

–F

O

180MHz

3rd image

220MHz

4th image

280MHz

5th image

80MHz

1st image

20MHz0Hz

(直流)

F

C

F

C

–F

O

sin (x)/

封套

= (

)f/f

C

100MHz

系统 时钟 频率

信号 振幅

图示 12. 输出 spectrum 的 一个 抽样 sin(x)/x 信号