®

5

dac7800, 01, 02

DAC7800

(内容)

数据

CS

CLK

t

1

t

5

upd 一个

upd b

t

3

t

7

CLR

t

6

t

8

t

4

0V

5V

5V

5V

5V

0V

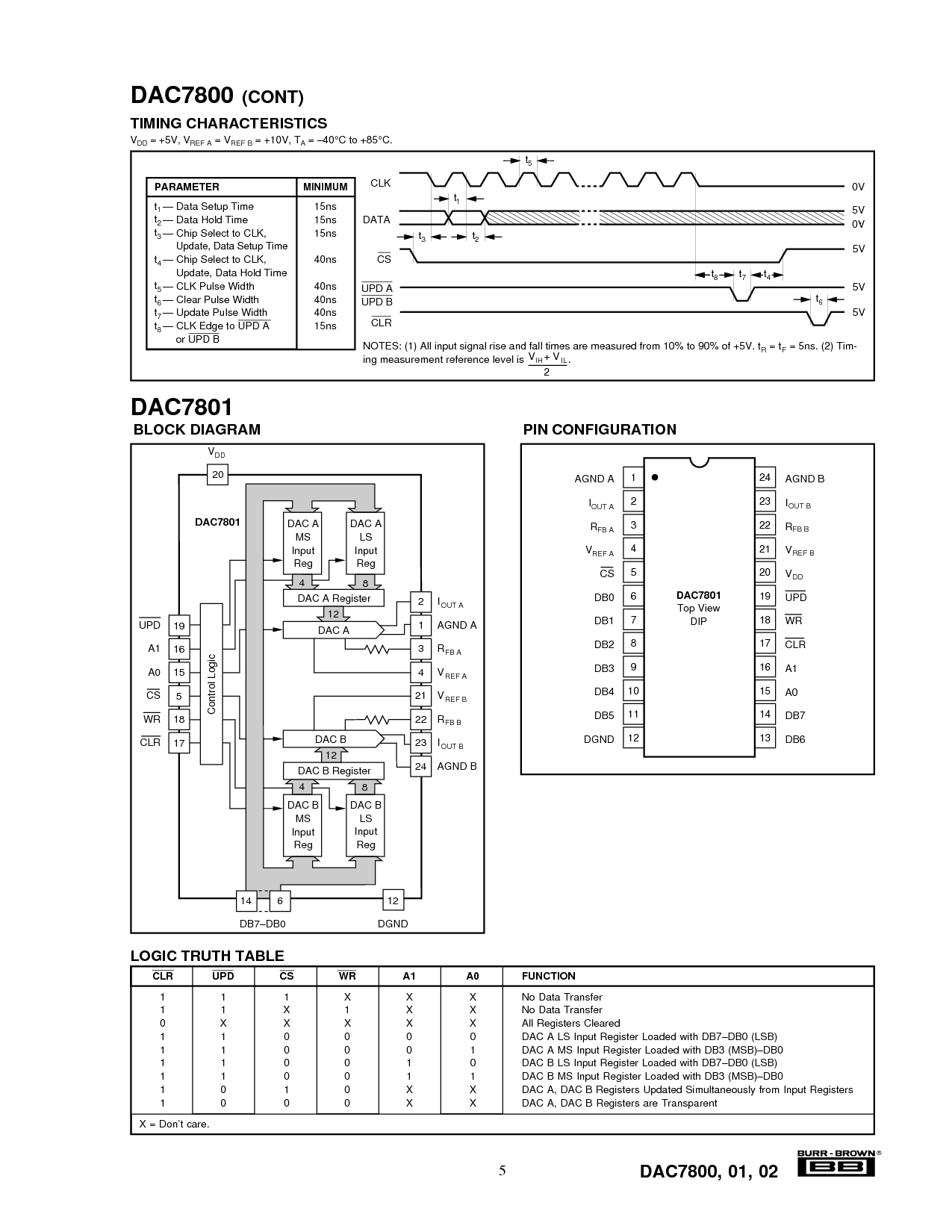

注释: (1) 所有 输入 信号 上升 和 下降 时间 是 量过的 从 10% 至 90% 的 +5v. t = t = 5ns. (2) tim-

ing 度量 涉及 水平的 是

v + v

2

FR

IH IL

.

t

2

参数

最小

t

1

— 数据 建制 时间 15ns

t

2

— 数据 支撑 时间 15ns

t

3

— 碎片 选择 至 clk, 15ns

更新, 数据 建制 时间

t

4

— 碎片 选择 至 clk, 40ns

更新, 数据 支撑 时间

t

5

— clk 脉冲波 宽度 40ns

t

6

— clear 脉冲波 宽度 40ns

t

7

— 更新 脉冲波 宽度 40ns

t

8

— clk 边缘 至 upd 一个 15ns

或者 upd b

定时 特性

V

DD

= +5v, v

ref 一个

= v

ref b

= +10v, t

一个

= –40

°

c 至 +85

°

c.

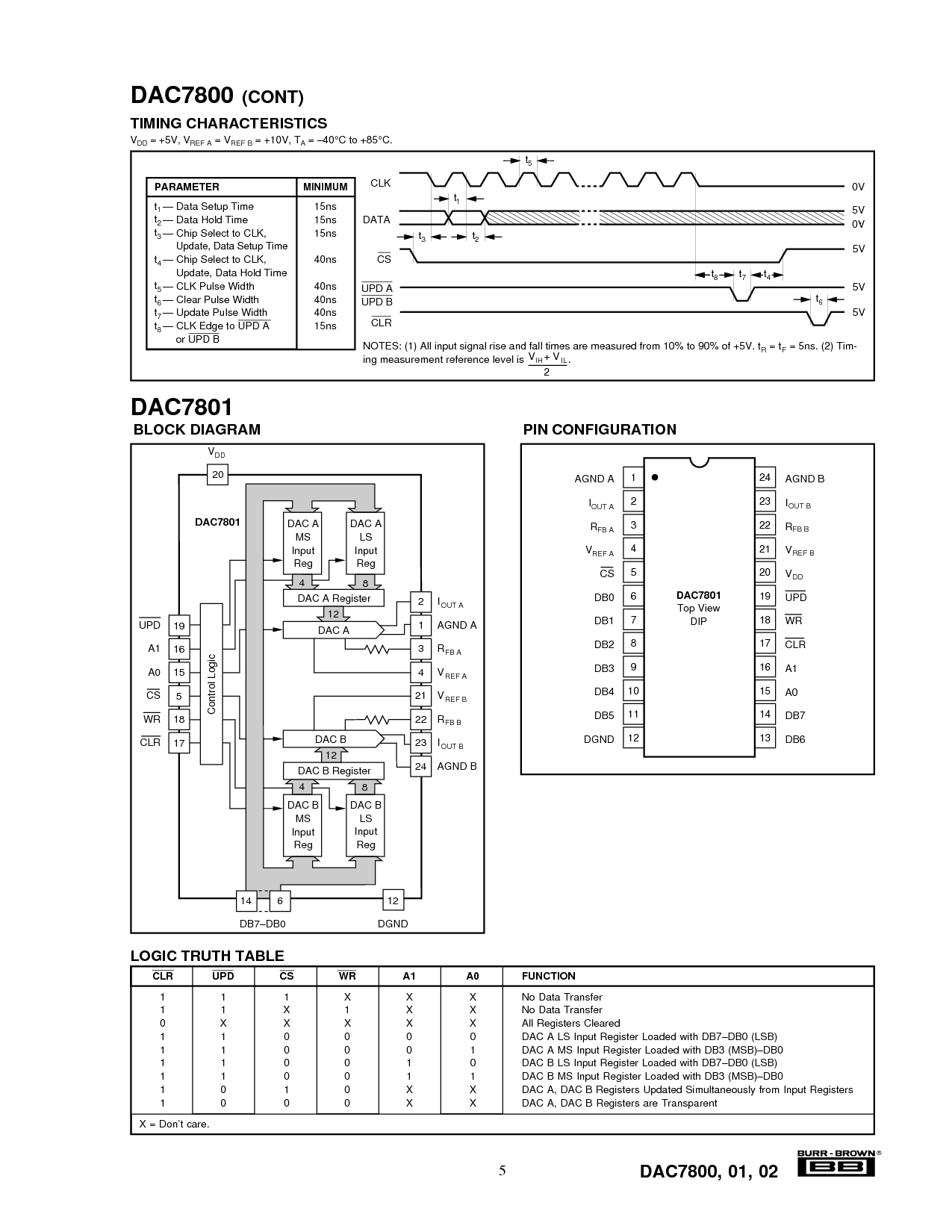

逻辑 真实 表格

dac 一个

I

agnd 一个

R

V

V

R

I

agnd b

输出 一个

fb 一个

ref 一个

ref b

fb b

输出 b

20

V

DD

2

1

3

4

21

22

23

24

dac 一个 寄存器

4

8

dac 一个

LS

输入

Reg

dac 一个

MS

输入

Reg

控制 逻辑

dac b

dac b 寄存器

4

8

12

DGND

dac b

LS

输入

Reg

dac b

MS

输入

Reg

19

16

15

5

18

17

UPD

A1

A0

CS

WR

CLR

DAC7801

14 6

DB7–DB0

12

12

块 图解 管脚 配置

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

agnd 一个

CS

DB0

DB1

DB2

DB3

DB4

DB5

DGND

agnd b

I

R

V

V

UPD

WR

CLR

A1

A0

DB7

DB6

输出 一个

fb 一个

ref 一个

fb b

ref b

DD

输出 b

DAC7801

顶 视图

插件

I

R

V

DAC7801

CLR UPD CS WR A1 A0 函数

1 1 1 X X X 非 数据 转移

1 1 X 1 X X 非 数据 转移

0 X X X X X 所有 寄存器 cleared

1 1 0 0 0 0 dac 一个 ls 输入 寄存器 承载 和 db7–db0 (lsb)

1 1 0 0 0 1 dac 一个 ms 输入 寄存器 承载 和 db3 (msb)–db0

1 1 0 0 1 0 dac b ls 输入 寄存器 承载 和 db7–db0 (lsb)

1 1 0 0 1 1 dac b ms 输入 寄存器 承载 和 db3 (msb)–db0

1 0 1 0 X X dac 一个, dac b 寄存器 updated 同时发生地 从 输入 寄存器

1 0 0 0 X X dac 一个, dac b 寄存器 是 transparent

x = don’t 小心.