adsp-bf561初步的 技术的 数据

rev. prc | 页 5 的 52 | april 2004

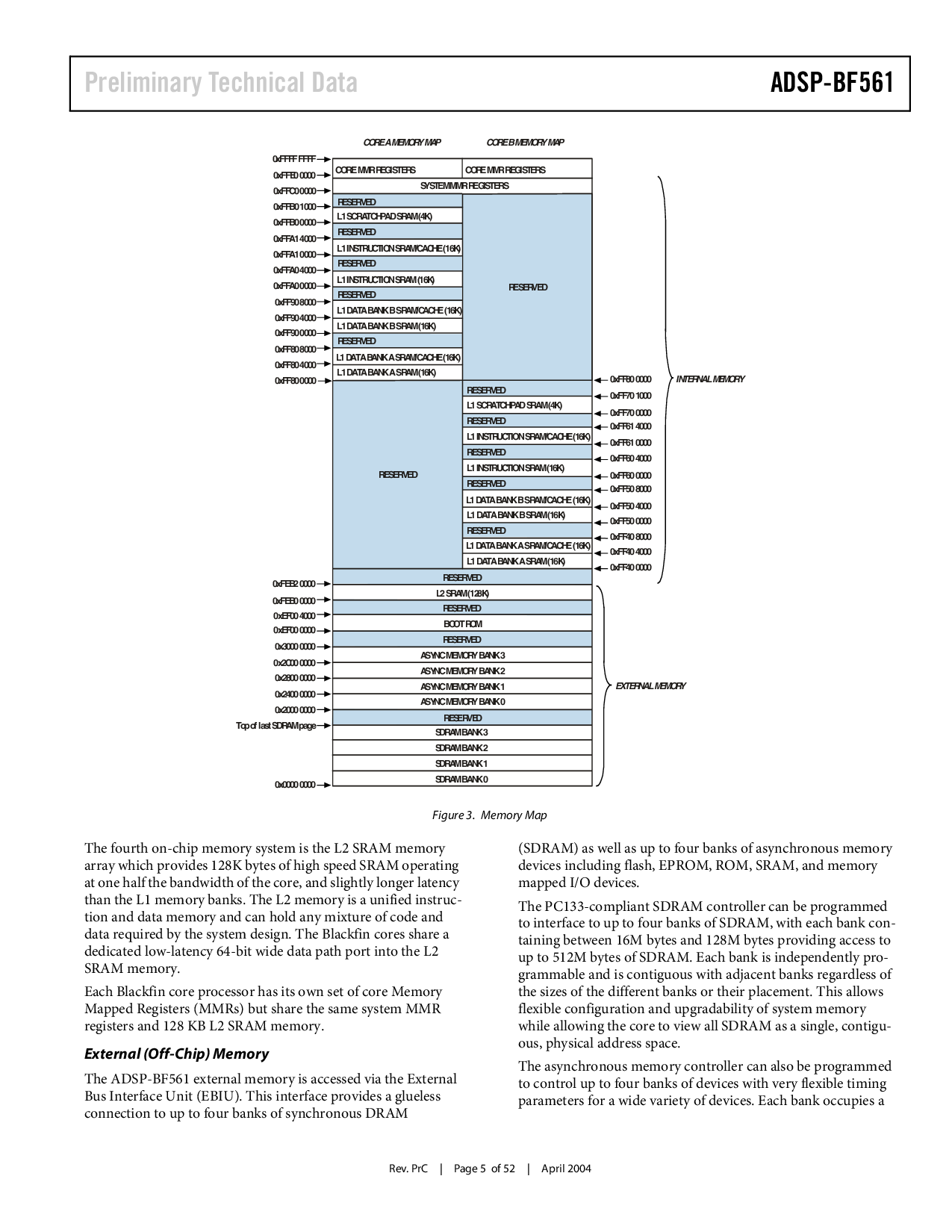

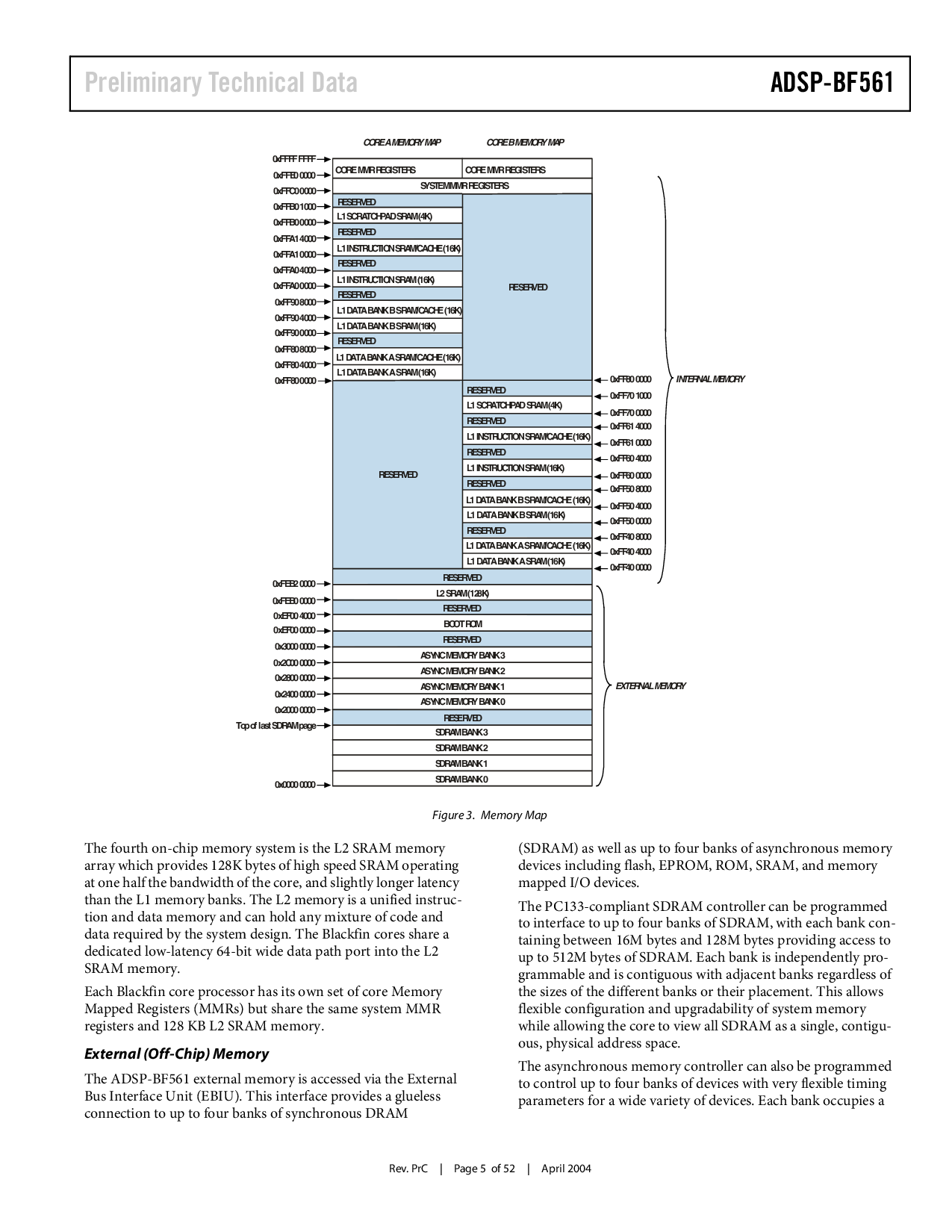

这 fourth 在-碎片 记忆 system 是 这 l2 sram 记忆

排列 这个 提供 128k 字节的 高 速 sram 运行

在 一个 half 这 带宽 的 这 核心, 和 slightly 变长 latency

比 这 l1 记忆 banks. 这 l2 记忆 是 一个 unified instruc-

tion 和 数据 记忆 和 能 支撑 任何 mixture 的 代号 和

数据 必需的 用 这 系统 design. 这 blackfin cores share 一个

专心致志的 低-latency 64-位 宽 数据 path 端口 在 这 l2

sram 记忆.

各自 blackfin 核心 处理器 has 它的 自己的 设置 的 核心 记忆

编排 寄存器 (mmrs) 但是share 这 一样 系统 mmr

寄存器 和 128 kb l2 sram 记忆.

外部 (止-碎片) 记忆

这 adsp-bf561 外部 记忆 是 accessed 通过 这 外部

总线 接口 单位 (ebiu). 这个接口 提供 一个 glueless

连接 至 向上 至 四 banks 的同步的 dram

(sdram) 作 好 作 向上 至 四banks 的 异步的 记忆

设备 包含 flash, eprom, 只读存储器, sram, 和 记忆

编排 i/o 设备.

这 pc133-一致的 sdram 内容roller 能 是 编写程序

至 接口 至 向上 至 四 banks 的 sdram, 和 各自 bank con-

taining 在 16m字节 和 128m 字节供应 进入 至

向上 至 512m 字节 的 sdram. each bank 是 independently pro-

grammable 和 是 相接的 和调整 banks regardless 的

这 sizes 的 这 different banks 或者 它们的 placement. 这个 准许

有伸缩性的 配置 和 upgradability 的 系统 记忆

当 准许 这 核心 至 视图所有 sdram 作 一个 单独的, contigu-

ous, 物理的 地址 空间.

这 异步的 记忆 内容roller 能 也 是 编写程序

至 控制 向上 至 四 banks 的 devices 和 非常 有伸缩性的 定时

参数 为 一个 宽 多样性 的 设备. 各自 bank occupies 一个

图示 3. 记忆 编排

保留

ASYNC 记忆 BANK 3

ASYNC 记忆 BANK 2

ASYNC 记忆 BANK 1

ASYNC 记忆 BANK 0

0xFF80 0000

0xFF70 1000

0xFF70 0000

0xFF61 4000

0xFF50 4000

0xFF50 0000

0xFF40 8000

0xFF40 4000

0xFF61 0000

0xFF60 4000

0xFF60 0000

0xFF50 8000

0xFF40 0000

L1 SCRATCHPAD SRAM (4k)

L1 INSTRUCTI 在 sram/ CACHE (16k)

L1 INSTRUCTI 在 SRAM (16k)

L1 数据 BANK B sram/ CACHE ( 16k)

L1 数据 BANK B SRAM (16k)

L1 数据 BANK 一个 sram/CACHE ( 16k)

L1 数据 BANK 一个 SRAM (16k)

COREAMEMORYMAP COREBMEMORYMAP

核心 MMR REGISTERS 核心 MMR REGI STERS

系统MMR REGISTERS

L1 SCRATCHPAD SRAM ( 4k)

保留

L1 INSTRUCTI在 sram/cache ( 16k)

L1 INSTRUCTI 在 SRAM (16k)

L1 数据 BANK B sram/ CACHE (16k)

L1 数据 BANK B SRAM (16k)

L1 数据 BANK 一个 sram/ CACHE (16k)

L1 数据 BANK 一个 SRAM (16k)

L2 SRAM (128k)

激励 只读存储器

SDRAM BANK 3

SDRAM BANK 2

SDRAM BANK 1

SDRAM BANK 0

0xFFE0 0000

0xFFC0 0000

0xFFB0 1000

0xFFB0 0000

0xFFA1 4000

0xFFA1 0000

0xFFA0 4000

0xFFA0 0000

0xFF90 8000

0xFF90 4000

0xFF90 0000

0xFF80 8000

0xFF80 4000

0xFEB2 0000

0xFEB0 0000

0xEF00 4000

0xEF00 0000

0x3000 0000

0x2C00 0000

0x2800 0000

0x2400 0000

0x2000 0000

0x0000 0000

保留

INTERNAL 记忆

外部 记忆

0xFFFF FFFF

TopoflastSDRAMpage

保留

保留

保留

保留

保留

保留

保留

保留

保留

保留

保留

保留

保留

0xFF80 0000