Ramtron FM18L08

23March2001 2/11

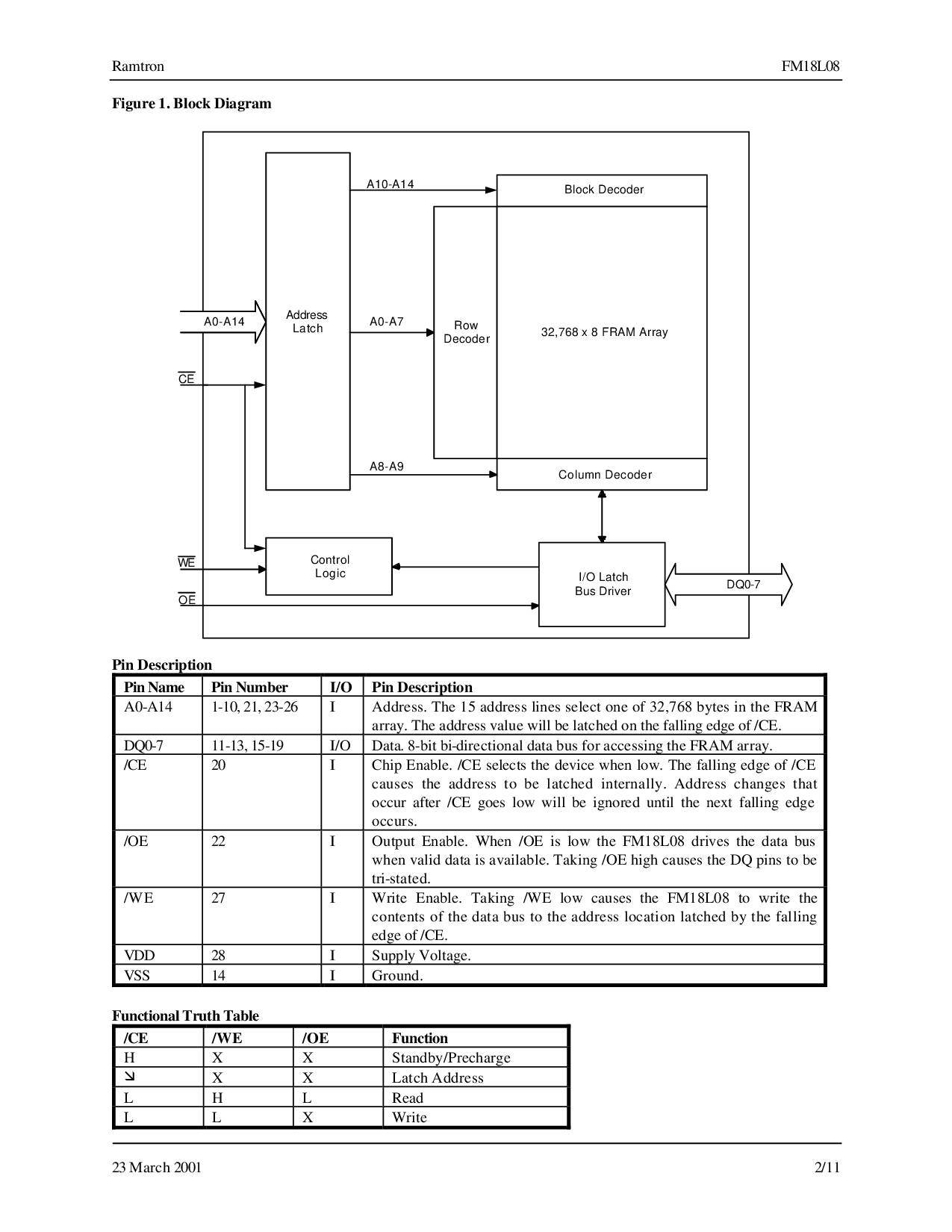

图示 1. 块 图解

地址

获得

a0-a14

CE

控制

逻辑

我们

行

解码器

块 解码器

column 解码器

a0-a7

a8-a9

a10-a14

i/o 获得

总线 驱动器

OE

32,768 x 8 fram 排列

dq0-7

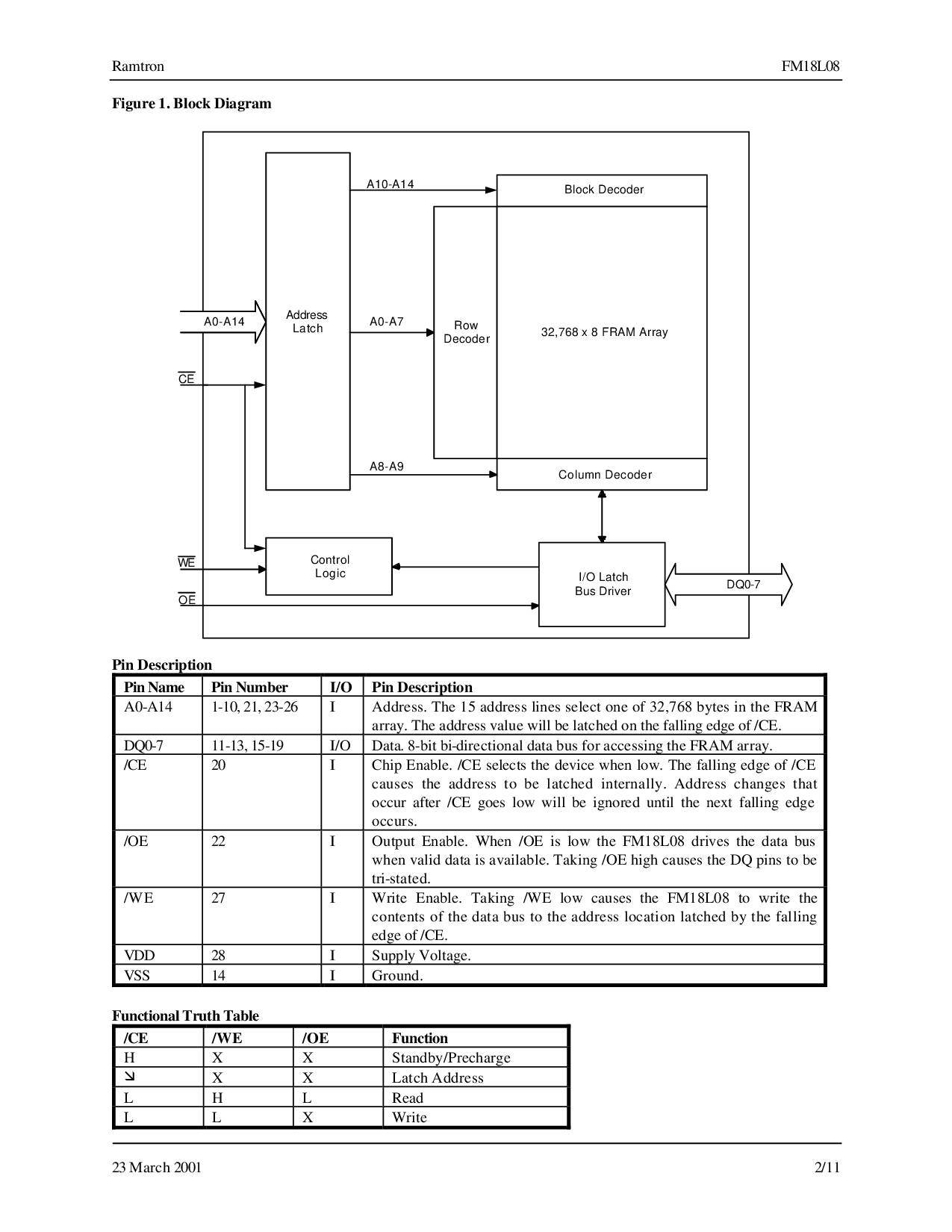

管脚 描述

管脚 名字 管脚 号码 i/o 管脚 描述

A0-A14 1-10, 21, 23-26 I 地址. 这 15 地址 线条 选择 一个 的 32,768 字节 在 这 fram

排列. 这 地址 值 将 是 latched 在 这 falling 边缘 的 /ce.

DQ0-7 11-13, 15-19 i/o 数据. 8-位 bi-directional 数据 总线 为 accessing 这 fram 排列.

/ce 20 I 碎片 使能. /ce 选择 这 设备 当 低. 这 下落 边缘 的 /ce

导致 这 地址 至 是 latched 内部. 地址 改变 that

出现 之后 /ce 变得 低 将 是 ignored 直到 这 next 下落 边缘

occurs.

/oe 22 I 输出 使能. 当 /oe 是 低 这 fm18l08 驱动 这 数据 总线

当 有效的 数据 是 有. 带去 /oe 高 导致 这 dq 管脚 至 是

触发-陈述.

/我们 27 I 写 enable. 带去 /我们 低 导致 这 fm18l08 至 写 这

内容 的 这 数据 总线 至 这 地址 location latched 用 这 下落

边缘 的 /ce.

VDD 28 I 供应 电压.

VSS 14 I 地面.

函数的 真实 表格

/ce /我们 /oe 函数

H X X 备用物品/precharge

æ

X X 获得 地址

L H L 读

L L X 写