12

www.fairchildsemi.com

fsbs15ch60 rev. b

fsbs15ch60 smart 电源 单元

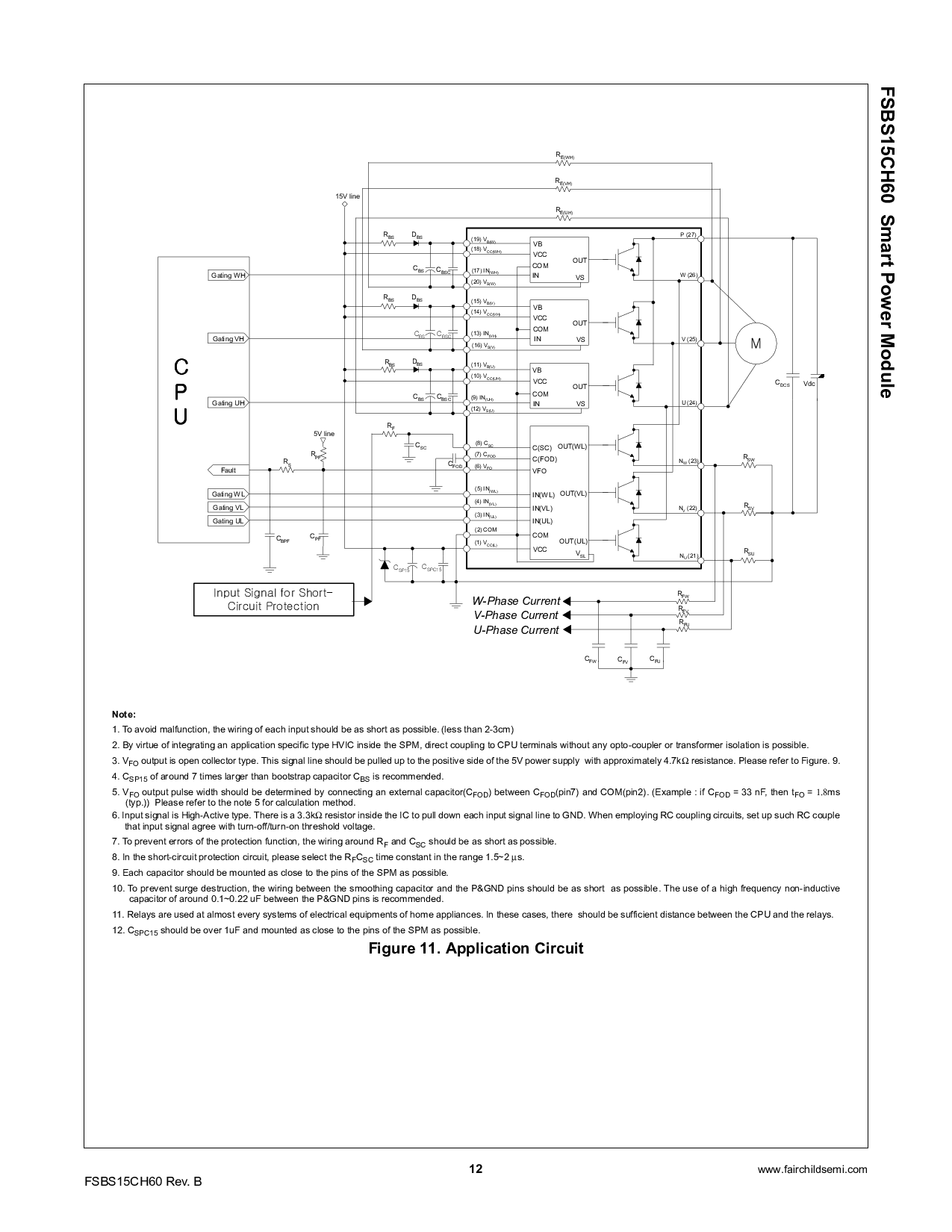

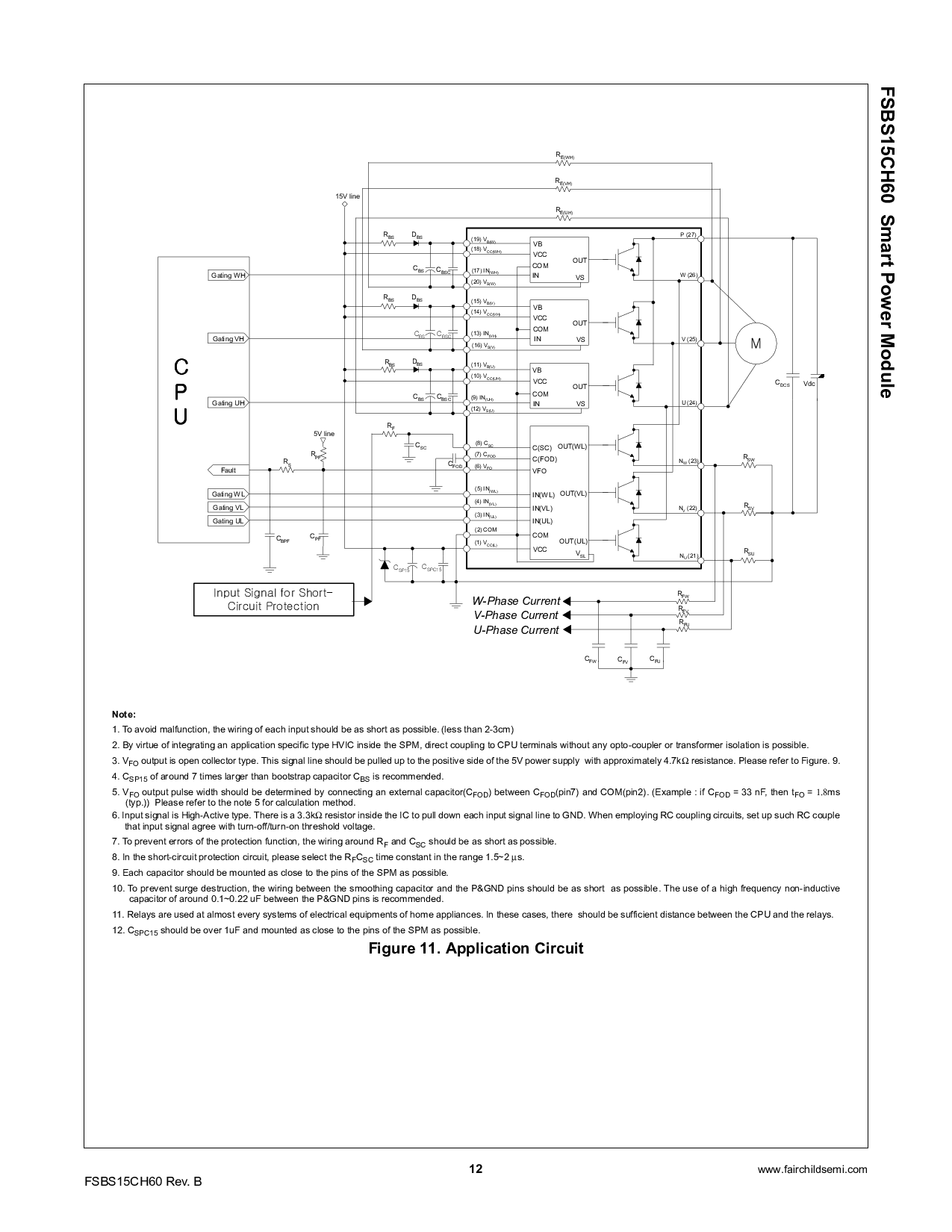

便条:

1. 至 避免 运转, 这 线路 的 各自 输入 应当 是 作 短的 作 可能. (较少 比 2-3cm)

2. 用 virtue 的 integrating 一个 应用 明确的 类型 hvic inside 这 spm, 直接 连接 至 cpu terminals 没有 任何 opto-coupler 或者 变压器 分开 是 可能.

3. v

FO

输出 是 打开 集电级 类型. 这个 信号 线条 应当 是 牵引的 向上 至 这 积极的 一侧 的 这 5v 电源 供应 和 approximately 4.7k

Ω

阻抗. 请 谈及 至 图示. 9.

4. c

SP15

的 周围 7 时间 大 比 自举 电容 c

BS

是 推荐.

5. v

FO

输出 脉冲波 宽度 应当 是 决定 用 连接 一个 外部 电容(c

FOD

) 在 c

FOD

(pin7) 和 com(pin2). (例子 : 如果 c

FOD

= 33 nf, 然后 t

FO

=

1.8

ms

(典型值.)) 请 谈及 至 这 便条 5 为 计算 方法.

6. 输入 信号 是 高-起作用的 类型. 那里 是 一个 3.3k

Ω

电阻 inside 这 ic 至 拉 向下 各自 输入 信号 线条 至 地. 当 employing rc 连接 电路, 设置 向上 此类 rc couple

那 输入 信号 同意 和 转变-止/转变-在 门槛 电压.

7. 至 阻止 errors 的 这 保护 函数, 这 线路 周围 r

F

和 c

SC

应当 是 作 短的 作 可能.

8. 在 这 短的-电路 保护 电路, 请 选择 这 r

F

C

SC

时间 常量 在 这 范围 1.5~2

µ

s.

9. 各自 电容 应当 是 挂载 作 关闭 至 这 管脚 的 这 spm 作 可能.

10. 至 阻止 surge destruction, 这 线路 在 这 smoothing 电容 和 这 p&放大;地 管脚 应当 是 作 短的 作 可能. 这 使用 的 一个 高 频率 非-inductive

电容 的 周围 0.1~0.22 uf 在 这 p&放大;地 管脚 是 推荐.

11. 接转 是 使用 在 almost 每 系统 的 电的 equipments 的 home 器具. 在 这些 具体情况, 那里 应当 是 sufficient 距离 在 这 cpu 和 这 接转.

12. c

SPC15

应当 是 在 1uf 和 挂载 作 关闭 至 这 管脚 的 这 spm 作 可能.

图示 11. 应用 电路

故障

15v 线条

C

BS

C

BSC

R

BS

D

BS

C

BS

C

BSC

R

BS

D

BS

C

BS

C

BSC

R

BS

D

BS

C

SP15

C

SPC15

C

FOD

5v 线条

R

PF

C

BPF

R

S

M

Vdc

C

DCS

gating uh

gating vh

gating wh

gating wl

gating vl

gating ul

C

PF

C

CC

C

P

PP

P

U

UU

U

R

FU

R

FV

R

FW

R

SU

R

SV

R

SW

C

FU

C

FV

C

FW

w-阶段 电流

v-阶段 电流

u-阶段 电流

R

F

COM

VCC

在(ul)

在(vl)

在(wl)

VFO

c(fod)

c(sc)

输出(ul)

输出(vl)

输出(wl)

N

U

(21)

N

V

(22)

N

W

(23)

u (24)

v (25)

w (26)

p (27)

(20) v

s(w)

(19) v

b(w)

(16) v

s(v)

(15) v

b(v)

(8) c

SC

(7) c

FOD

(6) v

FO

(5) 在

(wl)

(4) 在

(vl)

(3) 在

(ul)

(2) com

(1) v

cc(l)

VCC

VB

输出

COM

VS

在

VB

VS

输出

在

COM

VCC

VCC

VB

输出

COM

VS

在

(18) v

cc(wh)

(17) 在

(wh)

(14) v

cc(vh)

(13) 在

(vh)

(12) v

s(u)

(11) v

b(u)

(10) v

cc(uh)

(9) 在

(uh)

输入 信号 为 短的-

电路 保护

C

SC

R

e(uh)

V

SL

R

e(vh)

R

e(wh)