5

HIP4081A

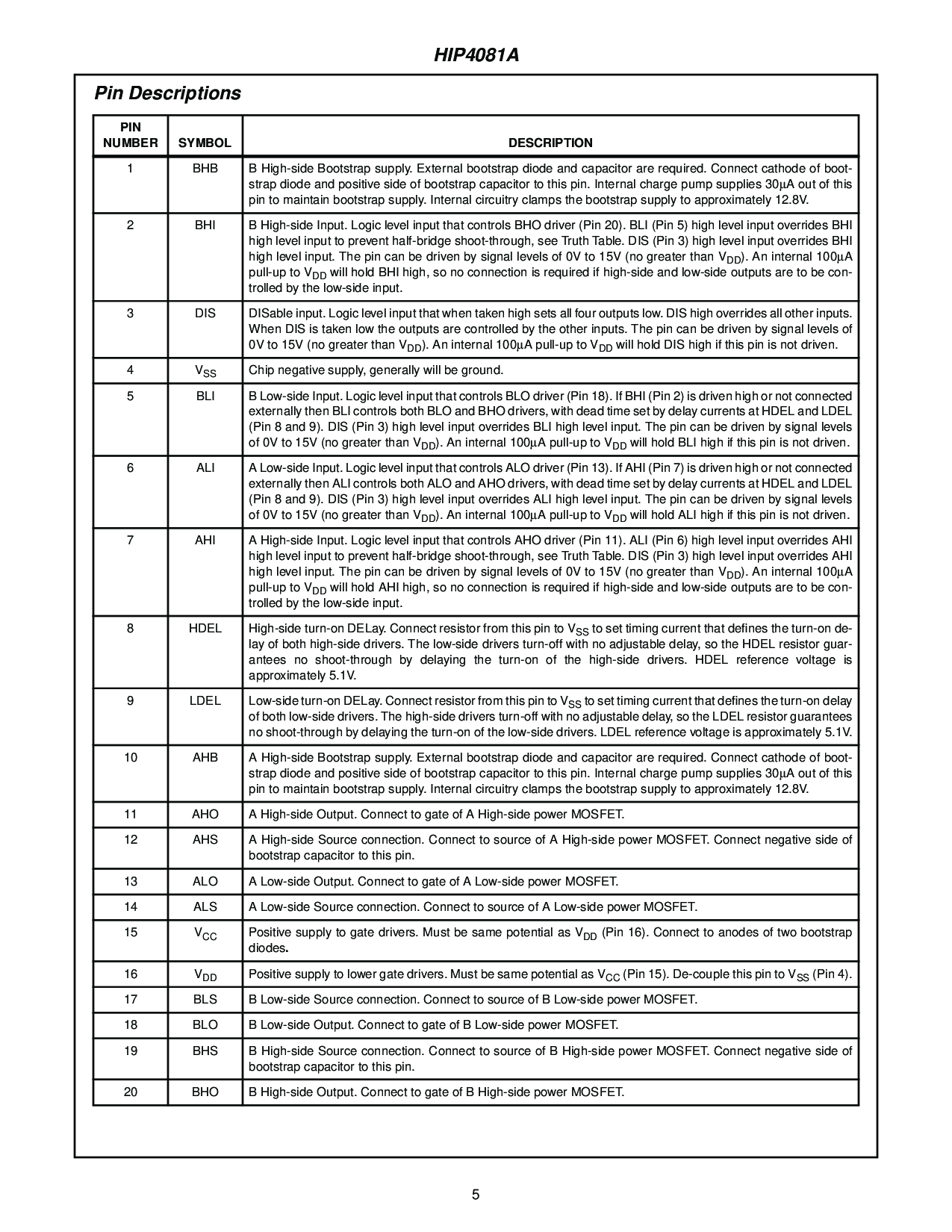

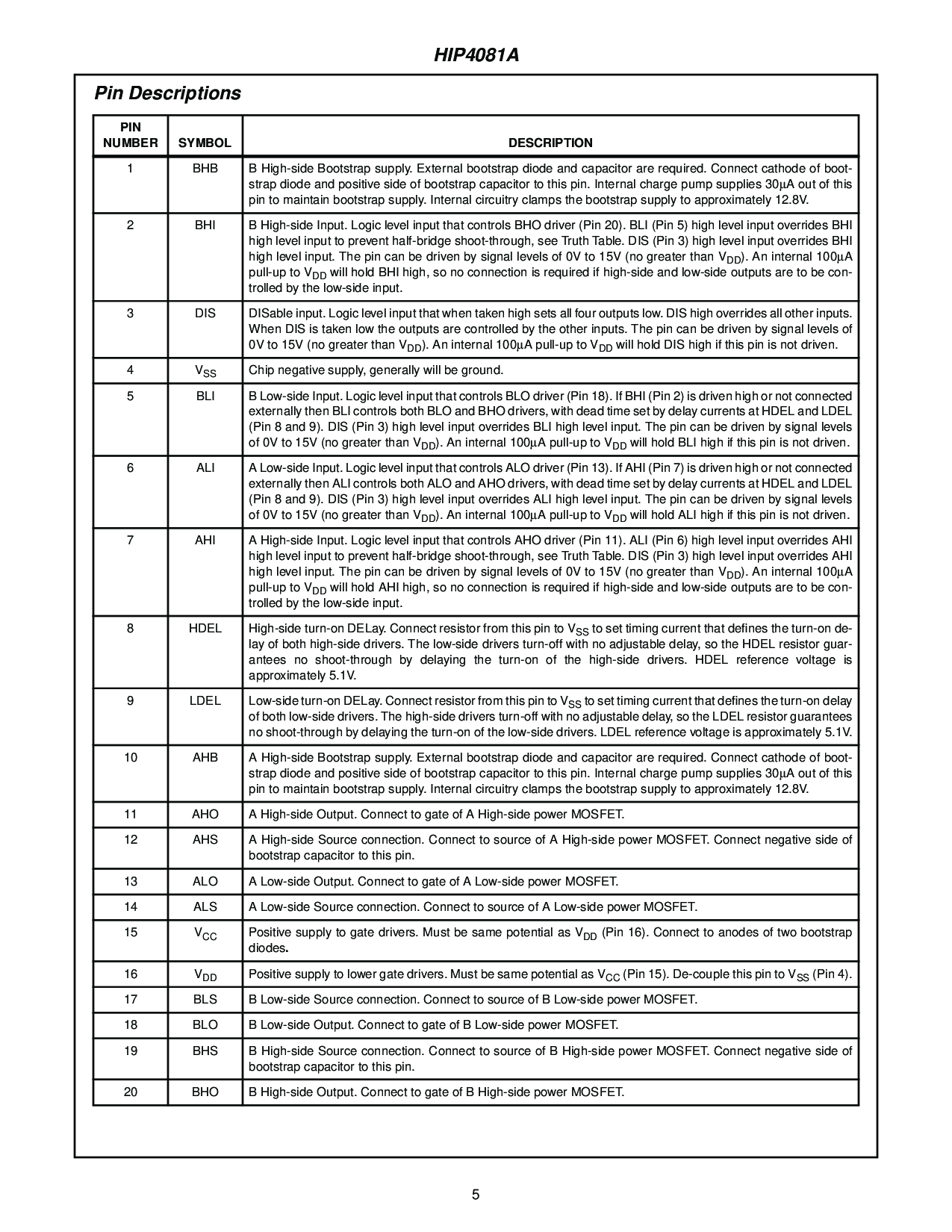

管脚 说明

管脚

号码 符号 描述

1 BHB b 高侧 引导程序 供应. 外部 引导程序 二极管 和 电容器 是 必填项. 连接 阴极 的 引导-

绑带 二极管 和 正 侧面 的 引导程序 电容器 至 这个 管脚. 内部 费用 泵 供应品 30

µ

一个 出点 的 这个

管脚 至 维护 引导程序 供应. 内部 电路 卡箍 这 引导程序 供应 至 大约 12.8v.

2 BHI b 高侧 输入. 逻辑 水平 输入 那 控件 bho 驾驶员 (管脚 20). bli (管脚 5) 高 水平 输入 覆盖 bhi

高 水平 输入 至 防止 半桥 射击-通过, 请参见 真相 表. dis (管脚 3) 高 水平 输入 覆盖 bhi

高 水平 输入. 这 管脚 可以 是 驱动 由 信号 级别 的 0v 至 15v (否 更大 比 v

dd

). 一个 内部 100

µ

一个

上拉 至 v

dd

将 保持 bhi 高, 所以 否 连接 是 必填项 如果 高侧 和 低侧 产出 是 至 是 con-

被控制 由 这 低侧 输入.

3 dis 禁用 输入. 逻辑 水平 输入 那 当 已拍摄 高 集 全部 四 产出 低. dis 高 覆盖 全部 其他 输入.

当 dis 是 已拍摄 低 这 产出 是 受控 由 这 其他 输入. 这 管脚 可以 是 驱动 由 信号 级别 的

0v 至 15v (否 更大 比 v

dd

). 一个 内部 100

µ

一个 上拉 至 v

dd

将 保持 dis 高 如果 这个 管脚 是 不 驱动.

4V

ss

芯片 负 供应, 一般 将 是 接地.

5 BLI b 低侧 输入. 逻辑 水平 输入 那 控件 blo 驾驶员 (管脚 18). 如果 bhi (管脚 2) 是 驱动 高 或 不 已连接

外部 然后 bli 控件 两者都有 blo 和 bho 驱动程序, 与 死了 时间 设置 由 延迟 电流 在 hdel 和 ldel

(管脚 8 和 9). dis (管脚 3) 高 水平 输入 覆盖 bli 高 水平 input. 这 管脚 可以 是 驱动 由 信号 级别

的 0v 至 15v (否 更大 比 v

dd

). 一个 内部 100

µ

一个 上拉 至 v

dd

将 保持 bli 高 如果 这个 管脚 是 不 驱动.

6 ALI 一个 低侧 输入. 逻辑 水平 输入 那 控件 alo 驾驶员 (管脚 13). 如果 ahi (管脚 7) 是 驱动 高 或 不 已连接

外部 然后 ali 控件 两者都有 alo 和 aho 驱动程序, 与 死了 时间 设置 由 延迟 电流 在 hdel 和 ldel

(管脚 8 和 9). dis (管脚 3) 高 水平 输入 覆盖 ali 高 水平 input. 这 管脚 可以 是 驱动 由 信号 级别

的 0v 至 15v (否 更大 比 v

dd

). 一个 内部 100

µ

一个 上拉 至 v

dd

将 保持 ali 高 如果 这个 管脚 是 不 驱动.

7 AHI 一个 高侧 输入. 逻辑 水平 输入 那 控件 aho 驾驶员 (管脚 11). ali (管脚 6) 高 水平 输入 覆盖 ahi

高 水平 输入 至 防止 半桥 射击-通过, 请参见 真相 表. dis (管脚 3) 高 水平 输入 覆盖 ahi

高 水平 输入. 这 管脚 可以 是 驱动 由 信号 级别 的 0v 至 15v (否 更大 比 v

dd

). 一个 内部 100

µ

一个

上拉 至 v

dd

将 保持 ahi 高, 所以 否 连接 是 必填项 如果 高侧 和 低侧 产出 是 至 是 con-

被控制 由 这 低侧 输入.

8 HDEL 高侧 打开 延迟. 连接 电阻 从 这个 管脚 至 v

ss

至 设置 计时 电流 那 defines 这 打开 de-

铺设 的 两者都有 高侧 驱动程序. 这 低侧 驱动程序 关闭 与 否 可调 延迟, 所以 这 hdel 电阻 瓜尔胶-

antees 否 射穿 由 拖延 这 打开 的 这 高侧 驱动程序. hdel 参考 电压 是

大约 5.1v.

9 LDEL 低侧 打开 延迟. 连接 电阻 从 这个 管脚 至 v

ss

至 设置 计时 电流 那 defines 这 打开 延迟

的 两者都有 低侧 驱动程序. 这 高侧 驱动程序 关闭 与 否 可调 延迟, 所以 这 ldel 电阻 保证

否 射穿 由 拖延 这 打开 的 这 低侧 驱动程序. ldel 参考 电压 是 大约 5.1v.

10 AHB 一个 高侧 引导程序 供应. 外部 引导程序 二极管 和 电容器 是 必填项. 连接 阴极 的 引导-

绑带 二极管 和 正 侧面 的 引导程序 电容器 至 这个 管脚. 内部 费用 泵 供应品 30

µ

一个 出点 的 这个

管脚 至 维护 引导程序 供应. 内部 电路 卡箍 这 引导程序 供应 至 大约 12.8v.

11 AHO 一个 高侧 输出. 连接 至 闸门 的 一个 高侧 电源 场效应晶体管.

12 AHS 一个 高侧 来源 连接. 连接 至 来源 的 一个 高侧 电源 场效应晶体管. 连接 负 侧面 的

引导程序 电容器 至 这个 管脚.

13 ALO 一个 低侧 输出. 连接 至 闸门 的 一个 低侧 电源 场效应晶体管.

14 als 一个 低侧 来源 连接. 连接 至 来源 的 一个 低侧 电源 场效应晶体管.

15 v

抄送

正 供应 至 闸门 驱动程序. 必须 是 相同 潜力 作为 v

dd

(管脚 16). 连接 至 阳极 的 两个 引导程序

二极管

.

16 v

dd

正 供应 至 下部 闸门 驱动程序. 必须 是 相同 潜力 作为 v

抄送

(管脚 15). 解耦合 这个 管脚 至 v

ss

(管脚 4).

17 BLS b 低侧 来源 连接. 连接 至 来源 的 b 低侧 电源 场效应晶体管.

18 blo b 低侧 输出. 连接 至 闸门 的 b 低侧 电源 场效应晶体管.

19 BHS b 高侧 来源 连接. 连接 至 来源 的 b 高侧 电源 场效应晶体管. 连接 负 侧面 的

引导程序 电容器 至 这个 管脚.

20 BHO b 高侧 输出. 连接 至 闸门 的 b 高侧 电源 场效应晶体管.