9-24

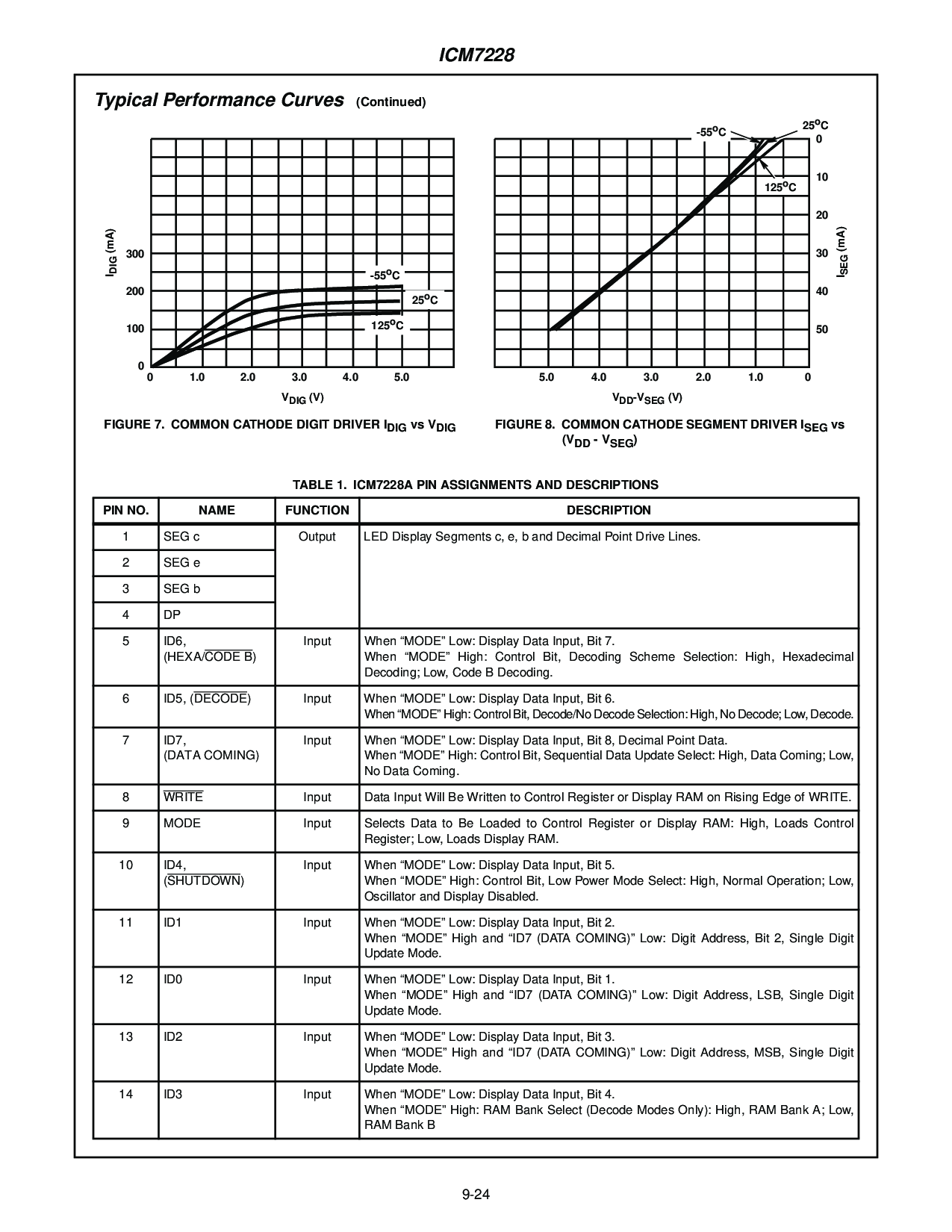

图示 7. 一般 cathode 数字 驱动器 i

DIG

vs v

DIG

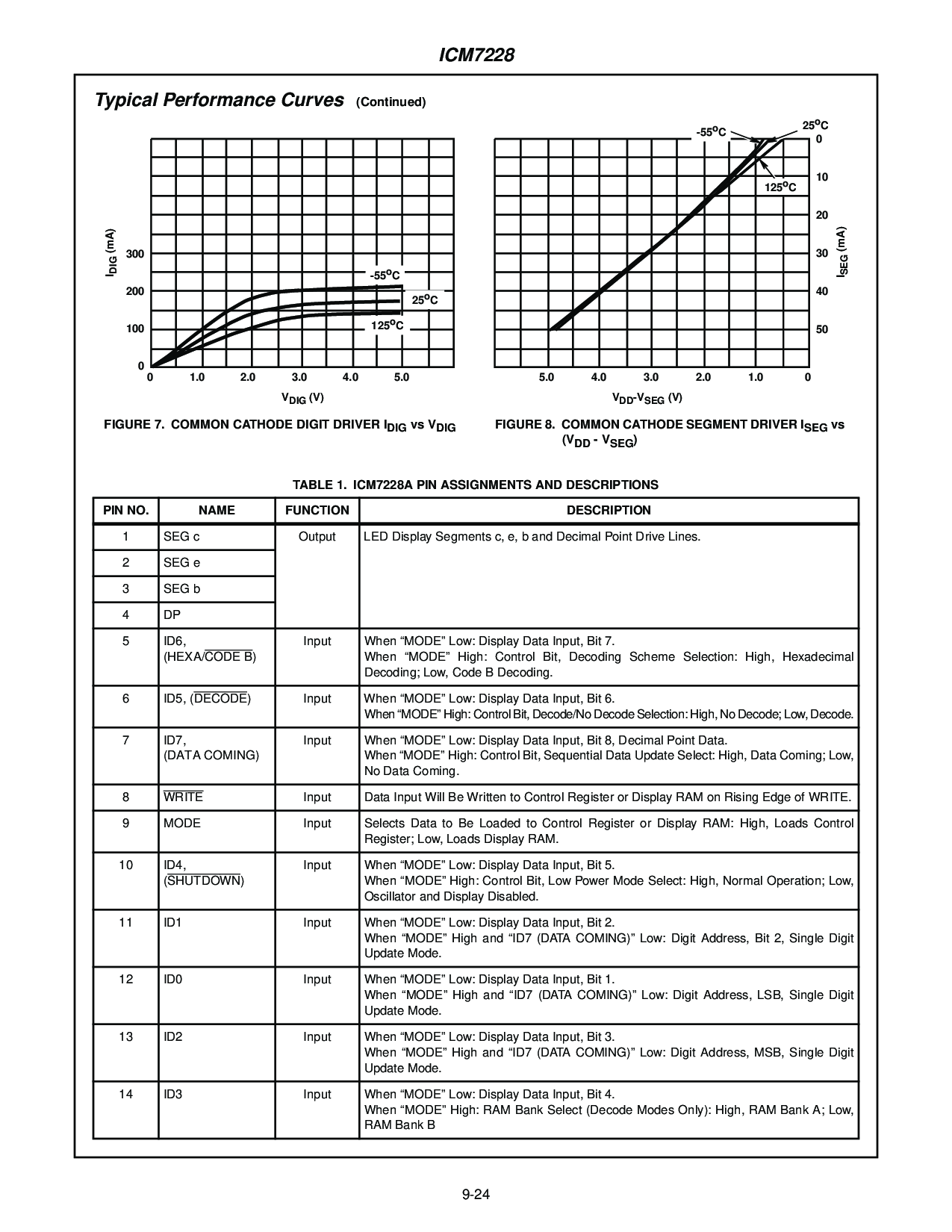

图示 8. 一般 cathode 段 驱动器 i

SEG

vs

(v

DD

- v

SEG

)

表格 1. icm7228a 管脚 assignments 和 描述

管脚 非. 名字 函数 描述

1 seg c 输出 led 显示 部分 c, e, b 和 decimal 要点 驱动 线条.

2 seg e

3 seg b

4DP

5 id6,

(hexa/代号 b)

输入 当 “mode” 低: 显示 数据 输入, 位 7.

当 “mode” 高: 控制 位, 解码 scheme 选择: 高, hexadecimal

解码; 低, 代号 b 解码.

6 id5, (decode) 输入 当 “mode” 低: 显示 数据 输入, 位 6.

当 “mode” 高: 控制 位, decode/非 decode 选择: high, 非 decode; low, decode.

7 id7,

(数据 coming)

输入 当 “mode” 低: 显示 数据 输入, 位 8, decimal 要点 数据.

当 “mode” 高: 控制 位, sequential 数据 更新 选择: 高, 数据 coming; low,

非 数据 coming.

8 写 输入 数据 输入 将 是 写 至 控制 寄存器 或者 显示 内存 在 rising 边缘 的 写.

9 模式 输入 选择 数据 至 是 承载 至 控制 寄存器 或者 显示 内存: 高, 负载 控制

寄存器; 低, 负载 显示 内存.

10 id4,

(关闭)

输入 当 “mode” 低: 显示 数据 输入, 位 5.

当 “mode” 高: 控制 位, 低 电源 模式 选择: 高, 正常的 operation; low,

振荡器 和 显示 无能.

11 ID1 输入 当 “mode” 低: 显示 数据 输入, 位 2.

当 “mode” 高 和 “id7 (数据 coming)” 低: 数字 地址, 位 2, 单独的 数字

更新 模式.

12 ID0 输入 当 “mode” 低: 显示 数据 输入, 位 1.

当 “mode” 高 和 “id7 (数据 coming)” 低: 数字 地址, lsb, 单独的 数字

更新 模式.

13 ID2 输入 当 “mode” 低: 显示 数据 输入, 位 3.

当 “mode” 高 和 “id7 (数据 coming)” 低: 数字 地址, msb, 单独的 数字

更新 模式.

14 ID3 输入 当 “mode” 低: 显示 数据 输入, 位 4.

当 “mode” 高: 内存 bank 选择 (decode 模式 仅有的): 高, 内存 bank a; low,

内存 bank b

典型 效能 曲线

(持续)

V

DIG

(v)

I

DIG

(毫安)

300

200

100

0

0 1.0 2.0 3.0 4.0 5.0

-55

o

C

25

o

C

125

o

C

V

DD

-v

SEG

(v)

0

10

20

30

40

50

01.02.03.04.05.0

I

SEG

(毫安)

-55

o

C

25

o

C

125

o

C

ICM7228