半导体 组件 industries, llc, 2004

october, 2004 − rev. 13

1

发行 顺序 号码:

mc10ep195/d

mc10ep195, mc100ep195

3.3v ecl 可编程序的

延迟 碎片

这 mc10/100ep195 是 一个 可编程序的 延迟 碎片 (pdc)

设计 primarily 为 时钟 deskewing 和 定时 调整. 它

提供 能变的 延迟 的 一个 差别的 necl/pecl 输入 转变.

这 延迟 部分 组成 的 一个 可编程序的 矩阵变换 的 门 和

multiplexers 作 显示 在 这 逻辑 图解, 图示 2. 这 延迟

increment 的 这 ep195 有 一个 digitally 可选择的 决议 的 关于

10 ps 和 一个 网 范围 的 向上 至 10.2 ns. 这 必需的 延迟 是 选择 用

这 10 数据 选择 输入 d[9:0] 值 和 控制 用 这 len

(管脚 10). 一个 低 水平的 在 len 准许 一个 transparent 加载 模式 的

real 时间 延迟 值 用 d[9:0]. 一个 低 至 高 转变 在 len

将 锁 和 支撑 电流 值 呈现 相反 任何 subsequent

改变 在 d[10:0]. 这 近似的 延迟 值 为 varying tap

号码 correlating 至 d0 (lsb) 通过 d9 (msb) 是 显示 在

表格 6 和 图示 3.

因为 这 ep195 是 设计 使用 一个 chain 的 multiplexers 它 有 一个

fixed 最小 延迟 的 2.2 ns. 一个 额外的 管脚 d10 是 提供 为

controlling 管脚 14 和 15, cascade 和 cascade

, 也 latched

用 len, 在 cascading 多样的 pdcs 为 增加 可编程序的

范围. 这 cascade 逻辑 准许 全部 控制 的 多样的 pdcs.

切换 设备 从 所有 “1” states 在 d[0:9] 和 setmax 低

至 所有 “0” states 在 d[0:9] 和 setmax 高 将 增加 这

延迟 相等的 至 “d0”, 这 最小 increment.

选择 输入 管脚 d[10:0] 将 是 门槛 控制 用

结合体 的 interconnects 在 v

EF

(管脚 7) 和 v

CF

(管脚 8)

为 lvcmos, ecl, 或者 lvttl 水平的 信号. 为 lvcmos 输入

水平, leave v

CF

和 v

EF

打开. 为 ecl 运作, 短的 v

CF

和

V

EF

(管脚 7 和 8). 为 lvttl 水平的 运作, 连接 一个 1.5 v

供应 涉及 至 v

CF

和 leave 打开 v

EF

管脚. 这 1.5 v 涉及

电压 至 v

CF

管脚 能 是 accomplished 用 放置 一个 2.2 k

电阻

在 v

CF

和 v

EE

为 一个 3.3 v 电源 供应.

这 v

BB

管脚, 一个 内部 发生 电压 供应, 是 有 至

这个 设备 仅有的. 为 单独的-结束 输入 情况, 这 unused

差别的输入 是 连接 至 v

BB

作 一个 切换 涉及 电压.

V

BB

将 也 rebias 交流 结合 输入. 当 使用, 分离 v

BB

和 v

CC

通过 一个 0.01

f 电容 和 限制 电流 sourcing 或者 sinking

至 0.5 毫安. 当 不 使用, v

BB

应当 是 left 打开.

这 100 序列 包含 温度 补偿.

•

最大 输入 时钟 频率 >1.2 ghz 典型

•

可编程序的 范围: 0 ns 至 10 ns

•

延迟 范围: 2.2 ns 至 12.2 ns

•

10 ps increments

•

pecl 模式 运行 范围:

V

CC

= 3.0 v 至 3.6 v 和 v

EE

= 0 v

•

necl 模式 运行 范围:

V

CC

= 0 v 和 v

EE

= −3.0 v 至 −3.6 v

•

打开 输入 default 状态

•

安全 clamp 在 输入

•

一个 逻辑 高 在 这 en 管脚 将 强迫 q 至 逻辑

低

•

d[10:0] 能 接受 也 ecl, lvcmos, 或者 lvttl

输入

•

V

BB

输出 涉及 电压

32

1

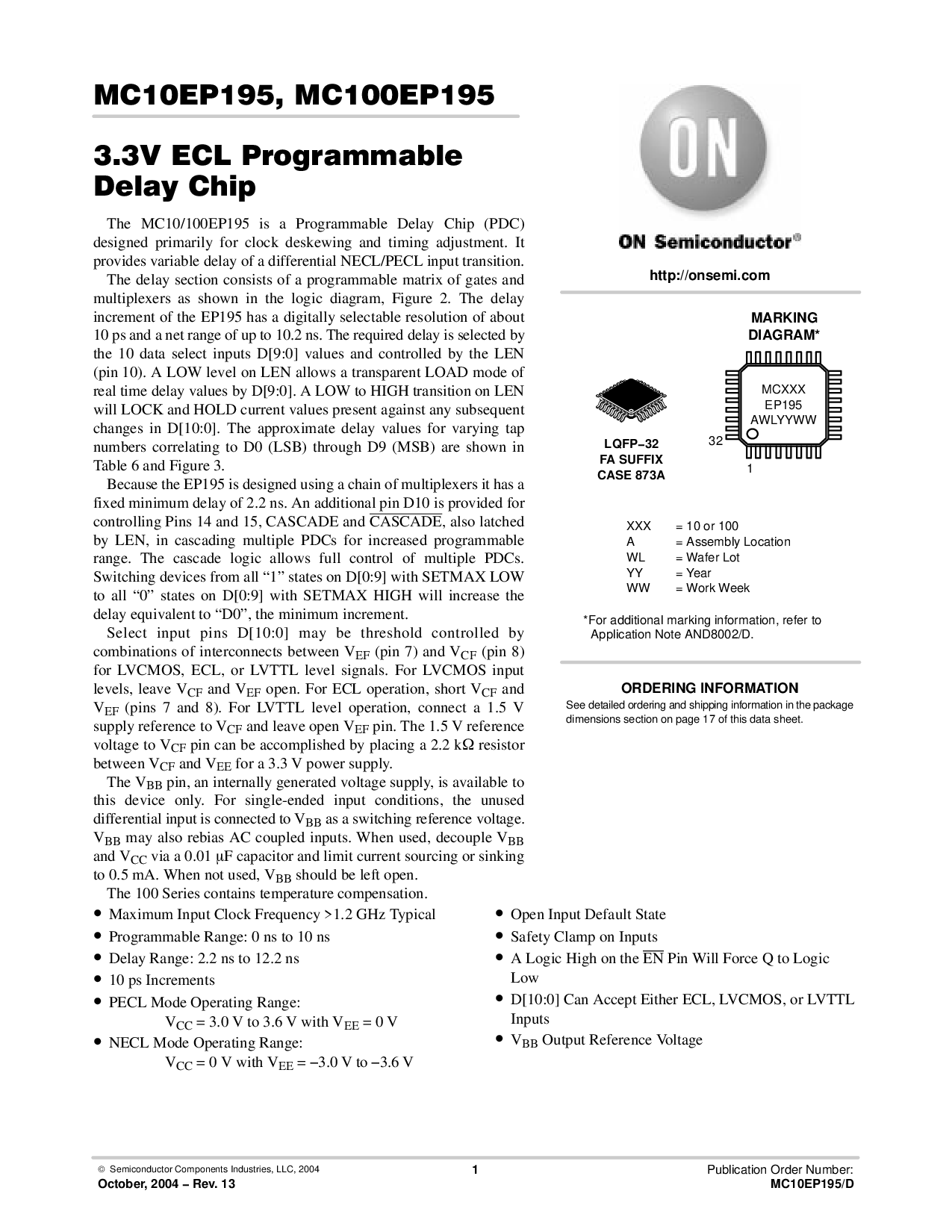

LQFP−32

fa 后缀

情况 873a

标记

DIAGRAM*

XXX = 10 或者 100

一个 = 组装 location

WL = 薄脆饼 lot

YY = 年

WW = 工作 week

*for 额外的 标记 信息, 谈及 至

应用 便条 and8002/d.

MCXXX

EP195

AWLYYWW

http://onsemi.com

看 详细地 订货 和 shipping 信息 在 这 包装

维度 部分 在 页 17 的 这个 数据 薄板.

订货 信息