为 communications 设备

Overview

这 mn6155 是 一个 cmos lsi 为 一个 阶段-锁 循环

(pll) 频率 synthesizer 和 串行 数据 参数

输入.

它 组成 的 一个 二-系数 预分频器, 能变的

频率 分隔物, 阶段 比较器, 和 承担 打气.

它 提供 高-速 运作 在 一个 低 电源 供应

电压 (1.0 至 1.4 v) 和 低 电源 消耗量 (1.65

mw 为 v

DD

=1.1 v, f

在

= r

在

=90 mhz).

其它 特性 包含 intermittent 运作 用 这

电源 保存 (ps) 控制 信号 和 高-速 拉-在 那

迅速 corrects 这 阶段 differences occurring 在 这 开始

的 运作.

它 也 提供 二 choices 为 这 涉及 信号: 自-

excited 运作 使用 这 建造-在 反相器 放大器 或者

使用 的 一个 外部, separately excited 振荡器.

特性

低 电源 供应 电压: V

DD

=1.0 至 1.4v

低 电源 消耗量: 1.65mw(v

DD

=1.10v,

F

在

=90mhz, r

在

=90mhz)

高-速 运作: f

在

=90mhz, r

在

=90MHz

(v

DD

=1.1v)

频率 dividing ratios 在 涉及 频率

dividing 平台

6 至 131,070 为 rsl 在 "h" 水平的

(甚至 号码 设置 是 有)

272 至 131,071 为 rsl 在 "l" 水平的

频率 dividing ratios 为 比较器 平台: 272

至 262,143

电源 供应 管脚 为 建造-在 承担 打气

V

CP

=2.5 至 3.2v

输出 监控 管脚 为 两个都 比较器 和 涉及

频率 dividing stages

MN6155

pll lsi 和 建造-在 预分频器

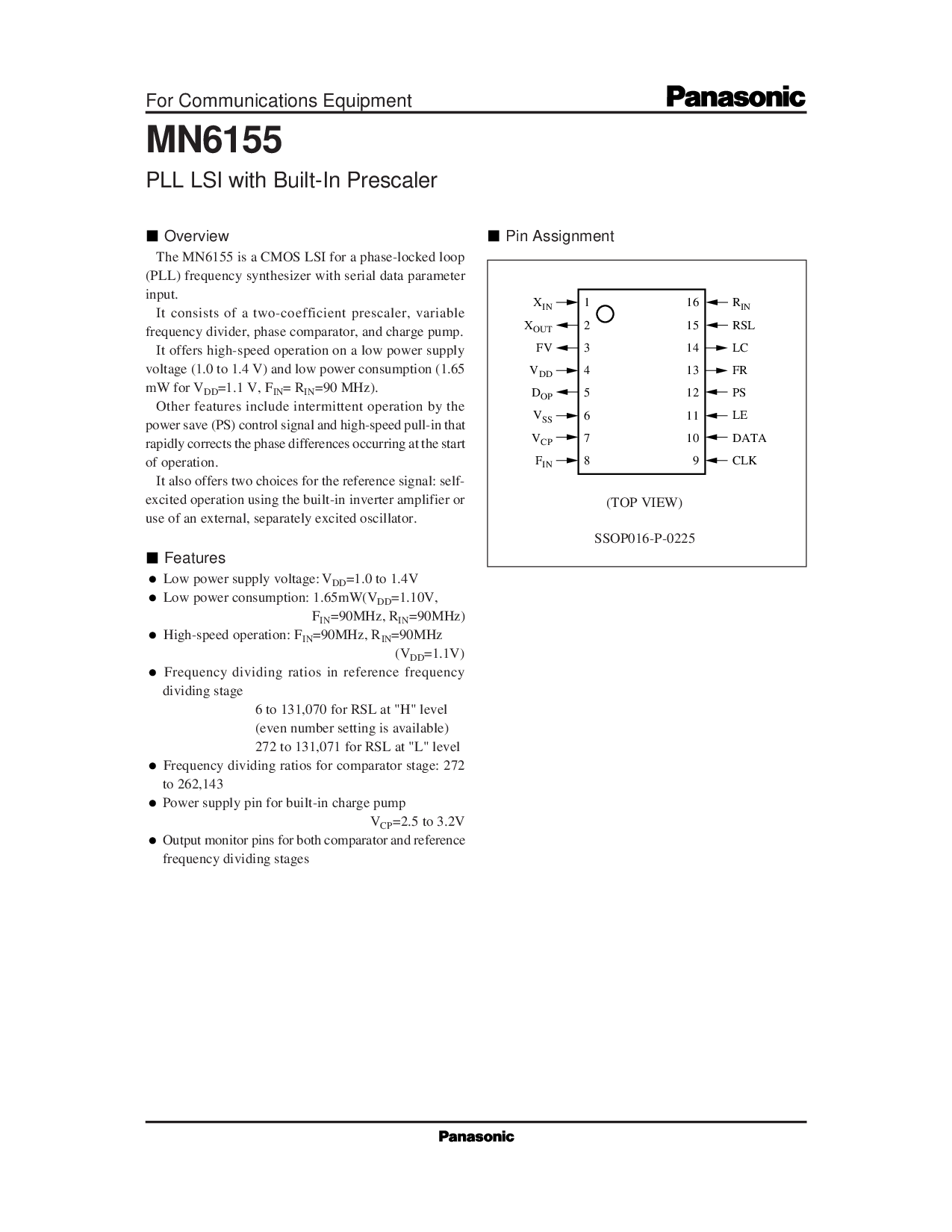

管脚 分派

ssop016-p-0225

(顶 视图)

X

在

X

输出

FV

V

DD

D

运算

V

SS

V

CP

F

在

R

在

RSL

LC

FR

PS

LE

数据

CLK

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9