CMOS

MT9085

2-127

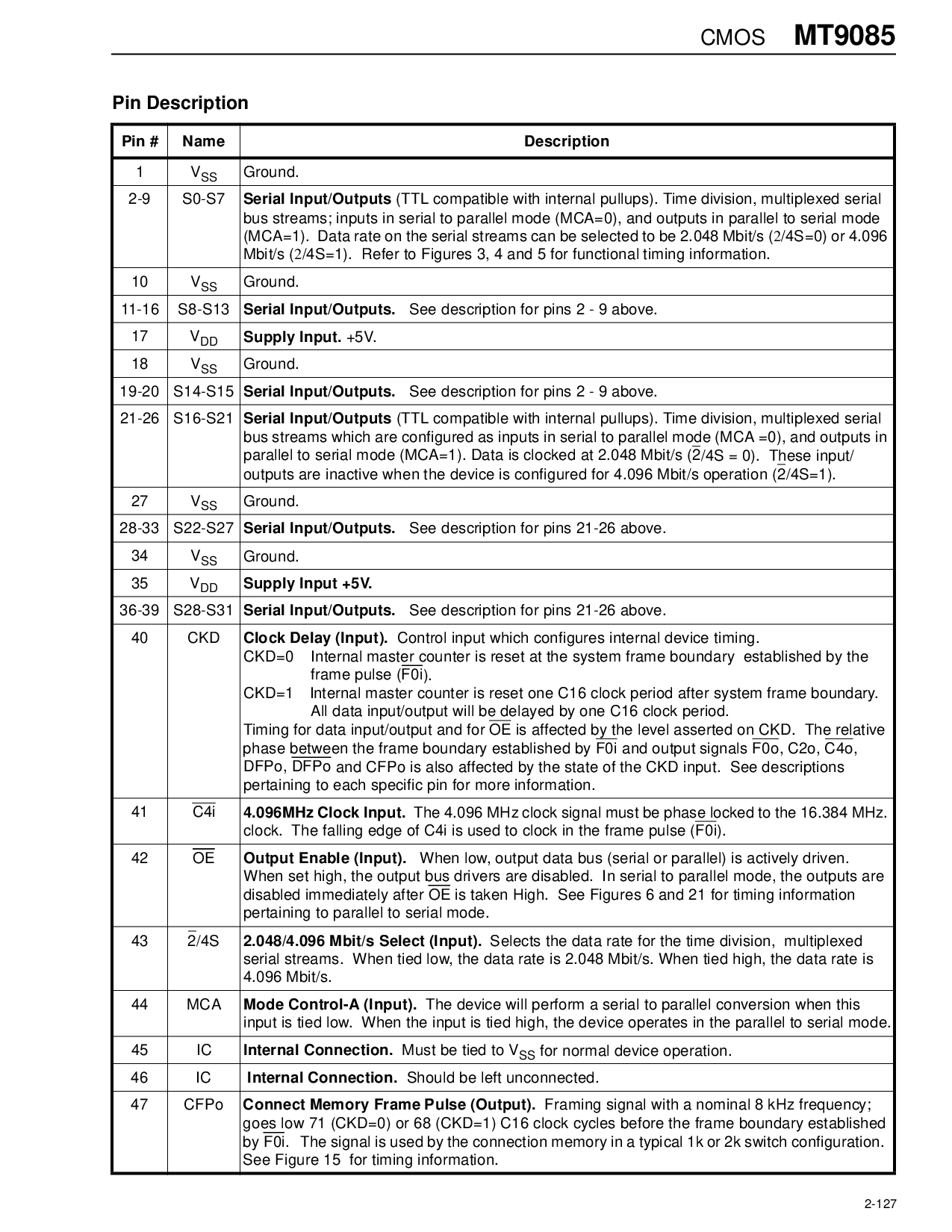

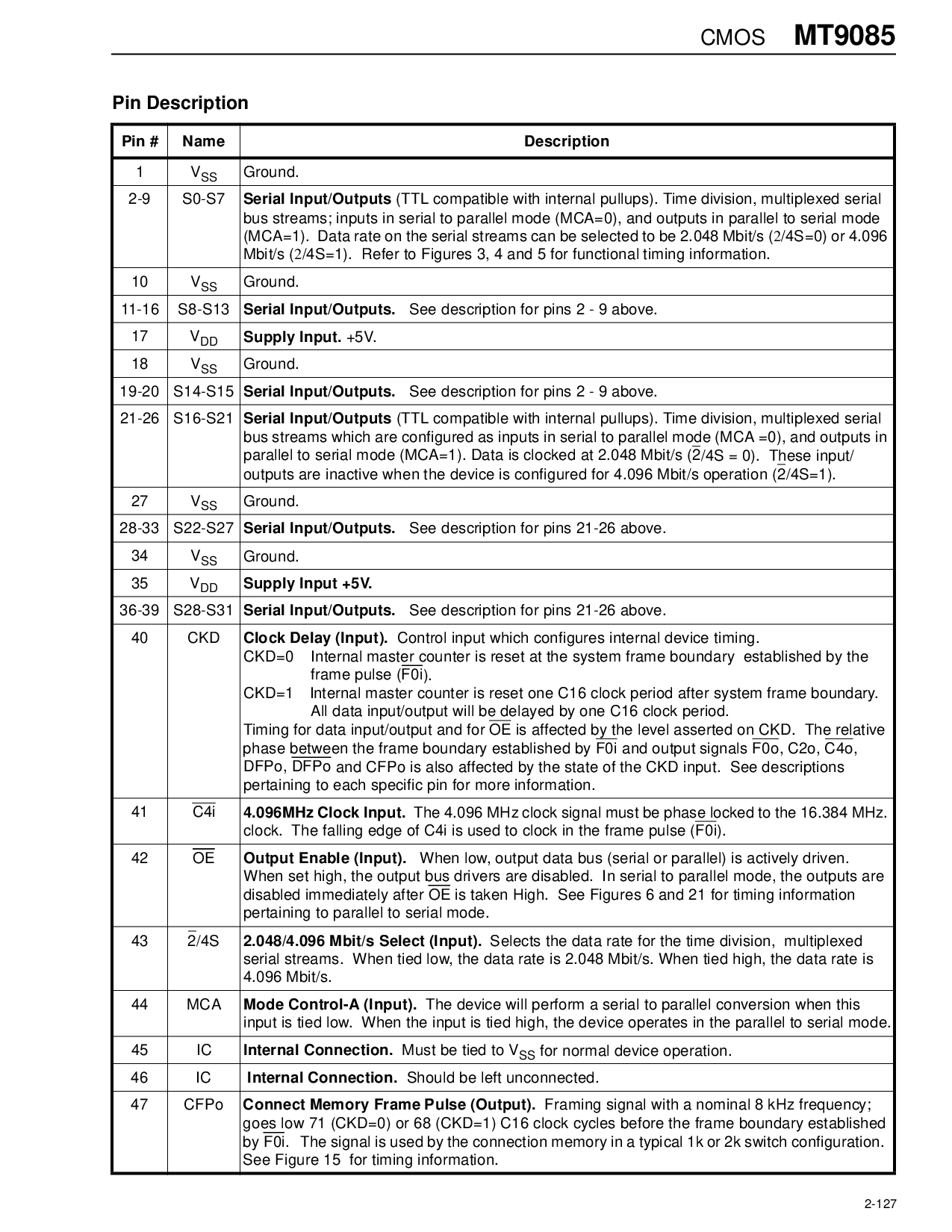

管脚 描述

管脚 # 名字 描述

1V

SS

地面.

2-9 s0-s7

串行 输入/输出

(ttl 兼容 和 内部的 pullups). 时间 分隔, 多路复用 串行

总线 streams; 输入 在 串行 至 并行的 模式 (mca=0), 和 输出 在 并行的 至 串行 模式

(mca=1). 数据 比率 在 这 串行 streams 能 是 选择 至 是 2.048 mbit/s (

2

/4s=0) 或者 4.096

mbit/s (

2

/4s=1). 谈及 至 计算数量 3, 4 和 5 为 函数的 定时 信息.

10 V

SS

地面.

11-16 s8-s13

串行 输入/输出.

看 描述 为 管脚 2 - 9 在之上.

17 V

DD

供应 输入.

+5v.

18 V

SS

地面.

19-20 s14-s15

串行 输入/输出.

看 描述 为 管脚 2 - 9 在之上.

21-26 s16-s21

串行 输入/输出

(ttl 兼容 和 内部的 pullups). 时间 分隔, 多路复用 串行

总线 streams 这个 是 配置 作 输入 在 串行 至 并行的 模式 (mca =0), 和 输出 在

并行的 至 串行 模式 (mca=1). 数据 是 clocked 在 2.048 mbit/s (2

/4s = 0). 这些 输入/

输出 是 inactive 当 这 设备 是 配置 为 4.096 mbit/s 运作 (2

/4s=1).

27 V

SS

地面.

28-33 s22-s27

串行 输入/输出.

看 描述 为 管脚 21-26 在之上.

34 V

SS

地面.

35 V

DD

供应 输入 +5v.

36-39 s28-s31

串行 输入/输出.

看 描述 为 管脚 21-26 在之上.

40 CKD

时钟 延迟 (输入).

控制 输入 这个 configures 内部的 设备 定时.

CKD=0 内部的 主控 计数器 是 重置 在 这 系统 框架 boundary established 用 这

框架 脉冲波 (f0i

).

CKD=1 内部的 主控 计数器 是 重置 一个 c16 时钟 时期 之后 系统 框架 boundary.

所有 数据 输入/输出 将 是 delayed 用 一个 c16 时钟 时期.

定时 为 数据 输入/输出 和 为 oe

是 影响 用 这 水平的 asserted 在 ckd. 这 相关的

阶段 在 这 框架 boundary established 用 f0i

和 输出 信号 f0o, c2o, c4o,

dfpo, dfpo

和 cfpo 是 也 影响 用 这 状态 的 这 ckd 输入. 看 描述

pertaining 至 各自 明确的 管脚 为 更多 信息.

41 C4i

4.096mhz 时钟 输入.

这 4.096 mhz 时钟 信号 必须 是 阶段 锁 至 这 16.384 mhz.

时钟. 这 下落 边缘 的 c4i 是 使用 至 时钟 在 这 框架 脉冲波 (f0i

).

42 OE

输出 使能 (输入).

当 低, 输出 数据 总线 (串行 或者 并行的) 是 actively 驱动.

当 设置 高, 这 输出 总线 驱动器 是 无能. 在 串行 至 并行的 模式, 这 输出 是

无能 立即 之后 oe

是 带去 高. 看 计算数量 6 和 21 为 定时 信息

pertaining 至 并行的 至 串行 模式.

43 2/4s

2.048/4.096 mbit/s 选择 (输入).

选择 这 数据 比率 为 这 时间 分隔, 多路复用

串行 streams. 当 系 低, 这 数据 比率 是 2.048 mbit/s. 当 系 high, 这 数据 比率 是

4.096 mbit/s.

44 MCA

模式 控制-一个 (输入).

这 设备 将 执行 一个 串行 至 并行的 转换 当 这个

输入 是 系 低. 当 这 输入 是 系 高, 这 设备 运作 在 这 并行的 至 串行 模式.

45 IC

内部的 连接.

必须 是 系 至 v

SS

为 正常的 设备 运作.

46 IC

内部的 连接.

应当 是 left unconnected.

47 CFPo

连接 记忆 框架 脉冲波 (输出).

framing 信号 和 一个 名义上的 8 khz 频率;

变得 低 71 (ckd=0) 或者 68 (ckd=1) c16 时钟 循环 在之前 这 框架 boundary established

用 f0i

. 这 信号 是 使用 用 这 连接 记忆 在 一个 典型 1k 或者 2k 转变 配置.

看 图示 15 为 定时 信息.