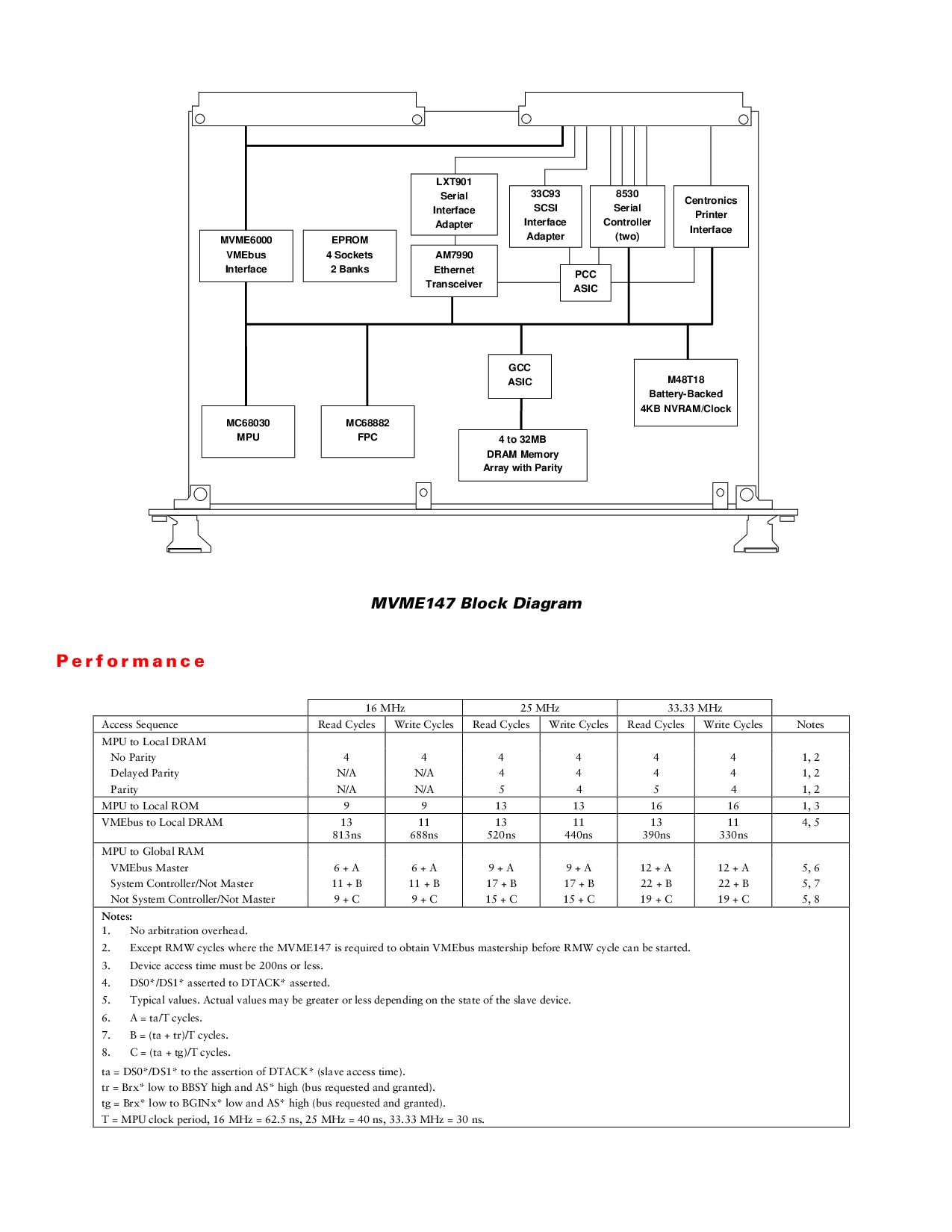

MVME6000

VMEbus

接口

非易失存储器

4 插座

2 banks

MC68030

MPU

GCC

ASIC

4 至 32mb

dram 记忆

排列 和 parity

LXT901

串行

接口

Adapter

Centronics

Printer

接口

AM7990

Ethernet

Transceiver

MC68882

FPC

33C93

SCSI

接口

Adapter

8530

串行

控制

(二)

PCC

ASIC

M48T18

电池-backed

4kb nvram/时钟

mvme147 块 图解

效能

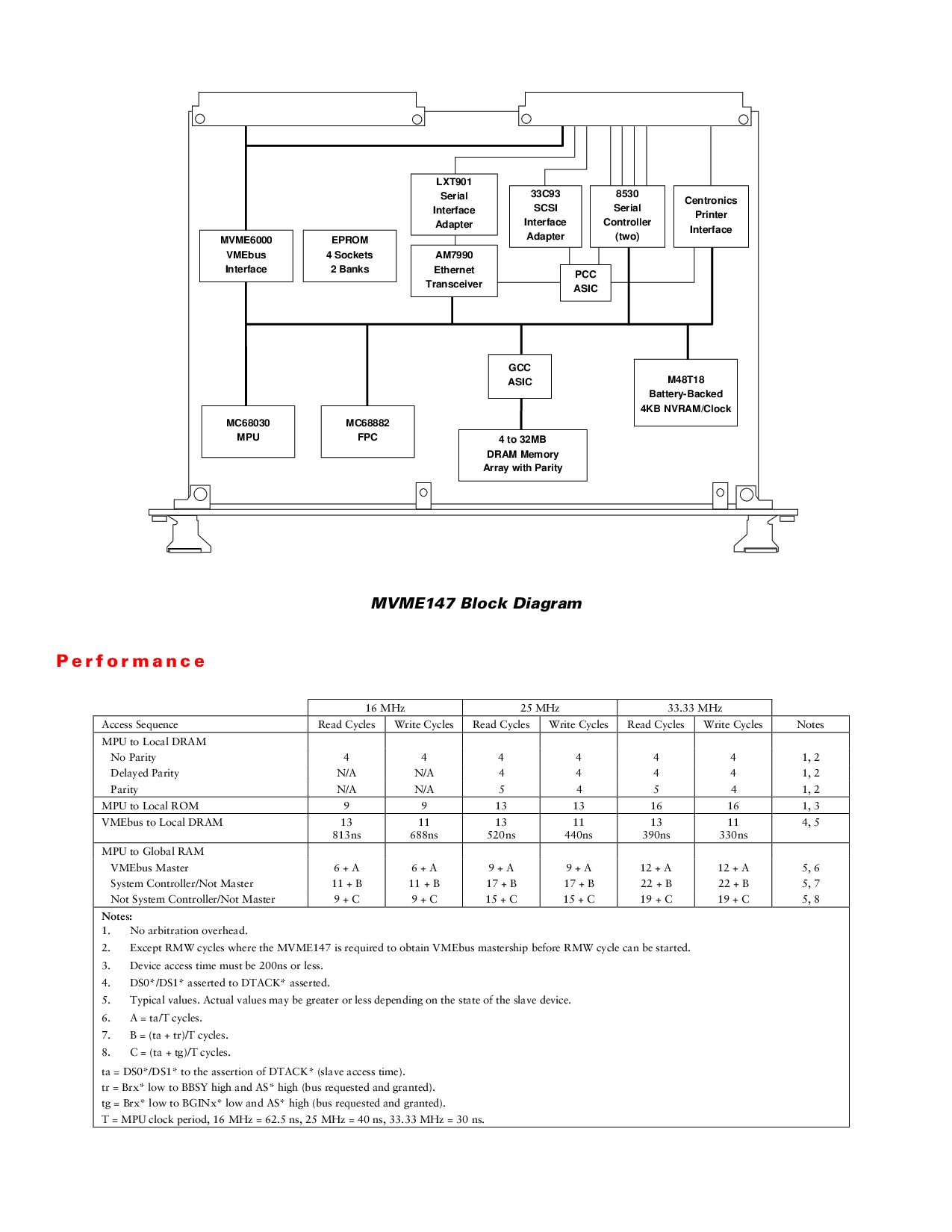

16 mhz 25 mhz 33.33 mhz

进入 sequence 读 循环 写 循环 读 循环 写 循环 读 循环 写 循环 注释

mpu 至 local dram

非 parity 4444441, 2

delayed parity n/一个 n/一个 4 4 4 4 1, 2

Parity n/一个 n/一个 5 4 5 4 1, 2

mpu 至 local 只读存储器 9 9 13 13 16 16 1, 3

vmebus 至 local dram 13

813ns

11

688ns

13

520ns

11

440ns

13

390ns

11

330ns

4, 5

mpu 至 global 内存

vmebus 主控 6 + 一个 6 + 一个 9 + 一个 9 + 一个 12 + 一个 12 + 一个 5, 6

系统 控制/不 主控 11 + b 11 + b 17 + b 17 + b 22 + b 22 + b 5, 7

不 系统 控制/不 主控 9 + c 9 + c 15 + c 15 + c 19 + c 19 + c 5, 8

注释:

1.

非 arbitration overhead.

2.

除了 rmw 循环 在哪里 这 mvme147 是 必需的 至 获得 vmebus mastership 在之前 rmw 循环 能 是 started.

3.

设备 进入 时间 必须 是 200ns 或者 较少.

4.

ds0*/ds1* asserted 至 dtack* asserted.

5.

典型 值. 真实的 值 将 是 更好 或者 较少 取决于 在 这 状态 的 这 从动装置 设备.

6.

一个 = ta/t 循环.

7.

b = (ta + tr)/t 循环.

8.

c = (ta + tg)/t 循环.

ta = ds0*/ds1* 至 这 assertion 的 dtack* (从动装置 进入 时间).

tr = brx* 低 至 bbsy 高 和 as* 高 (总线 要求 和 准予).

tg = brx* 低 至 bginx* 低 和 as* 高 (总线 要求 和 准予).

t = mpu 时钟 时期, 16 mhz = 62.5 ns, 25 mhz = 40 ns, 33.33 mhz = 30 ns.