10

pga204/205

®

典型 效能 曲线

(内容)

在 t

一个

= +25

°

c, 和 v

S

=

±

15v, 除非 否则 指出.

噪音, 0.1 至 10hz, g = 1

1s/div

0.5

µ

v/div

0.2

µ

v/div

1s/div

输入-涉及 噪音,

0.1 至 10hz, g = 1000

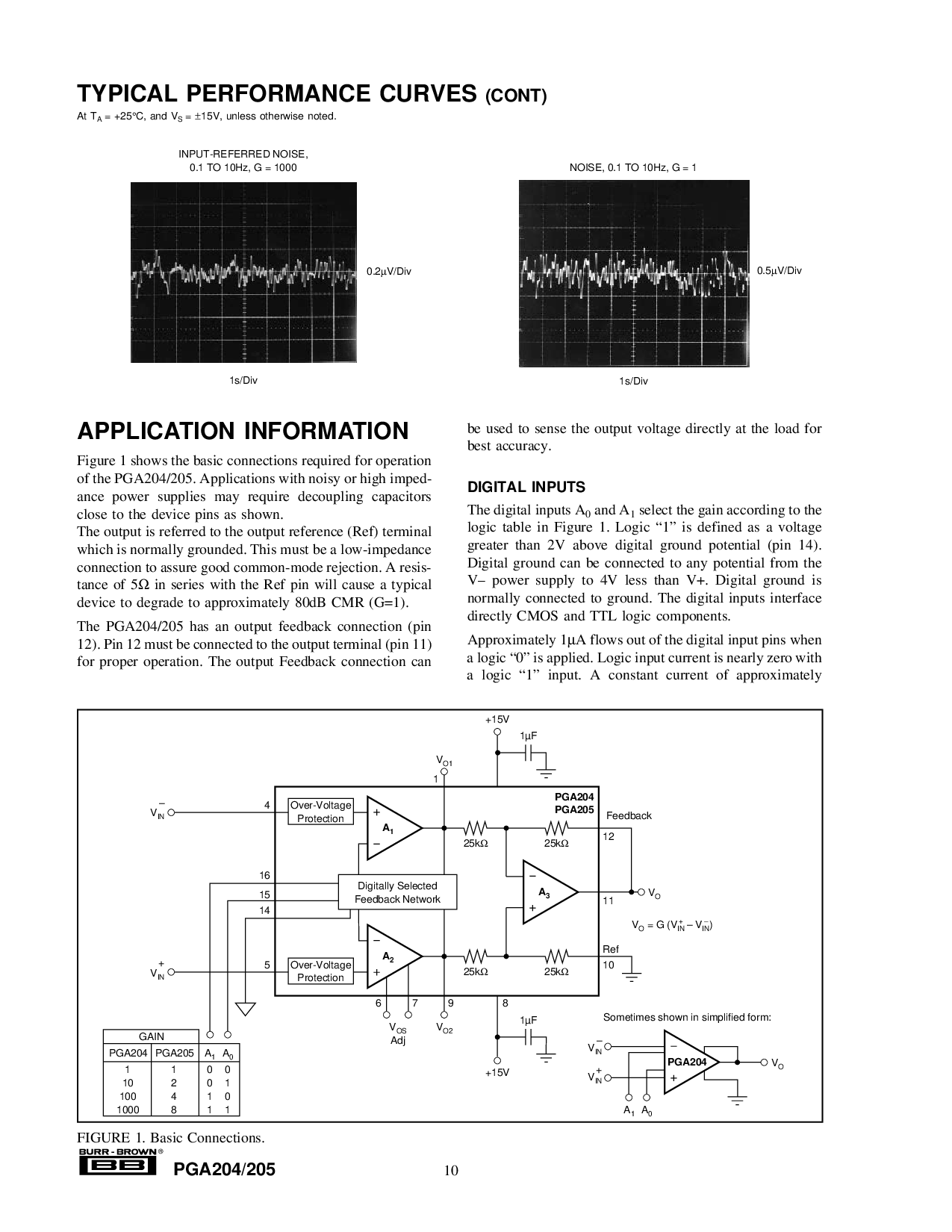

图示 1. 基本 连接.

应用 信息

图示 1显示 这 基本 连接 必需的 为 运作

的 这 pga204/205. 产品 和 嘈杂的 或者 高 imped-

ance 电源 供应 将 需要 解耦 电容

关闭 至 这 设备 管脚 作 显示.

这 输出 是 涉及 至 这 输出 涉及 (ref) 终端

这个 是 正常情况下 grounded. 这个 必须 是 一个 低-阻抗

连接 至 使确信 好的 一般模式 拒绝. 一个 resis-

tance 的 5

Ω

在 序列 和 这 ref 管脚 将 导致 一个 典型

设备 至 降级 至 大概 80db cmr (g=1).

这 pga204/205 有 一个 输出 反馈 连接 (管脚

12). 管脚 12 必须 是 连接 至 这 输出 终端 (管脚 11)

为 恰当的 运作. 这 输出 反馈 连接 能

是 使用 至 sense 这 输出 电压 直接地 在 这 加载 为

最好的 精度.

数字的 输入

这 数字的 输入 一个

0

和 一个

1

选择 这 增益 符合 至 这

逻辑 表格 在 图示 1. 逻辑 “1” 是 定义 作 一个 电压

更好 比 2v 在之上 数字的 地面 潜在的 (管脚 14).

数字的 地面 能 是 连接 至 任何 潜在的 从 这

v– 电源 供应 至 4v 较少 比 v+. 数字的 地面 是

正常情况下 连接 至 地面. 这 数字的 输入 接口

直接地 cmos 和 ttl 逻辑 组件.

大概 1

µ

一个 flows 输出 的 这 数字的 输入 管脚 当

一个 逻辑 “0” 是 应用. 逻辑 输入 电流 是 nearly 零 和

一个 逻辑 “1” 输入. 一个 常量 电流 的 大概

一个

1

一个

2

一个

3

12

11

10

25k

Ω

25k

Ω

25k

Ω

25k

Ω

7

5

14

16

4

V

在

V

在

PGA204

PGA205

V

O

= g (v

在

– v

在

)

V

O

–

+

在-voltage

保护

在-voltage

保护

反馈

digitally selected

反馈 网络

1

V

O1

15

6 9

8

V

O2

V

OS

Adj

+15V

1µF

+15V

1µF

+–

PGA204

V

在

V

在

–

+

V

O

一个

1

一个

0

sometimes 显示 在 simplified 表格:

一个

1

一个

0

PGA205PGA204

增益

0

0

1

1

0

1

0

1

1

2

4

8

1

10

100

1000

Ref