ADS7807

8

SBAS022B

www.德州仪器.com

十六进制 十六进制

二进制的 代号 代号 二进制的 代号 代号

+full-规模 (fs

–

1lsb) 9.999695v 4.999924v 3.999939v 0111 1111 1111 1111 7FFF 1111 1111 1111 1111 FFFF

Midscale 0V 2.5v 2V 0000 0000 0000 0000 0000 1000 0000 0000 0000 8000

一个 lsb 在下 midscale

–

305

µ

V 2.499924v 1.999939v 1111 1111 1111 1111 FFFF 0111 1111 1111 1111 7FFF

–

全部-规模

–

10V 0V 0V 1000 0000 0000 0000 8000 0000 0000 0000 0000 0000

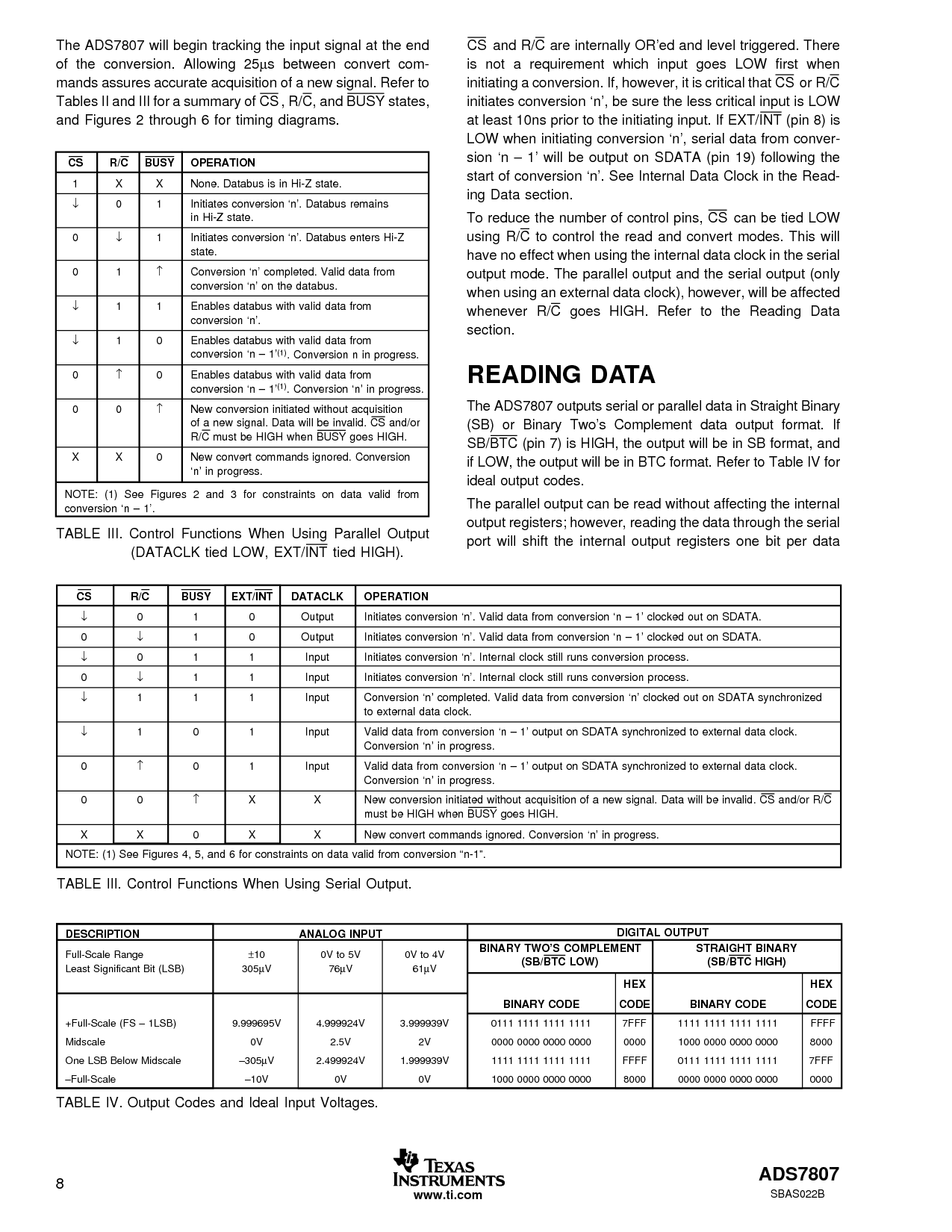

CS r/c BUSY 运作

1 X X 毫无. databus 是 在 hi-z 状态.

↓

0 1 initiates 转换

‘

n

’

. databus 仍然是

在 hi-z 状态.

0

↓

1 initiates 转换

‘

n

’

. databus enters hi-z

状态.

01

↑

转换

‘

n

’

完成. 有效的 数据 从

转换

‘

n

’

在 这 databus.

↓

1 1 使能 databus 和 有效的 数据 从

转换

‘

n

’

.

↓

1 0 使能 databus 和 有效的 数据 从

转换

‘

n

–

1

’

(1)

. 转换 n 在 progress.

0

↑

0 使能 databus 和 有效的 数据 从

转换

‘

n

–

1

’

(1)

. 转换

‘

n

’

在 progress.

00

↑

新 转换 initiated 没有 acquisition

的 一个 新 信号. 数据 将 是 invalid. cs 和/或者

r/c 必须 是 高 当 busy 变得 高.

X X 0 新 转变 commands ignored. 转换

‘

n

’

在 progress.

便条: (1) 看 计算数量 2 和 3 为 constraints 在 数据 有效的 从

转换

‘

n

–

1

’

.

这 ads7807 将 begin 追踪 这 输入 信号 在 这 终止

的 这 转换. 准许 25

µ

s 在 转变 com-

mands assures 精确 acquisition 的 一个 新 信号. 谈及 至

tables ii 和 iii 为 一个 summary 的

CS

,

r/c

, 和

BUSY

states,

和 计算数量 2 通过 6 为 定时 图解.

CS

和

r/c

是 内部 或者

’

ed 和 水平的 triggered. 那里

是 不 一个 必要条件 这个 输入 变得 低 第一 当

初始的 一个 转换. 如果, 不管怎样, 它 是 核心的 那

CS

或者

r/c

initiates 转换

‘

n

’

, 是 确信 这 较少 核心的 输入 是 低

在 least 10ns 较早的 至 这 初始的 输入. 如果

ext/int

(管脚 8) 是

低 当 初始的 转换

‘

n

’

, 串行 数据 从 变换器-

sion

‘

n

–

1

’

将 是 输出 在 sdata (管脚 19) 下列的 这

开始 的 转换

‘

n

’

. 看 内部的 数据 时钟 在 这 读-

ing 数据 部分.

至 减少 这 号码 的 控制 管脚,

CS

能 是 系 低

使用

r/c

至 控制 这 读 和 转变 模式. 这个 将

有 非 效应 当 使用 这 内部的 数据 时钟 在 这 串行

输出 模式. 这 并行的 输出 和 这 串行 输出 (仅有的

当 使用 一个 外部 数据 时钟), 不管怎样, 将 是 影响

whenever

r/c

变得 高. 谈及 至 这 读 数据

部分.

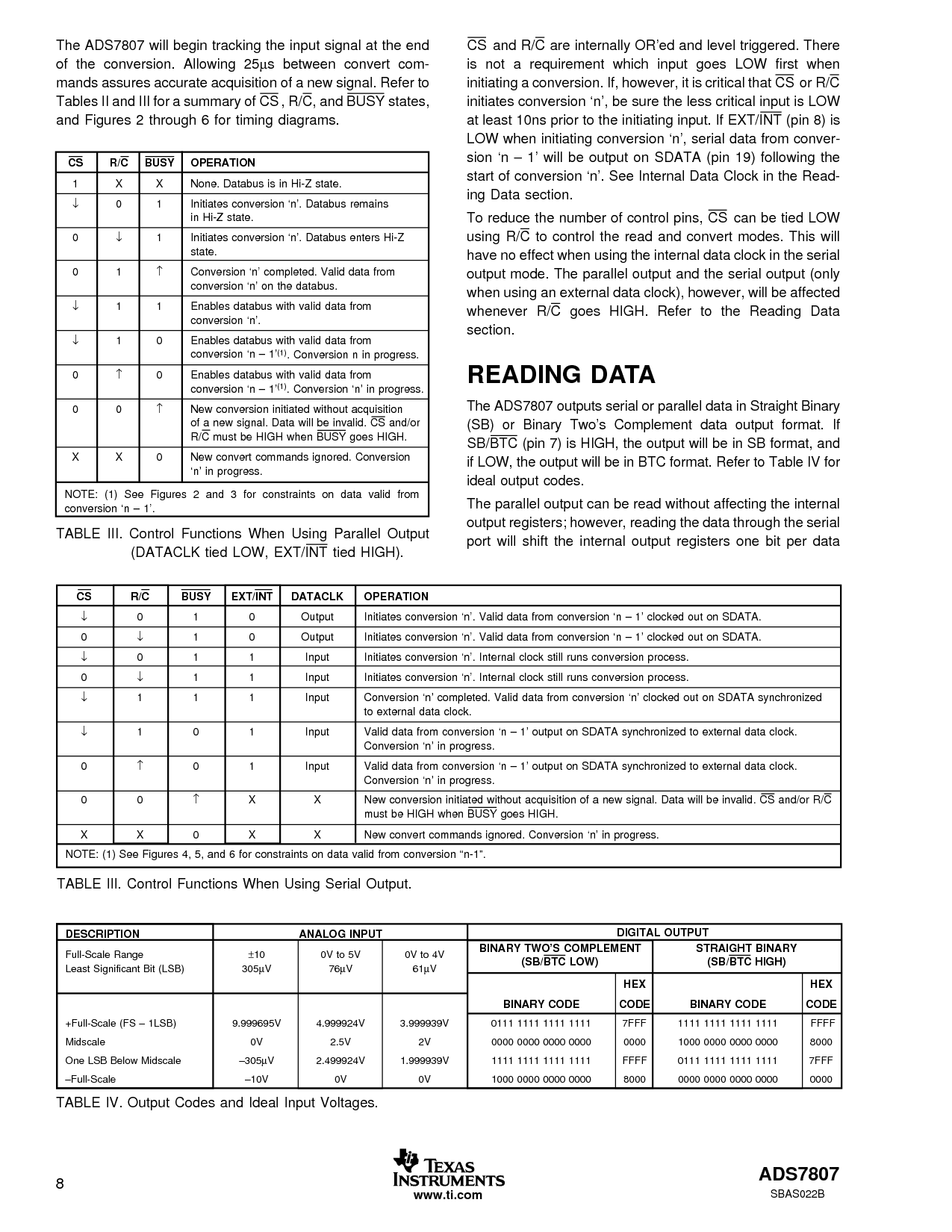

读 数据

这 ads7807 输出 串行 或者 并行的 数据 在 笔直地 二进制的

(sb) 或者 二进制的 二

’

s complement 数据 输出 format. 如果

sb/btc

(管脚 7) 是 高, 这 输出 将 是 在 sb format, 和

如果 低, 这 输出 将 是 在 btc format. 谈及 至 表格 iv 为

完美的 输出 代号.

这 并行的 输出 能 是 读 没有 影响 这 内部的

输出 寄存器; 不管怎样, 读 这 数据 通过 这 串行

端口 将 变换 这 内部的 输出 寄存器 一个 位 每 数据

CS r/c BUSY ext/int DATACLK 运作

↓

0 1 0 输出 initiates 转换

‘

n

’

. 有效的 数据 从 转换

‘

n

–

1

’

clocked 输出 在 sdata.

0

↓

1 0 输出 initiates 转换

‘

n

’

. 有效的 数据 从 转换

‘

n

–

1

’

clocked 输出 在 sdata.

↓

0 1 1 输入 initiates 转换

‘

n

’

. 内部的 时钟 安静的 runs 转换 处理.

0

↓

1 1 输入 initiates 转换

‘

n

’

. 内部的 时钟 安静的 runs 转换 处理.

↓

1 1 1 输入 转换

‘

n

’

完成. 有效的 数据 从 转换

‘

n

’

clocked 输出 在 sdata 同步

至 外部 数据 时钟.

↓

1 0 1 输入 有效的 数据 从 转换

‘

n

–

1

’

输出 在 sdata 同步 至 外部 数据 时钟.

转换

‘

n

’

在 progress.

0

↑

0 1 输入 有效的 数据 从 转换

‘

n

–

1

’

输出 在 sdata 同步 至 外部 数据 时钟.

转换

‘

n

’

在 progress.

00

↑

X X 新 转换 initiated 没有 acquisition 的 一个 新 信号. 数据 将 是 invalid. cs 和/或者 r/c

必须 是 高 当 busy 变得 高.

X X 0 X X 新 转变 commands ignored. 转换

‘

n

’

在 progress.

便条: (1) 看 计算数量 4, 5, 和 6 为 constraints 在 数据 有效的 从 转换

“

n-1

”

.

表格 iii. 控制 功能 当 使用 串行 输出.

表格 iv. 输出 代号 和 完美的 输入 电压.

表格 iii. 控制 功能 当 使用 并行的 输出

(dataclk 系 低,

ext/int

系 高).

二进制的 二

’

s complement 笔直地 二进制的

(sb/btc 低) (sb/btc 高)

数字的 输出

描述 相似物 输入

全部-规模 范围

±

10 0v 至 5v 0v 至 4v

least 重大的 位 (lsb) 305

µ

V76

µ

V61

µ

V