12

rev. 10-17-00 sp706 +3.0/ +3.3 低 电源 微处理器 电路 © 版权 2000 sipex 公司

ensuring 一个 有效的 重置 输出 向下 至

V

CC

= 0v

当 v

CC

falls 在下 1v, 这 重置 输出 非

变长 sinks 电流, 它 变为 一个 打开 电路.

高-阻抗 cmos 逻辑 输入 能 逐渐变化 至

undetermined 电压 如果 left undriven. 如果 一个 拉-

向下 电阻 是 增加 至 这 重置 管脚, 任何

偏离 承担 或者 泄漏 电流 将 是 shunted

至 地面, 支持 重置 低. 这 电阻

值 是 不 核心的. 它 应当 是 关于 100k

Ω

,

大 足够的 不 至 加载 重置 和 小

足够的 至 拉 重置 至 地面.

monitoring 电压 其它 比 这

无秩序的 直流 输入

监控 电压 其它 比 这 无秩序的 直流

用 连接 一个 电压 分隔物 至 pfi 和

调整 这 比率 appropriately. 如果 必需的,

增加 hysteresis 用 连接 一个 电阻 (和 一个

值 大概 10 时间 这 总 的 这

二 电阻器 在 这 潜在的 分隔物 网络)

在 pfi 和 pfo. 一个 电容 在 pfi

和 地 将 减少 这 电源-失败 电路's

敏锐的 至 高-频率 噪音 在 这

线条 正在 监控. 重置 能 是 使用 至

监控 电压 其它 比 这 +3.3v/+3.0v

V

CC

线条. 连接 pfo 至 mr 至 initiate 一个

重置 脉冲波 当 pfi drops 在下 1.25v.

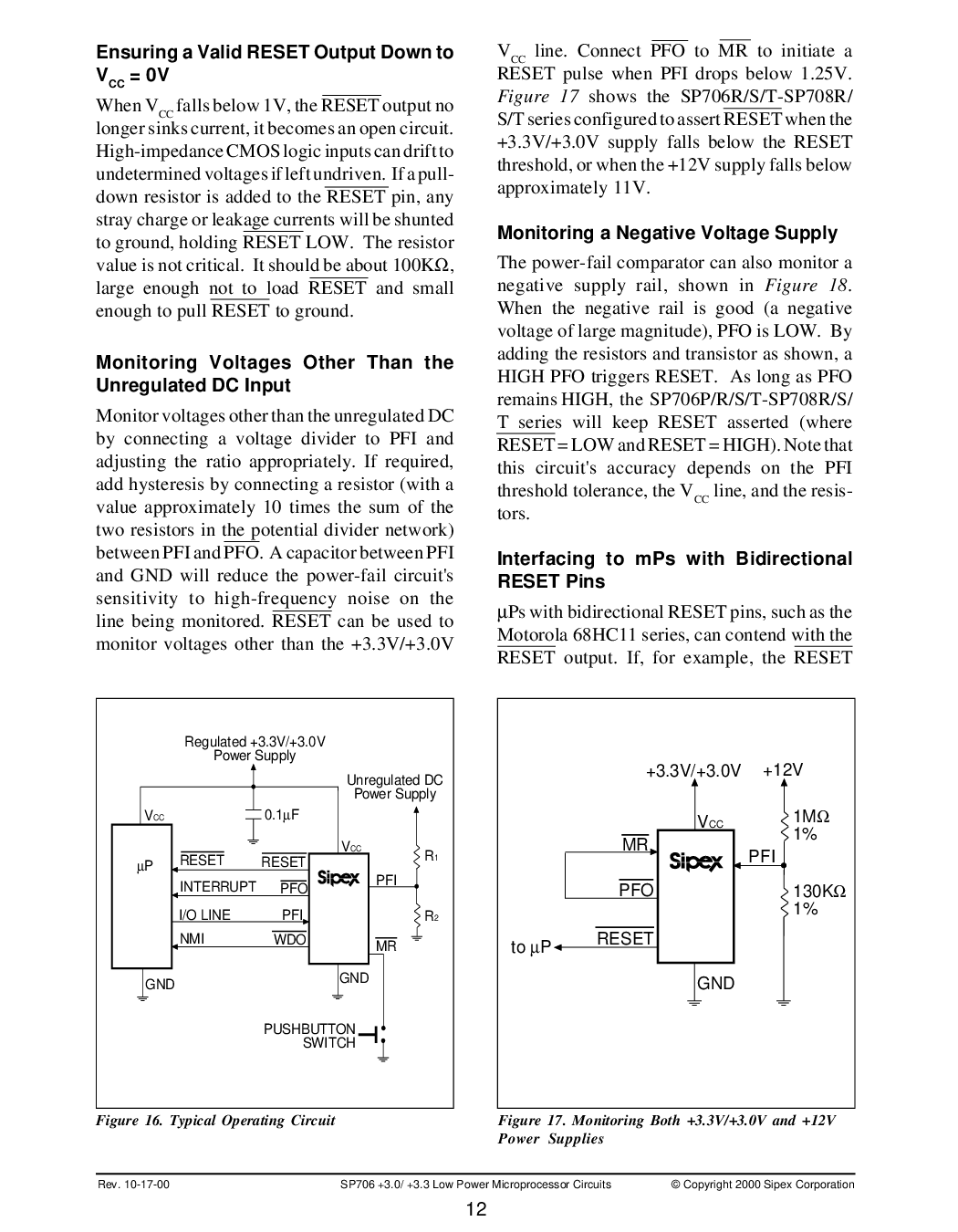

图示 17

显示 这 sp706r/s/t-sp708r/

s/t 序列 配置 至 assert 重置 当 这

+3.3v/+3.0v 供应 falls 在下 这 重置

门槛, 或者 当 这 +12v 供应 falls 在下

大概 11v.

monitoring 一个 负的 电压 供应

这 电源-失败 比较器 能 也 监控 一个

负的 供应 栏杆, 显示 在

图示 18

.

当 这 负的 栏杆 是 好的 (一个 负的

电压 的 大 巨大), pfo 是 低. 用

adding 这 电阻器 和 晶体管 作 显示, 一个

高 pfo triggers 重置. 作 长 作 pfo

仍然是 高, 这

sp706p/r/s/t-sp708r/s/

t 序列 将 保持 重置 asserted (在哪里

重置 = 低 和 重置 = 高). 便条 那

这个 电路's 精度 取决于 在 这 pfi

门槛 容忍, 这 v

CC

线条, 和 这 resis-

tors.

接合 至 mps 和 双向的

重置 管脚

µ

ps 和 双向的 重置 管脚, 此类 作 这

motorola 68hc11 序列, 能 contend 和 这

重置 输出. 如果, 为 例子, 这 重置

PFI

PFO

V

CC

+3.3v/+3.0v

地

重置

至

µ

P

MR

+12V

1M

Ω

1%

130K

Ω

1%

图示 17. monitoring 两个都 +3.3v/+3.0v 和 +12v

电源 供应

地

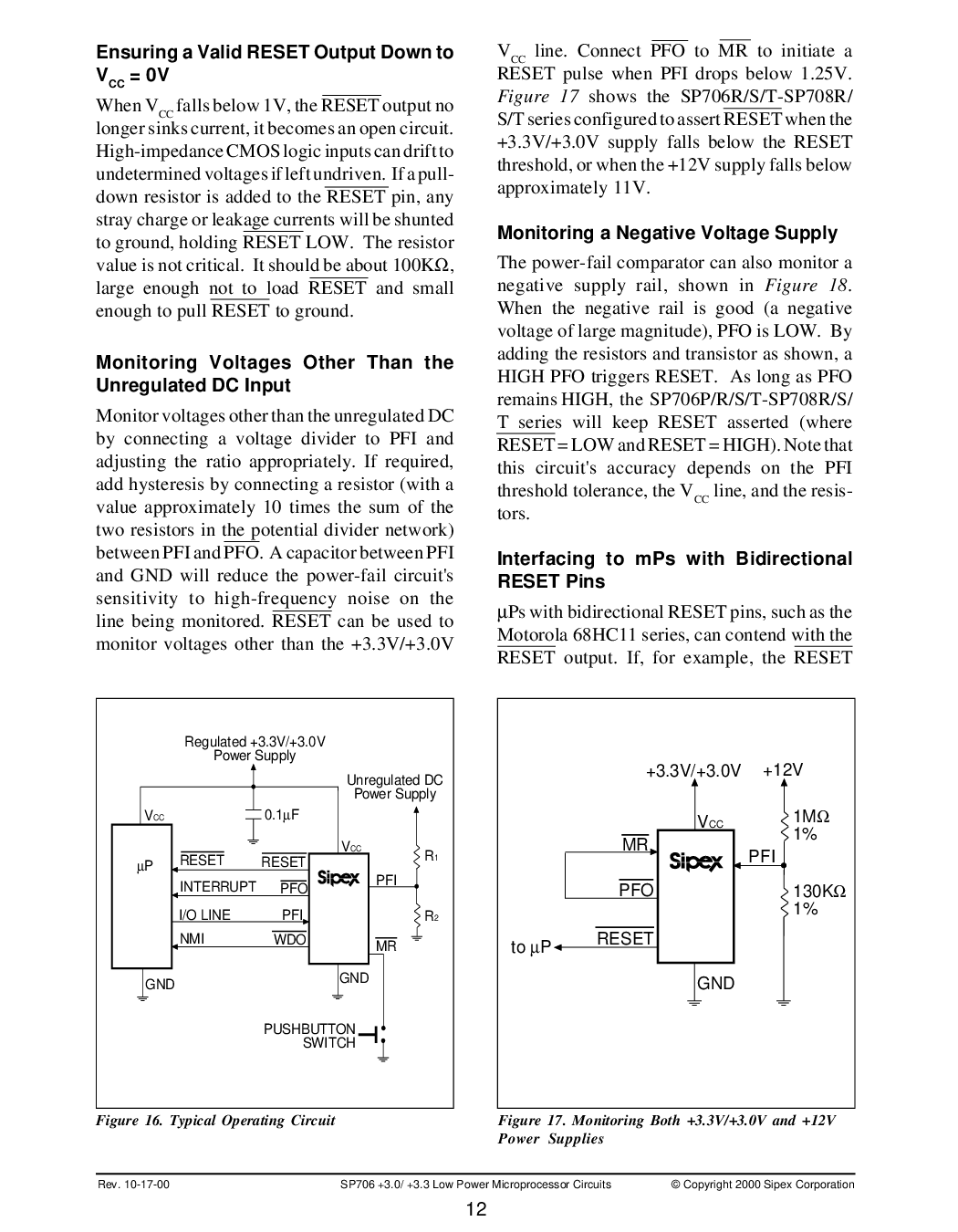

地

重置

中断

i/o 线条

V

CC

重置

PFO

PFI

R

2

R

1

无秩序的 直流

电源 供应

管制 +3.3v/+3.0v

电源 供应

V

CC

0.1

µ

F

PFI

µ

P

NMI

WDO

PUSHBUTTON

转变

MR

图示 16. 典型 运行 电路