描述特性

d flip-flop

和 设置 和 重置

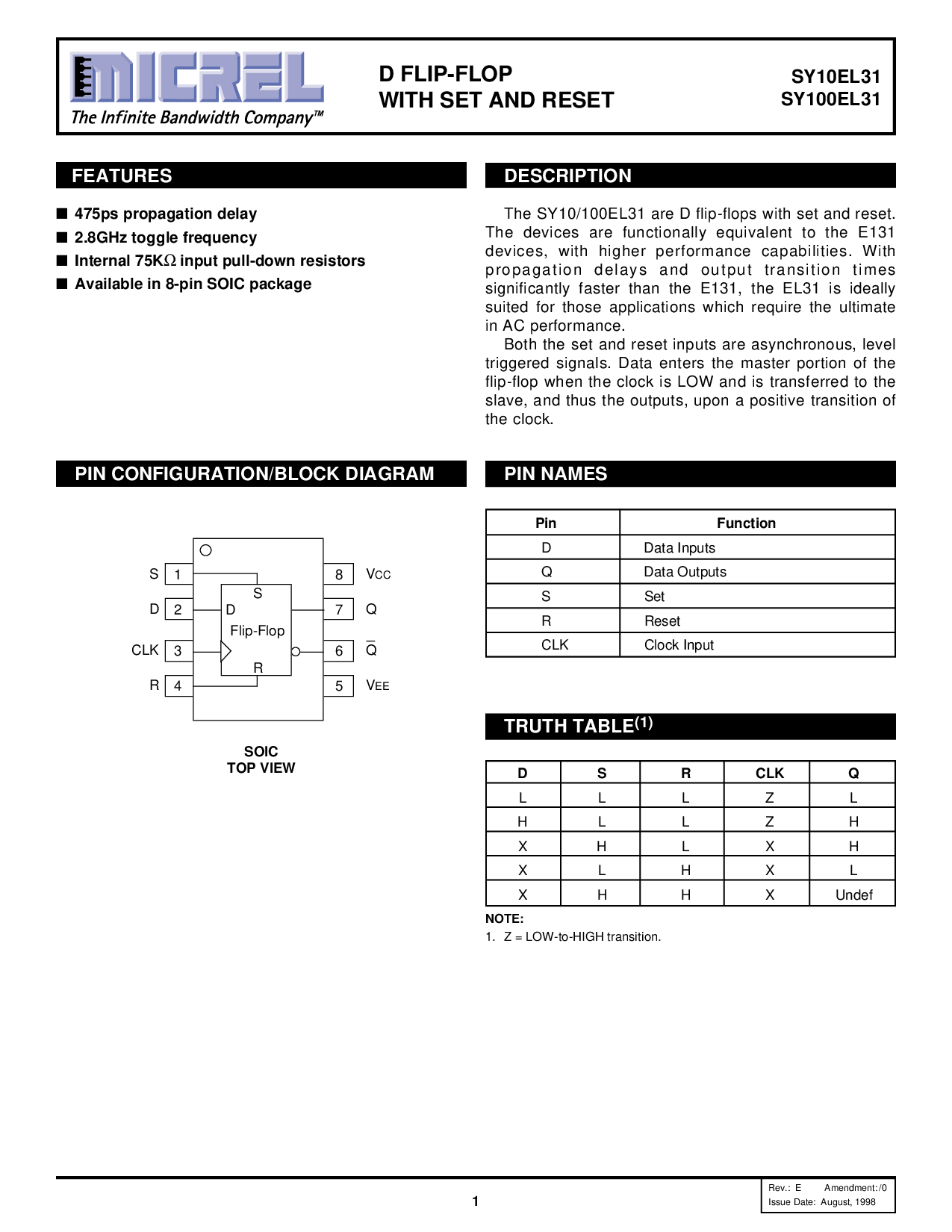

管脚 names

管脚 函数

D 数据 输入

Q 数据 输出

S 设置

R 重置

CLK 时钟 输入

管脚 配置/块 图解

rev.: e amendment: /0

公布 日期: 8月, 1998

SY10EL31

SY100EL31

■

475ps 传播 延迟

■

2.8ghz toggle 频率

■

内部的 75k

Ω

输入 拉-向下 电阻器

■

有 在 8-管脚 soic 包装

这 sy10/100el31 是 d flip-flops 和 设置 和 重置.

这 设备 是 functionally 相等的 至 这 e131

设备, 和 高等级的 效能 能力. 和

传播 延迟 和 输出 转变 时间

significantly faster 比 这 e131, 这 el31 是 ideally

suited 为 那些 产品 这个 需要 这 ultimate

在 交流 效能.

两个都 这 设置 和 重置 输入 是 异步的, 水平的

triggered 信号. 数据 enters 这 主控 portion 的 这

flip-flop 当 这 时钟 是 低 和 是 transferred 至 这

从动装置, 和 因此 这 输出, 在之上 一个 积极的 转变 的

这 时钟.

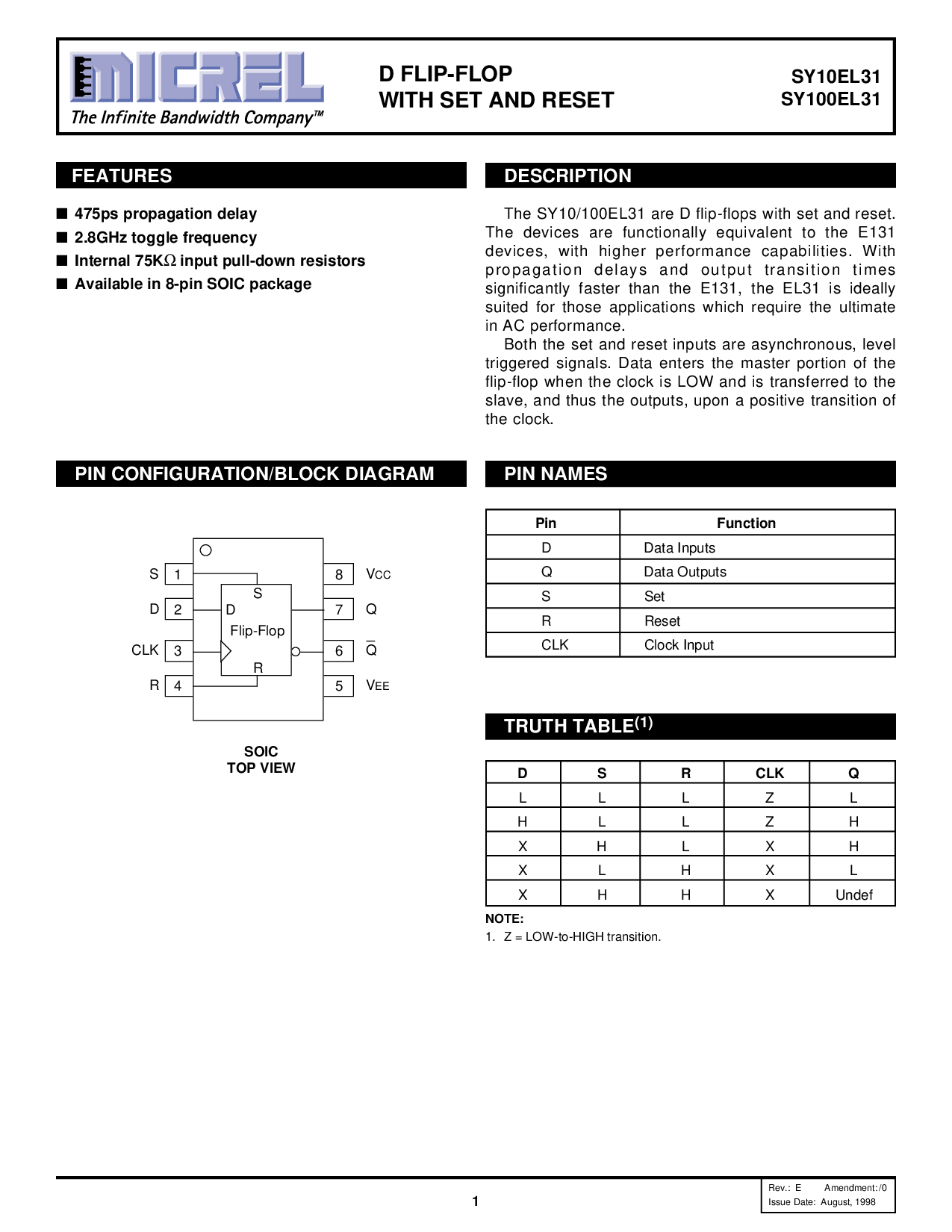

真实 表格

(1)

D S R CLK Q

LL L Z L

HL L Z H

XH L X H

XL H X L

X H H X Undef

便条:

1. z = 低-至-高 转变.

SOIC

顶 视图

1

2

3

45

6

7

8

SV

CC

Q

V

EE

D

R

CLK

Q

S

D

R

flip-flop

1