4

v54c3128(16/80/40)4v(t/s) rev.1.2 8月 2002

mosel vitelic

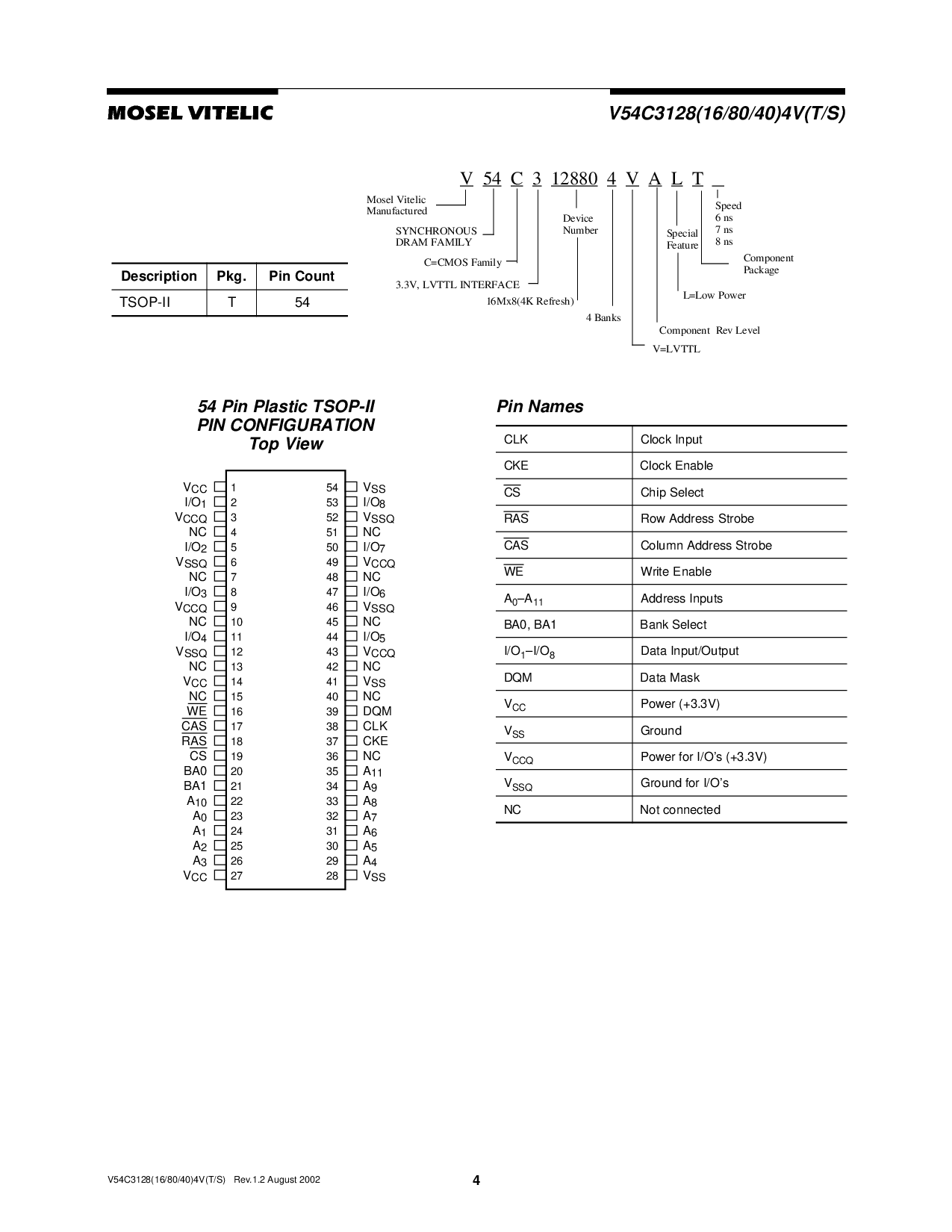

v54c3128(16/80/40)4v(t/s)

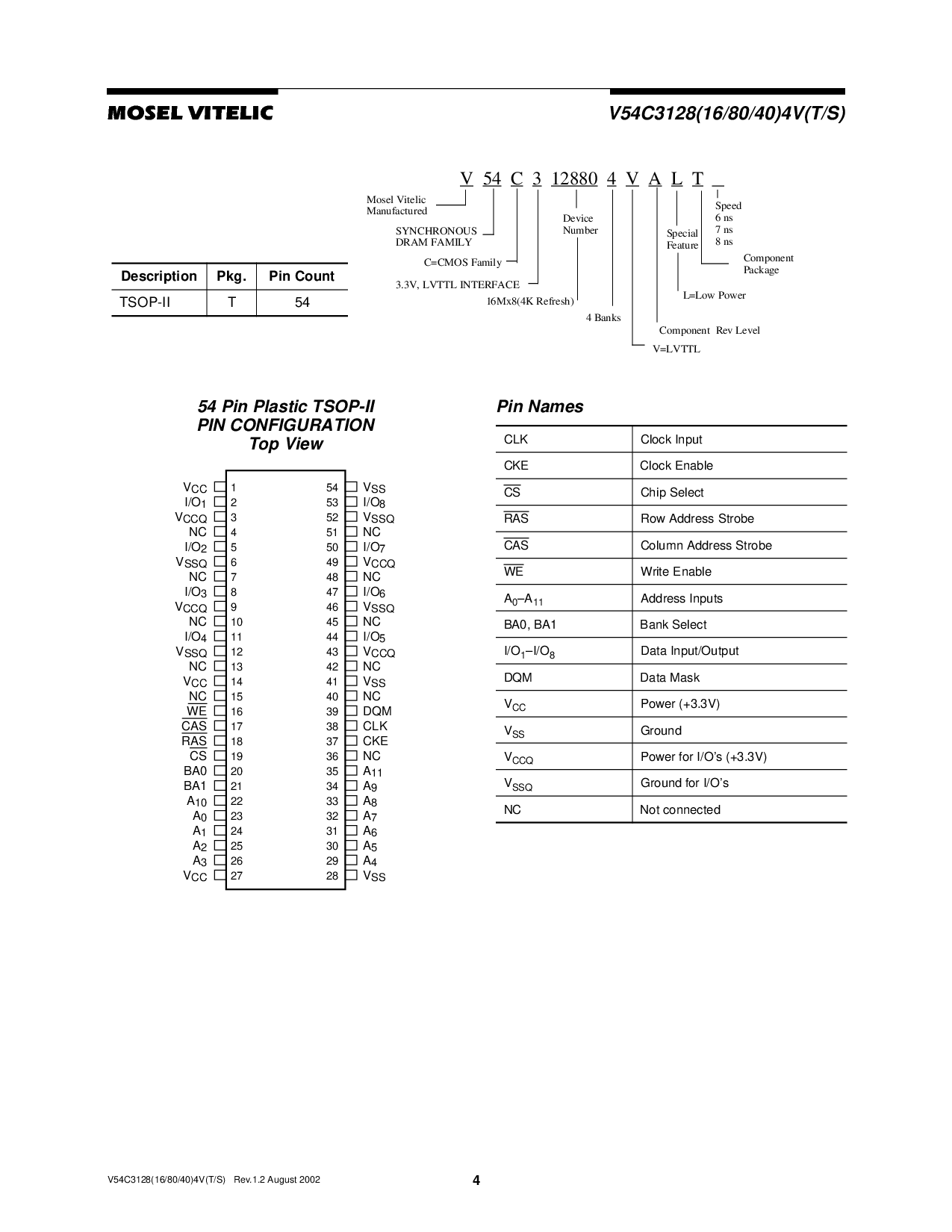

54 管脚 塑料 tsop-ii

管脚 配置

顶 视图

管脚 names

V

CC

i/o

1

V

CCQ

NC

i/o

2

V

SSQ

NC

i/o

3

V

CCQ

NC

i/o

4

V

SSQ

NC

V

CC

NC

我们

CAS

RAS

CS

BA0

BA1

一个

10

一个

0

一个

1

一个

2

一个

3

V

CC

V

SS

i/o

8

V

SSQ

NC

i/o

7

V

CCQ

NC

i/o

6

V

SSQ

NC

i/o

5

V

CCQ

NC

V

SS

NC

DQM

CLK

CKE

NC

一个

11

一个

9

一个

8

一个

7

一个

6

一个

5

一个

4

V

SS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

CLK 时钟 输入

CKE 时钟 使能

CS

碎片 选择

RAS

行 地址 strobe

CAS

column 地址 strobe

我们

写 使能

一个

0

–A

11

地址 输入

ba0, ba1 bank 选择

i/o

1

–i/o

8

数据 输入/输出

DQM 数据 掩饰

V

CC

电源 (+3.3v)

V

SS

地面

V

CCQ

电源 为 i/o’s (+3.3v)

V

SSQ

地面 为 i/o’s

NC 不 连接

V54C3128804V一个 lT

mosel vitelic

制造的

同步的

dram 家族

c=cmos 家族

3.3v, lvttl 接口

16mx8(4k refresh)

4 banks

V=LVTTL

组件 rev 水平的

特定的

特性

l=低 电源

组件

包装

速

6 ns

7 ns

8 ns

设备

号码

描述 pkg. 管脚 计数

tsop-ii T 54