7

规格

ispgdx160v/va

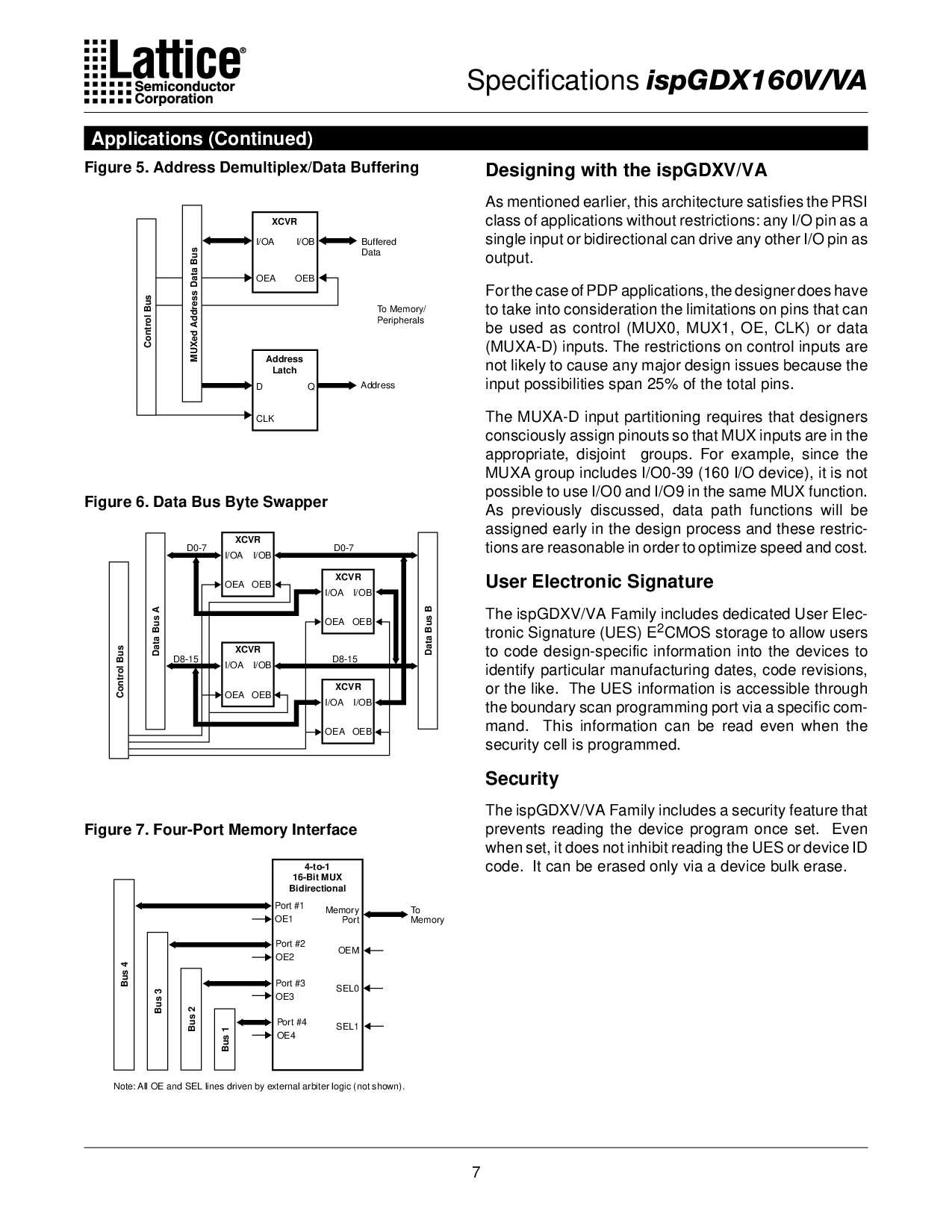

图示 6. 数据 总线 字节 swapper

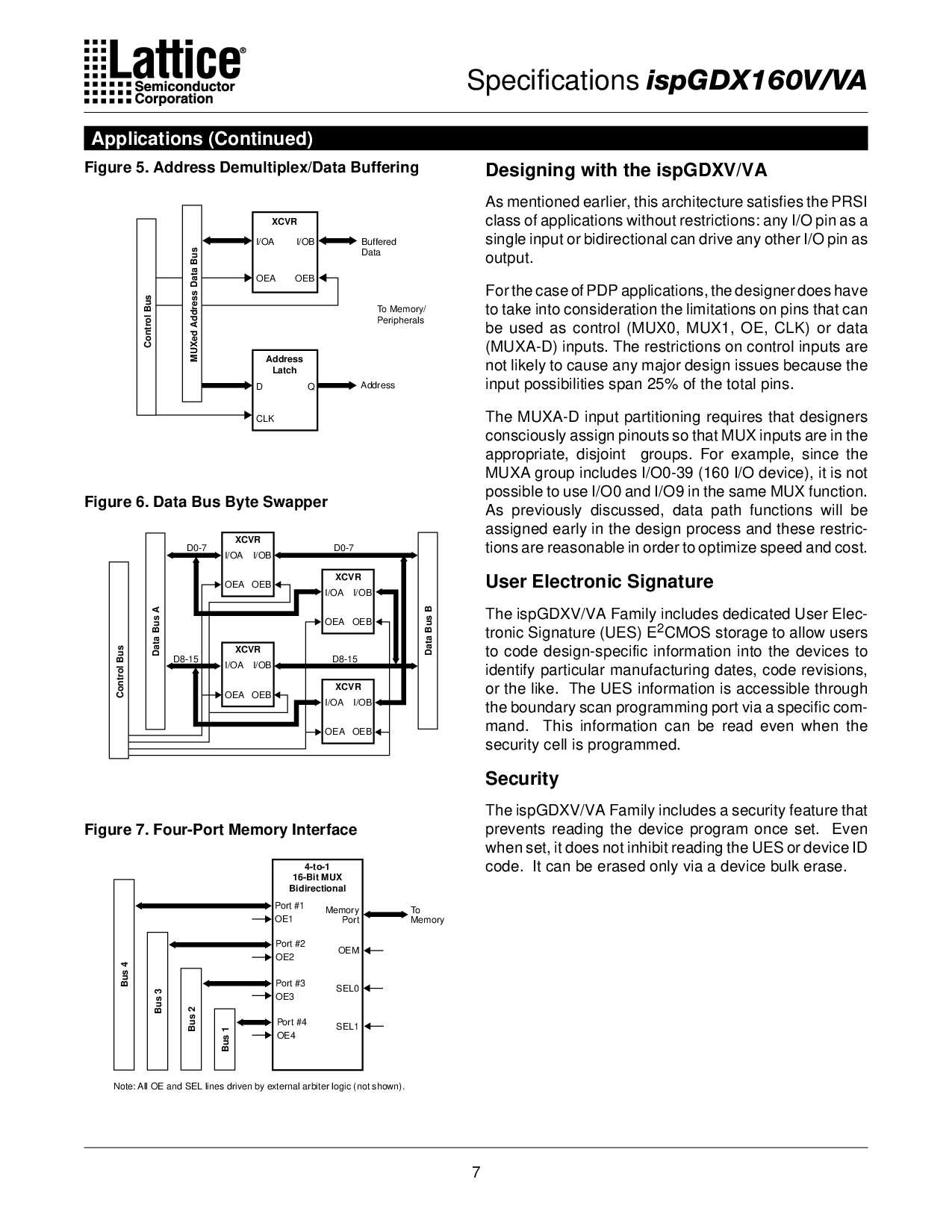

图示 7. 四-端口 记忆 接口

控制 总线

数据 总线 一个

数据 总线 b

OEA OEB

i/oa

d0-7

d8-15 d8-15

d0-7

i/ob

XCVR

OEA OEB

i/oa i/ob

XCVR

OEA OEB

i/oa i/ob

XCVR

OEA OEB

i/oa i/ob

XCVR

总线 4

总线 3

总线 2

总线 1

端口 #1

OE1

记忆

Port

OEM

SEL0

SEL1

至

记忆

端口 #2

OE2

端口 #3

OE3

便条: 所有 oe 和 sel 线条 驱动 用 外部 arbiter 逻辑 (不 显示).

端口 #4

OE4

4-至-1

16-位 mux

双向的

图示 5. 地址 demultiplex/数据 buffering

控制 总线

muxed 地址 数据 总线

DQ

CLK

OEA OEB

i/oa i/ob

地址

缓冲

数据

至 记忆/

Peripherals

XCVR

地址

获得

产品 (持续)

designing 和 这 ispgdxv/va

作 提到 早期, 这个 architecture satisfies 这 prsi

类 的 产品 没有 restrictions: 任何 i/o 管脚 作 一个

单独的 输入 或者 双向的 能 驱动 任何 其它 i/o 管脚 作

输出.

为 这 情况 的 pdp 产品, 这 设计者 做 有

至 引领 在 仔细考虑 这 限制 在 管脚 那 能

是 使用 作 控制 (mux0, mux1, oe, clk) 或者 数据

(muxa-d) 输入. 这 restrictions 在 控制 输入 是

不 likely 至 导致 任何 主要的 设计 issues 因为 这

输入 possibilities span 25% 的 这 总的 管脚.

这 muxa-d 输入 partitioning 需要 那 designers

consciously assign pinouts 所以 那 mux 输入 是 在 这

适合的, disjoint groups. 为 例子, 自从 这

muxa 组 包含 i/o0-39 (160 i/o 设备), 它 是 不

可能 至 使用 i/o0 和 i/o9 在 这 一样 mux 函数.

作 先前 discussed, 数据 path 功能 将 是

assigned early 在 这 设计 处理 和 这些 restric-

tions 是 合理的 在 顺序 至 优化 速 和 费用.

用户 电子的 signature

这 ispgdxv/va 家族 包含 专心致志的 用户 elec-

tronic signature (ues) e

2

cmos 存储 至 准许 用户

至 代号 设计-明确的 信息 在 这 设备 至

identify particular 制造 dates, 代号 revisions,

或者 这 像. 这 ues 信息 是 accessible 通过

这 boundary scan 程序编制 端口 通过 一个 明确的 com-

mand. 这个 信息 能 是 读 甚至 当 这

安全 cell 是 编写程序.

安全

这 ispgdxv/va 家族 包含 一个 安全 特性 那

阻止 读 这 设备 程序 once 设置. 甚至

当 设置, 它 做 不 inhibit 读 这 ues 或者 设备 id

代号. 它 能 是 erased 仅有的 通过 一个 设备 大(量) 擦掉.