WM8768

生产 数据

w

pd rev 4.1 march 2005

8

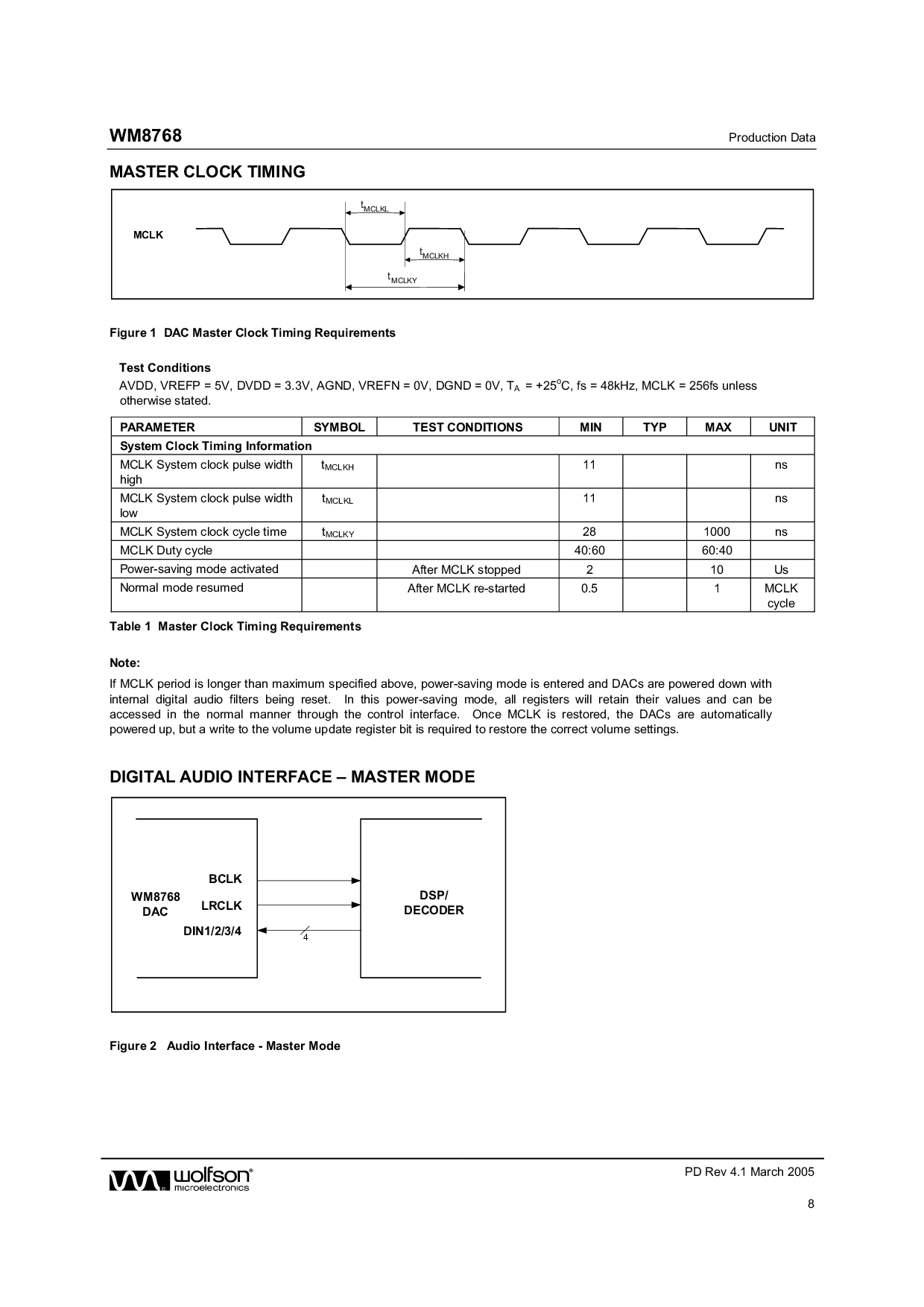

主控 时钟 定时

MCLK

t

MCLKL

t

MCLKH

t

MCLKY

图示 1 dac 主控 时钟 定时 (所需的)东西

测试 情况

avdd, vrefp = 5v, dvdd = 3.3v, agnd, vrefn = 0v, dgnd = 0v, t

一个

= +25

o

c, fs = 48khz, mclk = 256fs 除非

否则 陈述.

参数 标识 测试 情况 最小值 典型值 最大值 单位

系统 时钟 定时 信息

mclk 系统 时钟 脉冲波 宽度

高

t

MCLKH

11 ns

mclk 系统 时钟 脉冲波 宽度

低

t

MCLKL

11 ns

mclk 系统 时钟 循环 时间

t

MCLKY

28 1000 ns

mclk 职责 循环

40:60 60:40

电源-节省 模式 使活动

之后 mclk stopped 2 10 美国

正常的 模式 resumed

之后 mclk re-started 0.5 1 MCLK

循环

表格 1 主控 时钟 定时 (所需的)东西

便条:

如果 mclk时期 是 变长 比 最大 指定 在之上, 电源-节省 模式 是entered 和 dacs 是 powered 向下 和

内部的 数字的 音频的 过滤 正在 重置. 在 这个 电源-节省 模式, 所有 寄存器 将 retain 它们的 值 和 能 是

accessed 在 这 正常的 manner 通过 这 控制 接口. Once MCLK 是 restored, 这 DACs 是 automatically

powered 向上, 但是 一个 写 至 这 容积 更新 寄存器 位 是 必需的 至 restore 这 准确无误的 容积 settings.

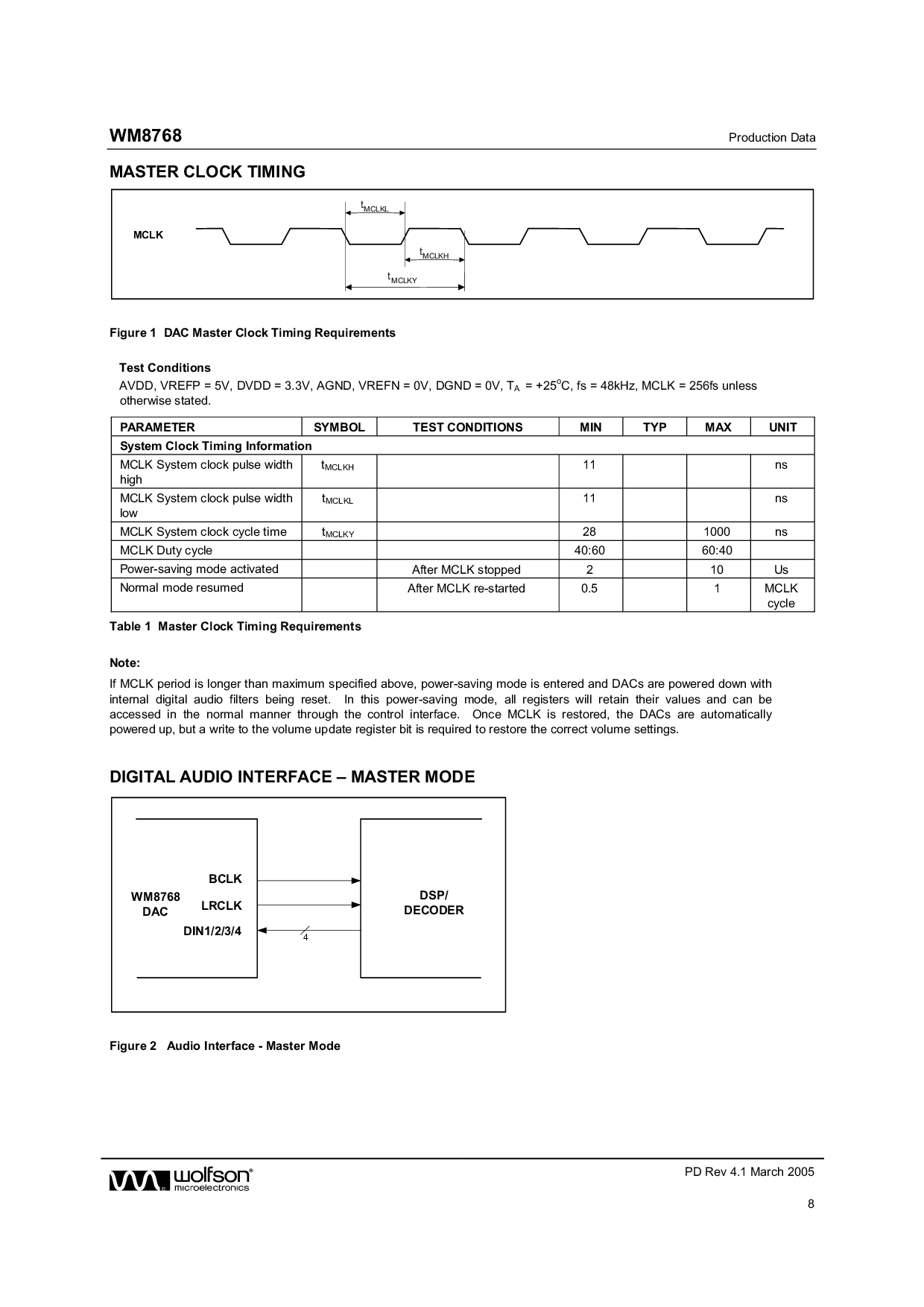

数字的 音频的 接口 – 主控 模式

BCLK

din1/2/3/4

LRCLK

WM8768

DAC

dsp/

解码器

4

图示 2 音频的 接口 - 主控 模式