– 5 –

CXA3026Q

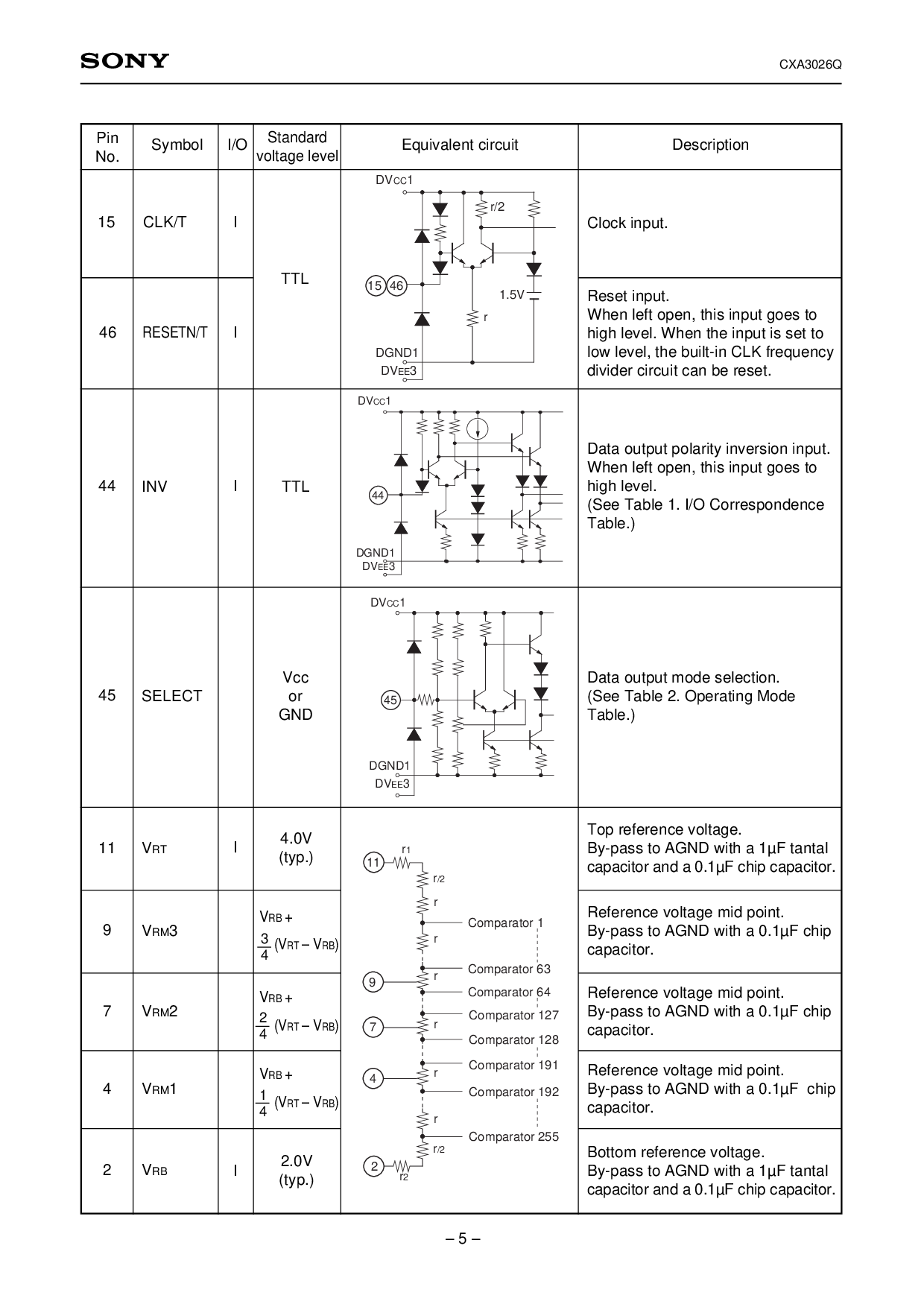

15 clk/t

时钟 输入.

46

resetn/t

TTL

TTL

Vcc

或者

地

重置 输入.

当 left 打开, 这个 输入 变得 至

高 水平的. 当 这 输入 是 设置 至

低 水平的, 这 建造-在 clk 频率

分隔物 电路 能 是 重置.

44

INV

数据 输出 极性 倒置 输入.

当 left 打开, 这个 输入 变得 至

高 水平的.

(看 表格 1. i/o correspondence

表格.)

45

选择

数据 输出 模式 选择.

(看 表格 2. 运行 模式

表格.)

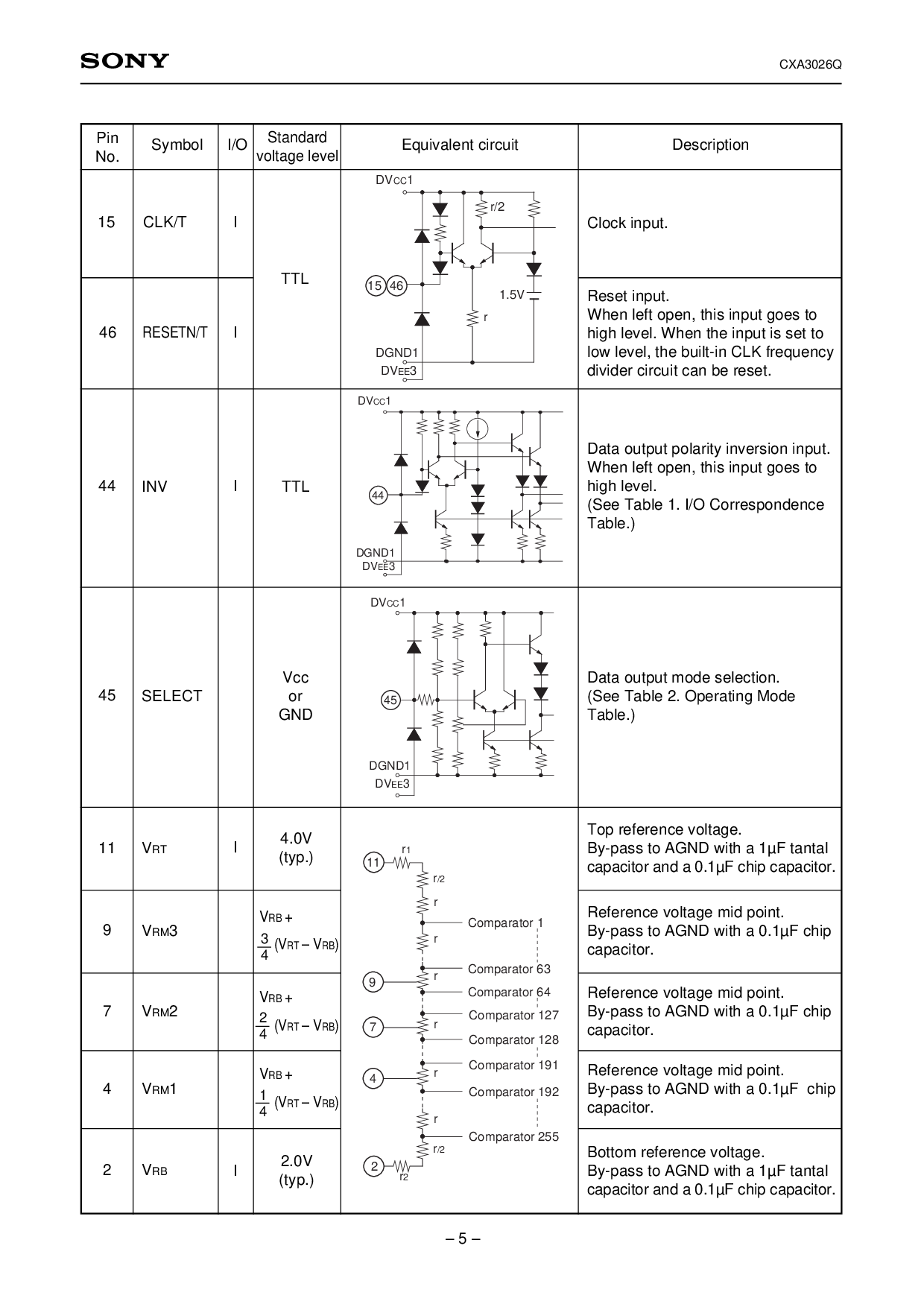

4.0v

(典型值.)

11

V

RT

顶 涉及 电压.

用-通过 至 agnd 和 一个 1µf tantal

电容 和 一个 0.1µf 碎片 电容.

V

RB

+

(v

RT

– v

RB

)

9

V

RM

3

涉及 电压 mid 要点.

用-通过 至 agnd 和 一个 0.1µf 碎片

电容.

7

V

RM

2

涉及 电压 mid 要点.

用-通过 至 agnd 和 一个 0.1µf 碎片

电容.

4

V

RM

1

涉及 电压 mid 要点.

用-通过 至 agnd 和 一个 0.1µf 碎片

电容.

2.0v

(典型值.)

2

V

RB

bottom 涉及 电压.

用-通过 至 agnd 和 一个 1µf tantal

电容 和 一个 0.1µf 碎片 电容.

DV

CC

1

DGND1

1.5v

r/2

r

DV

EE

3

15

46

DV

CC

1

DGND1

DV

EE

3

44

DV

CC

1

DGND1

DV

EE

3

45

r

1

r

/2

比较器 1

比较器 63

比较器 64

比较器 128

比较器 191

比较器 127

比较器 192

比较器 255

r

r

2

r

/2

r

r

r

r

4

7

9

2

11

r

I

I

I

I

I

4

3

4

2

V

RB

+

(v

RT

– v

RB

)

4

1

V

RB

+

(v

RT

– v

RB

)

管脚

非.

标识 i/o

标准

电压 水平的

相等的 电路 描述