ds026 (v4.0) 六月 11, 2003

www.xilinx.com

1

产品 规格

1-800-255-7778

©2003 xilinx, 公司 所有 权利 保留. 所有 xilinx 商标, 注册 商标, patents, 和 更远 免责声明 是 作 listed 在

http://www.xilinx.com/legal.htm

. 所有 其它

商标 和 注册 商标 是 这 所有物 的 它们的 各自的 所有权人. 所有 规格 是 主题 至 改变 和输出 注意.

注意 的 免责声明: xilinx 是 供应 这个 设计, 代号, 或者 信息 "作 is." 用 供应 这 design, code, 或者 information 作 一个 可能 implementation 的 这个 fea-

ture, 应用, 或者 标准, xilinx 制造 非 描述 那 这个 implementation 是 自由 从 任何 claims 的 侵犯. 你 是 有责任 为 获得 任何 权利 你

将 需要 为 your implementation. xilinx expressly disclaims 任何 保用单 whatsoever 和 遵守 至 这 adequacy 的 这 implementation, 包含 但是 不 限制 至 任何 war-

ranties 或者 描述 那 这个 implementation 是 自由 从 claims 的 侵犯 和 任何 暗指 保用单 的 merchantability 或者 fitness 为 一个 particular 目的.

特性

• 在-系统 可编程序的 3.3v proms 为

配置 的 xilinx fpgas

- 忍耐力 的 20,000 程序/擦掉 循环

- 程序/擦掉 在 全部 商业的/工业的

电压 和 温度 范围 (–40°c 至 +85°c)

• ieee 标准 1149.1 boundary-scan (jtag) 支持

• 简单的 接口 至 这 fpga

• cascadable 为 storing 变长 或者 多样的 bitstreams

• 低-电源 先进的 cmos flash 处理

• 双 配置 模式

- 串行 慢/快 配置 (向上 至 33 mhz)

- 并行的 (向上 至 264 mb/s 在 33 mhz)

• 5v tolerant i/o 管脚 接受 5v, 3.3v 和 2.5v 信号

• 3.3v 或者 2.5v 输出 能力

• 有 在 pc20, so20, pc44, 和 vq44 包装

• 设计 支持 使用 这 xilinx alliance 和

foundation 序列 软件 包装.

• jtag command initiation 的 标准 fpga

配置

描述

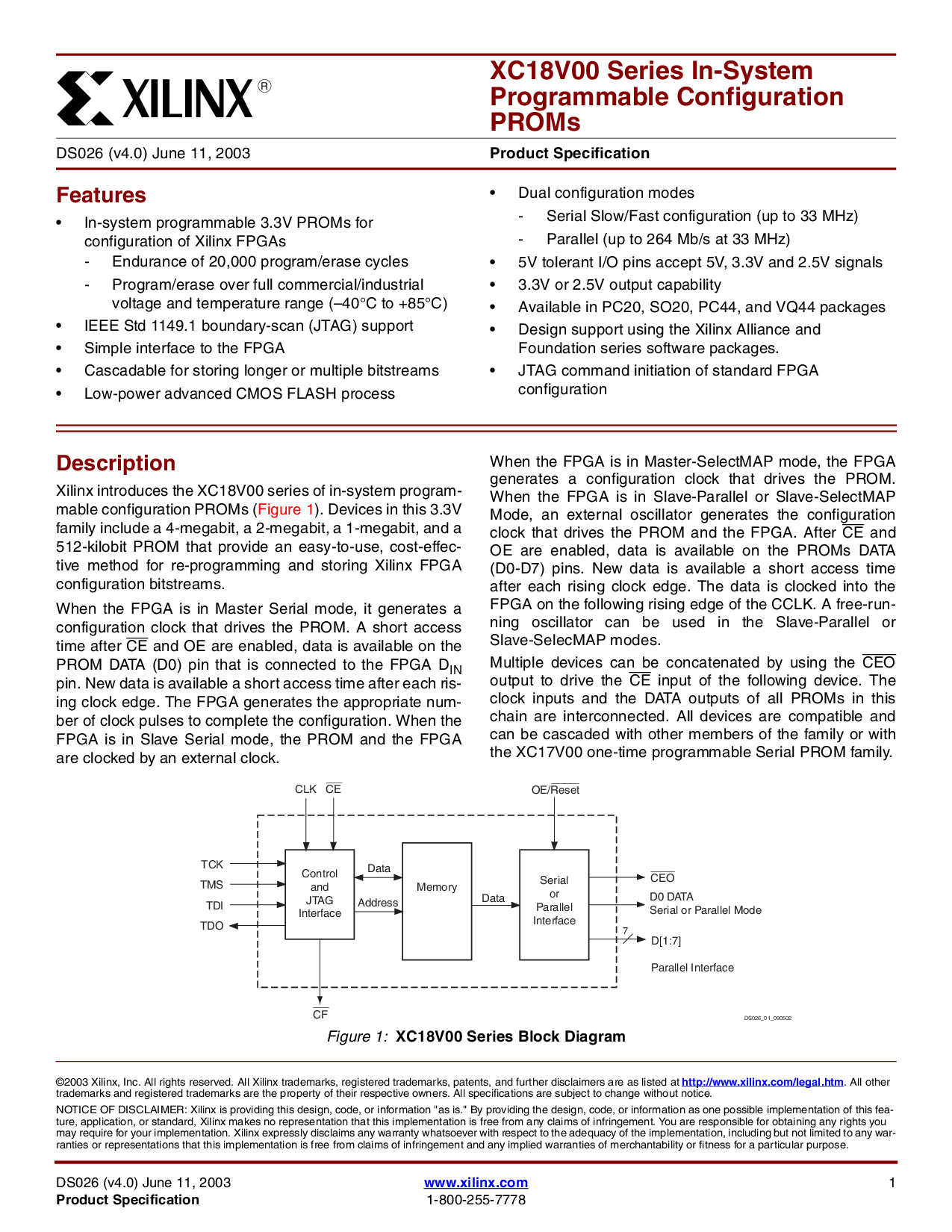

xilinx introduces 这 xc18v00 序列 的 在-系统 程序-

mable 配置 proms (图示 1). 设备 在 这个 3.3v

家族 包含 一个 4-megabit, 一个 2-megabit, 一个 1-megabit, 和 一个

512-kilobit prom 那 提供 一个 容易-至-使用, 费用-effec-

tive 方法 为 re-程序编制 和 storing xilinx fpga

配置 bitstreams.

当 这 fpga 是 在 主控 串行 模式, 它 发生 一个

配置 时钟 那 驱动 这 prom. 一个 short 进入

时间 之后 ce

和 oe 是 使能, 数据 是 有 在 这

prom 数据 (d0) 管脚 那 是 连接 至 这 fpga d

在

管脚. 新 数据 是 有 一个 short 进入 时间 之后 各自 ris-

ing 时钟 边缘. 这 fpga 发生 这 适合的 num-

ber 的 时钟 脉冲 至 完全 这 配置. 当 这

fpga 是 在 从动装置 串行 模式, 这 prom 和 这 fpga

是 clocked 用 一个 外部 时钟.

当 这 fpga 是 在 主控-selectmap 模式, 这 fpga

发生 一个 配置 时钟 那 驱动 这 prom.

当 这 fpga 是 在 从动装置-并行的 或者 从动装置-selectmap

模式, 一个 外部 振荡器 发生 这 配置

时钟 那 驱动 这 prom 和 这 fpga. 之后 ce

和

oe 是 使能, 数据 是 有 在 这 proms 数据

(d0-d7) 管脚. 新 数据 是 有 一个 short 进入 时间

之后 各自 rising 时钟 边缘. 这 数据 是 clocked 在 这

fpga 在 这 下列的 rising 边缘 的 这 cclk. 一个 自由-run-

ning 振荡器 能 是 使用 在 这 从动装置-并行的 或者

从动装置-selecmap 模式.

多样的 设备 能 是 concatenated 用 使用 这 ceo

输出 至 驱动 这 ce输入 的 这 下列的 设备. 这

时钟 输入 和 这 数据 输出 的 所有 proms 在 这个

chain 是 interconnected. 所有 设备 是 兼容 和

能 是 倾泻 和 其它 members 的 这 家族 或者 和

这 xc17v00 一个-时间 可编程序的 串行 prom 家族.

0

xc18v00 序列 在-系统

可编程序的 配置

PROMs

ds026 (v4.0) 六月 11, 2003

00

产品 规格

R

图示 1:

xc18v00 序列 块 图解

控制

和

JTAG

接口

记忆

串行

或者

并行的

接口

d0 数据

串行 或者 并行的 模式

d[1:7]

并行的 接口

数据

地址

CLK

CE

TCK

TMS

TDI

TDO

oe/重置

CEO

数据

ds026_01_090502

7

CF