ds017 (v1.6) january 8, 2002

www.xilinx.com

1

产品 规格

1-800-255-7778

© 2002 xilinx, 公司 所有 权利 保留. 所有 xilinx 商标, 注册 商标, patents, 和 免责声明 是 作 列表 一个t

http://www.xilinx.com/legal.htm

.

所有 其它 商标 和 注册 商标 是 这 所有物 的 它们的 各自的 所有权人. 所有 规格 是 主题 至 change 没有 注意.

特性

• 最低 电源 64 macrocell cpld

• 6.0 ns 管脚-至-管脚 逻辑 延迟

• 系统 发生率 向上 至 145 mhz

• 64 macrocells 和 1,500 usable 门

• 有 在 小 footprint 包装

- 44-管脚 plcc (36 用户 i/o 管脚)

- 44-管脚 vqfp (36 用户 i/o 管脚)

- 48-球 cs bga (40 用户 i/o 管脚)

- 56-球 cp bga (48 用户 i/o 管脚)

- 100-管脚 vqfp (68 用户 i/o 管脚)

• 优化 为 3.3v 系统

- 过激-低 电源 运作

- 5v tolerant i/o 管脚 和 3.3v 核心 供应

- 先进的 0.35 micron five layer metal 可擦可编程只读存储器

处理

- 快 零 power™ (fzp) cmos 设计

技术

• 先进的 系统 特性

- 在-系统 程序编制

- 输入 寄存器

- predictable 定时 模型

- 向上 至 23 有 clocks 每 函数 块

- 极好的 管脚 保持 在 设计 改变

- 全部 ieee 标准 1149.1 boundary-scan (jtag)

- 四 global clocks

- 第八 产品 期 控制 条款 每 函数 块

• 快 isp 程序编制 时间

• 端口 使能 管脚 为 双 函数 的 jtag isp 管脚

• 2.7v 至 3.6v 供应 电压 在 工业的 温度

range

• 可编程序的 回转 比率 控制 每 macrocell

• 安全 位 阻止 unauthorized 进入

• 谈及 至 xpla3 家族 数据 薄板 (

DS012

) 为

architecture 描述

描述

这 xcr3064xl 是 一个 3.3v, 64-macrocell cpld targeted 在

电源 敏感的 设计 那 需要 leading 边缘 程序-

mable 逻辑 解决方案. 一个 总的 的 四 函数 blocks 提供

1,500 usable 门. 管脚-至-管脚 传播 延迟 是

6.0 ns 和 一个 最大 系统 频率 的 145 mhz.

totalcmos 设计 技巧 为 快

零 电源

xilinx 提供 一个 totalcmos cpld, 两个都 在 处理 technol-

ogy 和 设计 技巧. xilinx 雇用 一个 cascade 的

cmos 门 至 执行 它的 总 的 产品 instead 的

这 传统的 sense 放大 approach. 这个 cmos 门 imple-

mentation 准许 xilinx 至 提供 cplds 那 是 两个都 高

效能 和 低 电源, breaking 这 paradigm 那 至

有 低 电源, 你 必须 有 低 效能. 谈及 至

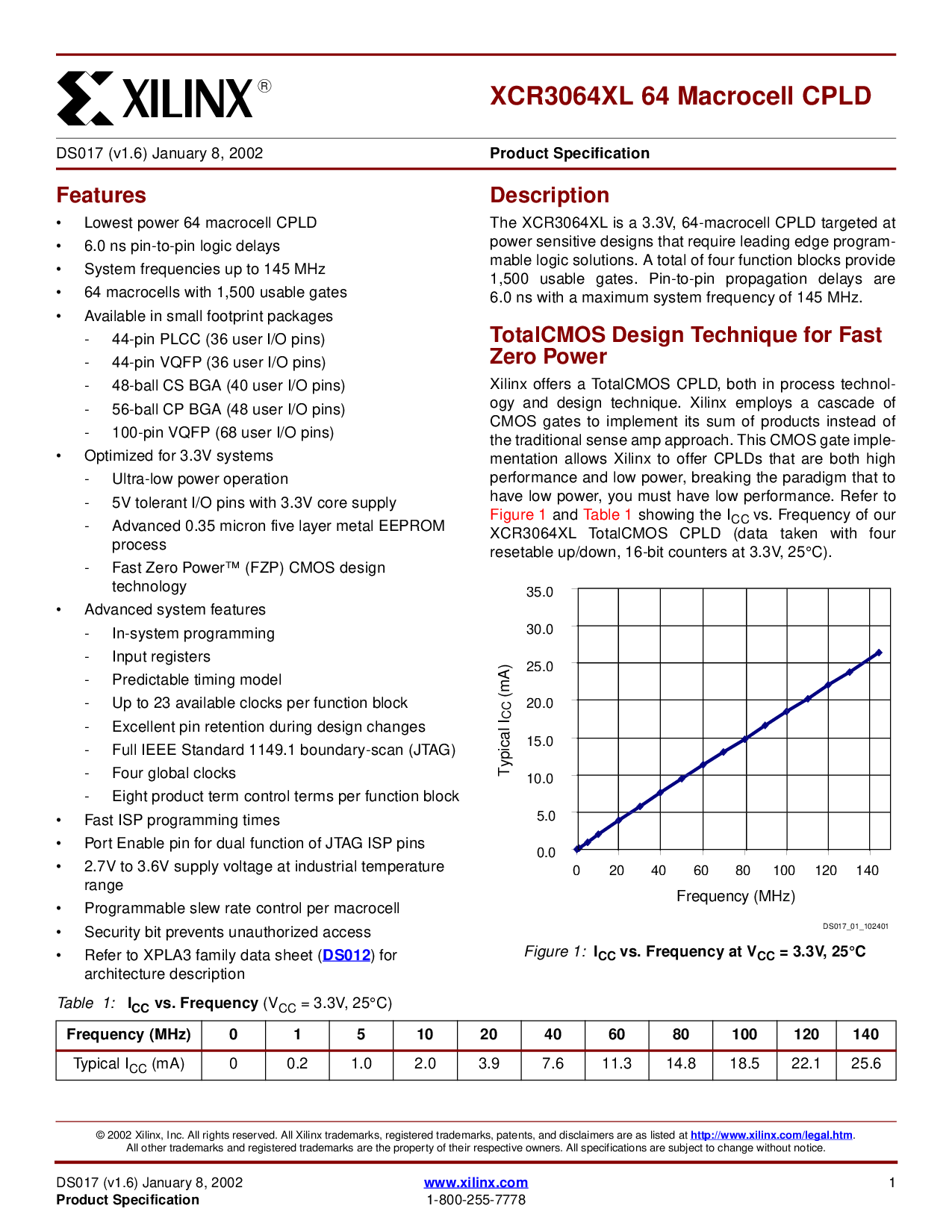

图示 1和表格 1表明 这 i

CC

vs. 频率 的 我们的

xcr3064xl totalcmos cpld (数据 带去 和 四

resetable 向上/向下, 16-位 counters 在 3.3v, 25

°

c).

0

xcr3064xl 64 macrocell cpld

ds017 (v1.6) january 8, 2002

014

产品 规格

R

图示 1:

I

CC

vs. 频率 在 v

CC

= 3.3v, 25°c

0.0

5.0

10.0

15.0

20.0

25.0

30.0

35.0

0 20 40 60 80 100 120 140

频率 (mhz)

DS017_01_102401

典型 i

CC

(毫安)

表格 1:

I

CC

vs. 频率

(v

CC

= 3.3v, 25

°

c)

频率 (mhz) 0 1 5 10 20 40 60 80 100 120 140

Ty p ic 一个 l I

CC

(毫安) 0 0.2 1.0 2.0 3.9 7.6 11.3 14.8 18.5 22.1 25.6