rev. 一个

ad7475/ad7495

–5–

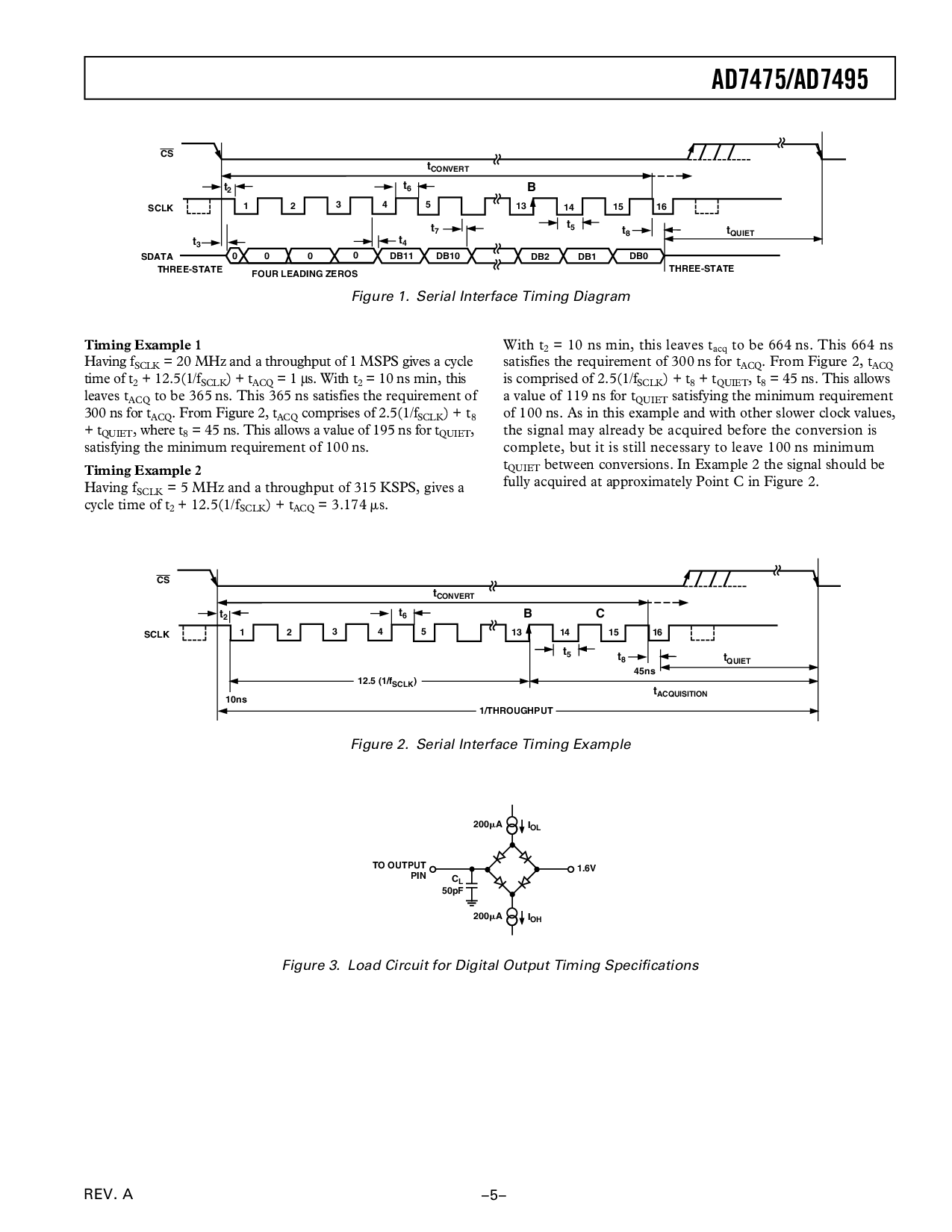

SCLK

1

5

13

15

SDATA

四 leading zeros

三-状态

t

4

2

34

16

t

5

t

3

t

安静

t

转变

t

2

三-状态

DB11 DB10

DB2

DB0

t

6

t

7

t

8

14

0

0

00

B

DB1

CS

图示 1. 串行 接口 定时 图解

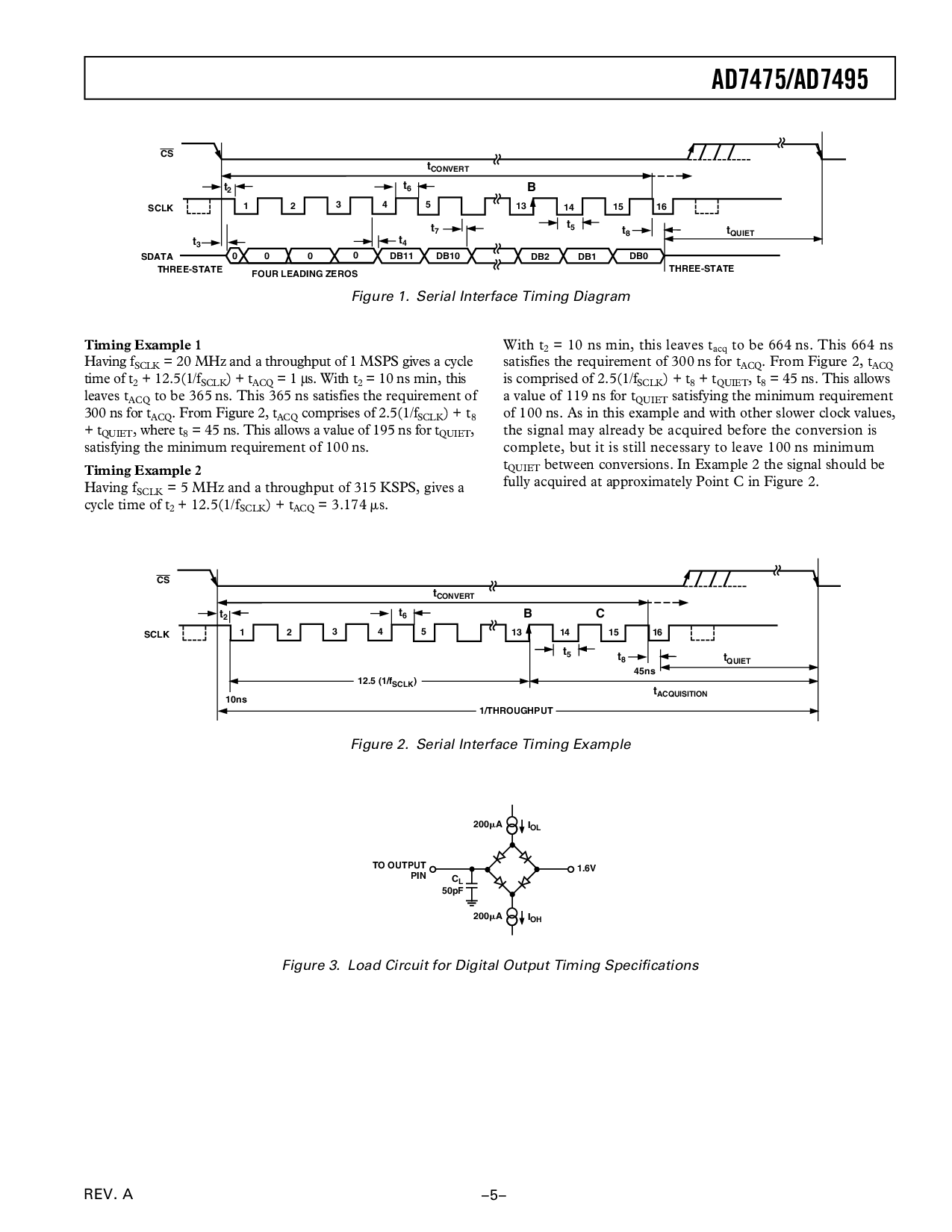

定时 例子 1

having f

SCLK

= 20 mhz 和 一个 throughput 的 1 msps 给 一个 循环

时间 的 t

2

+ 12.5(1/f

SCLK

) + t

ACQ

= 1

µ

s. 和 t

2

= 10 ns 最小值,这个

leaves t

ACQ

至 是 365 ns. 这个 365 ns satisfies 这 必要条件 的

300 ns 为 t

ACQ

. 从 图示 2, t

ACQ

comprises 的 2.5(1/f

SCLK

) + t

8

+ t

安静

, 在哪里 t

8

= 45 ns. 这个 准许 一个 值 的 195 ns 为 t

安静

,

satisfying 这 最小 必要条件 的 100 ns.

定时 例子 2

having f

SCLK

= 5 mhz 和 一个 throughput 的 315 ksps, 给 一个

循环 时间 的 t

2

+ 12.5(1/f

SCLK

) + t

ACQ

= 3.174

s.

和 t

2

= 10 ns 最小值, 这个 leaves t

acq

至 是 664 ns. 这个 664 ns

satisfies 这 必要条件 的 300 ns 为 t

ACQ

. 从 图示 2, t

ACQ

是 包括 的 2.5(1/f

SCLK

) + t

8

+ t

安静

, t

8

= 45 ns. 这个 准许

一个 值 的 119 ns 为 t

安静

satisfying 这 最小 必要条件

的 100 ns. 作 在 这个 例子 和 和 其它 slower 时钟 值,

这 信号 将 already 是 acquired 在之前 这 转换 是

完全, 但是 它 是 安静的 需要 至 leave 100 ns 最小

t

安静

在 conversions. 在 例子 2 这 信号 应当 是

全部地 acquired 在 大概 要点 c 在 图示 2.

SCLK

1

5

13

15

2

34

16

t

5

t

安静

t

转变

t

2

t

6

t

8

14

B

CS

45ns

t

ACQUISITION

12.5 (1/f

SCLK

)

10ns

1/throughput

C

图示 2. 串行 接口 定时 例子

200

一个

I

OL

200

一个

I

OH

C

L

50pF

至 输出

管脚

1.6v

图示 3. 加载 电路 为 数字的 输出 定时 规格