CY7B9910

CY7B9920

4

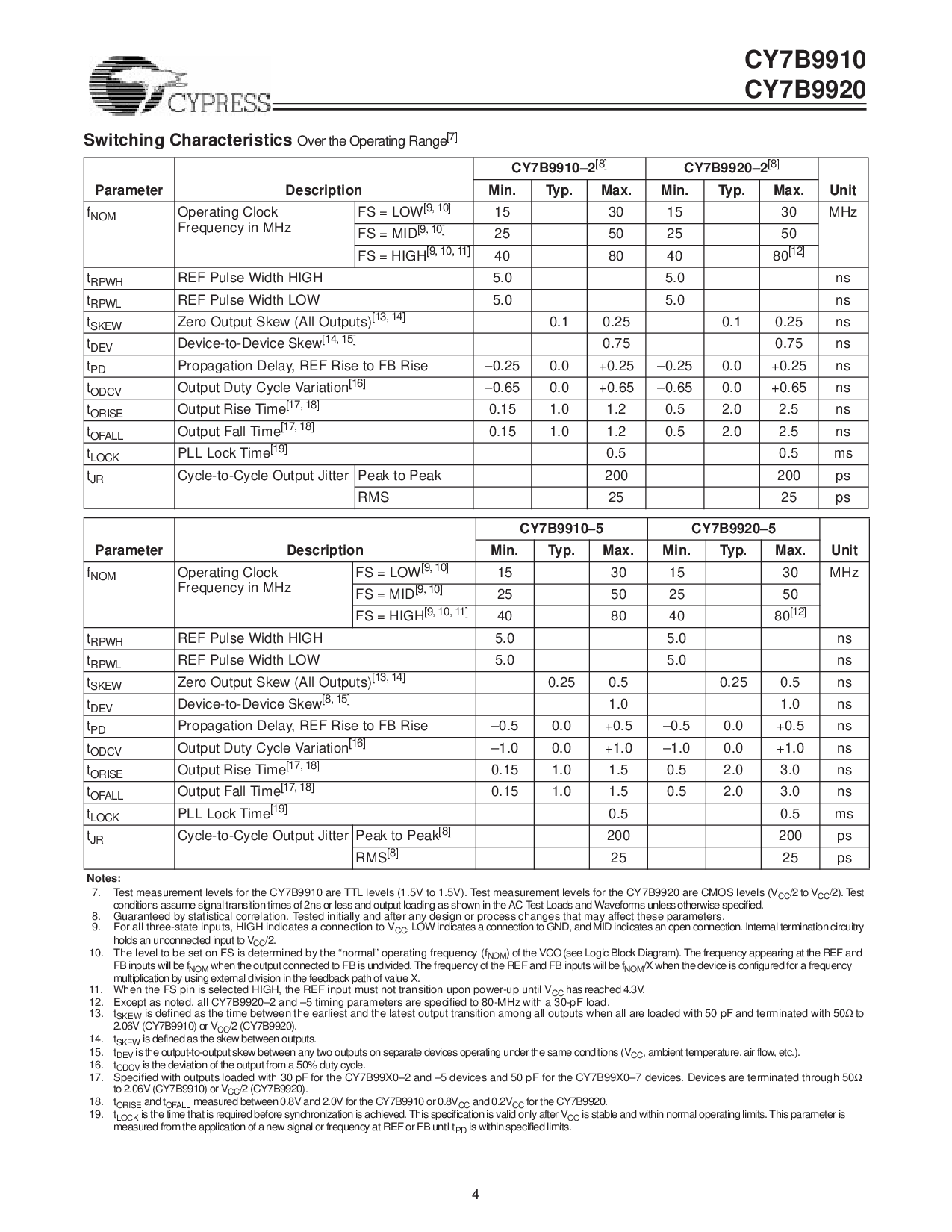

切换 特性

在 这 运行 范围

[7]

CY7B9910–2

[8]

CY7B9920–2

[8]

参数 描述 最小值 典型值 最大值 最小值 典型值 最大值 单位

f

NOM

运行 时钟

频率 在 mhz

fs = 低

[9, 10]

15 30 15 30 MHz

fs = mid

[9, 10]

25 50 25 50

fs = 高

[9, 10, 11]

40 80 40 80

[12]

t

RPWH

ref 脉冲波 宽度 高 5.0 5.0 ns

t

RPWL

ref 脉冲波 宽度 低 5.0 5.0 ns

t

SKEW

零 输出 skew (所有 输出)

[13, 14]

0.1 0.25 0.1 0.25 ns

t

DEV

设备-至-设备 skew

[14, 15]

0.75 0.75 ns

t

PD

传播 延迟, ref 上升 至 fb 上升 –0.25 0.0 +0.25 –0.25 0.0 +0.25 ns

t

ODCV

输出 职责 循环 变化

[16]

–0.65 0.0 +0.65 –0.65 0.0 +0.65 ns

t

ORISE

输出 上升 时间

[17, 18]

0.15 1.0 1.2 0.5 2.0 2.5 ns

t

OFALL

输出 下降 时间

[17, 18]

0.15 1.0 1.2 0.5 2.0 2.5 ns

t

锁

pll 锁 时间

[19]

0.5 0.5 ms

t

JR

循环-至-循环 输出 jitter 顶峰 至 顶峰 200 200 ps

RMS 25 25 ps

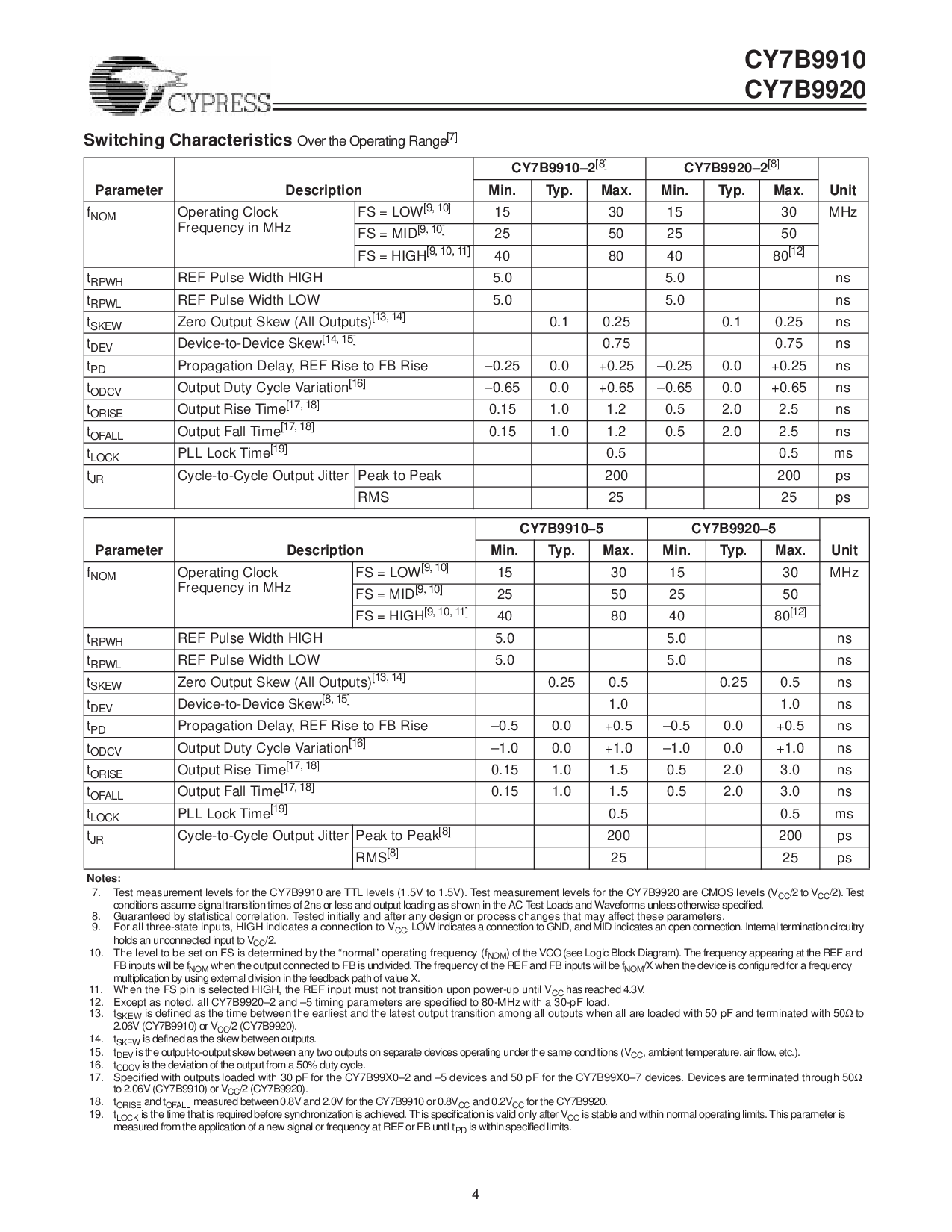

CY7B9910–5 CY7B9920–5

参数 描述 最小值 典型值 最大值 最小值 Typ. 最大值 单位

f

NOM

运行 时钟

频率 在 mhz

fs = 低

[9, 10]

15 30 15 30 MHz

fs = mid

[9, 10]

25 50 25 50

fs = 高

[9, 10, 11]

40 80 40 80

[12]

t

RPWH

ref 脉冲波 宽度 高 5.0 5.0 ns

t

RPWL

ref 脉冲波 宽度 低 5.0 5.0 ns

t

SKEW

零 输出 skew (所有 输出)

[13, 14]

0.25 0.5 0.25 0.5 ns

t

DEV

设备-至-设备 skew

[8, 15]

1.0 1.0 ns

t

PD

传播 延迟, ref 上升 至 fb 上升 –0.5 0.0 +0.5 –0.5 0.0 +0.5 ns

t

ODCV

输出 职责 循环 变化

[16]

–1.0 0.0 +1.0 –1.0 0.0 +1.0 ns

t

ORISE

输出 上升 时间

[17, 18]

0.15 1.0 1.5 0.5 2.0 3.0 ns

t

OFALL

输出 下降 时间

[17, 18]

0.15 1.0 1.5 0.5 2.0 3.0 ns

t

锁

pll 锁 时间

[19]

0.5 0.5 ms

t

JR

循环-至-循环 输出 jitter 顶峰 至 顶峰

[8]

200 200 ps

RMS

[8]

25 25 ps

注释:

7. 测试 度量 水平 为 这 cy7b9910 是 ttl 水平 (1.5v 至 1.5v). 测试 度量 水平 为 这 cy7b9920 是 cmos levels (v

CC

/2 至 v

CC

/2). 测试

情况 假设 信号 转变 时间 的 2ns 或者 较少 和 输出 加载 作 显示 在 这 交流 测试 负载 和 波形 除非否则 指定.

8. 有保证的 用 statistical correlation. 测试 initially 和 之后 任何 设计 或者 process改变 那 将 影响 这些 参数.

9. 为 所有 三-状态 输入, 高 indicates 一个 连接 至 v

CC

, 低 indicates 一个 连接 至 地, 和 mid indicates 一个 打开 连接. 内部的 末端 电路系统

holds 一个 unconnected 输入 至 v

CC

/2.

10. 这 水平的 至 是 设置 在 fs 是 决定 用 这 “normal” 运行 频率 (f

NOM

) 的 这 vco

(看 逻辑 块 图解). 这 频率 appearing 在 这 ref 和

fb 输入 will 是 f

NOM

当 这 输出 连接 至 fb 是 undivided. 这 频率 的 这 ref 和 fb 输入 will 是 f

NOM

/x

当 这 设备 是 配置 为 一个 频率

multiplication 用 使用 外部 分隔 在 这 反馈 path 的 值 x.

11. 当 这 fs 管脚 是 选择 高, 这 ref 输入 必须 不 转变 在之上电源-向上 直到 v

CC

有 reached 4.3v.

12. 除了 作 指出, 所有 cy7b9920–2 和 –5定时 para计量表 是 指定 至 80-mhz 和 一个 30-pf加载.

13. t

SKEW

是 定义 作 这 时间 在 这 earliest 和 这 最新的 输出 转变 among 所有 输出 当 所有 是 承载 和 50 pf和 terminated 和 50

Ω

至

2.06v (cy7b9910) 或者 v

CC

/2 (cy7b9920).

14. t

SKEW

是 定义 作 这 skew 在 输出.

15. t

DEV

是 这 输出-至-输出 skew 在 任何 二 输出 在 独立的 设备 运行 下面 这 一样 情况 (v

CC

, 包围的 温度, 空气 流动, 等.).

16. t

ODCV

是 这 背离 的 这 输出 从 一个 50% 职责 循环.

17. 指定 和 输出 承载 和 30 pf 为 这 cy7b99x0–2 和 –5 设备 和 50 pf 为 这 cy7b99x0–7设备. 设备 是 terminated 通过 50

Ω

至 2.06v (cy7b9910) 或者 v

CC

/2 (cy7b9920).

18. t

ORISE

和 t

OFALL

量过的 在 0.8v 和 2.0v 为 这 cy7b9910 或者 0.8v

CC

和 0.2v

CC

为 这 cy7b9920.

19. t

锁

是 这 时间 那 是 必需的 在之前 同步 是 达到. 这个 规格 是 有效的 仅有的 之后 v

CC

是 稳固的 和 在里面 正常的 运行 限制. 这个 参数 是

量过的 从 这 应用 的 一个 新 信号 或者 频率 在 ref 或者 fb 直到 t

PD

是 在里面 指定 限制.